一、Zynq开发流程

二、软件安装

三、软件使用

字体大小修改:Setting、Font

四、Vivado基本开发流程

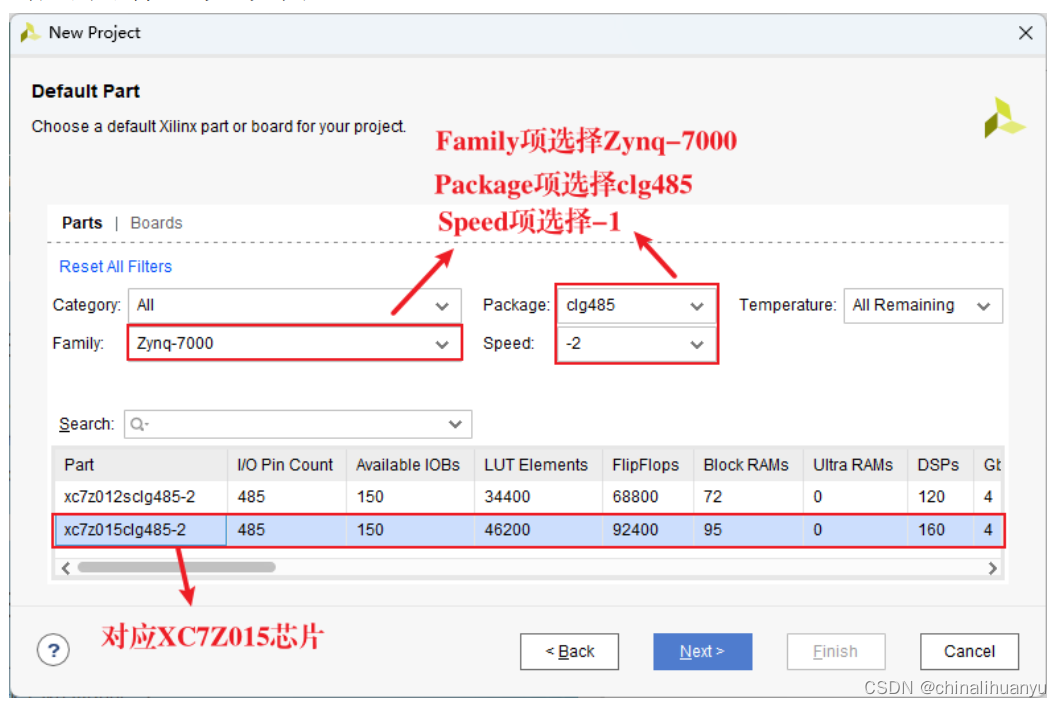

1、创建工程

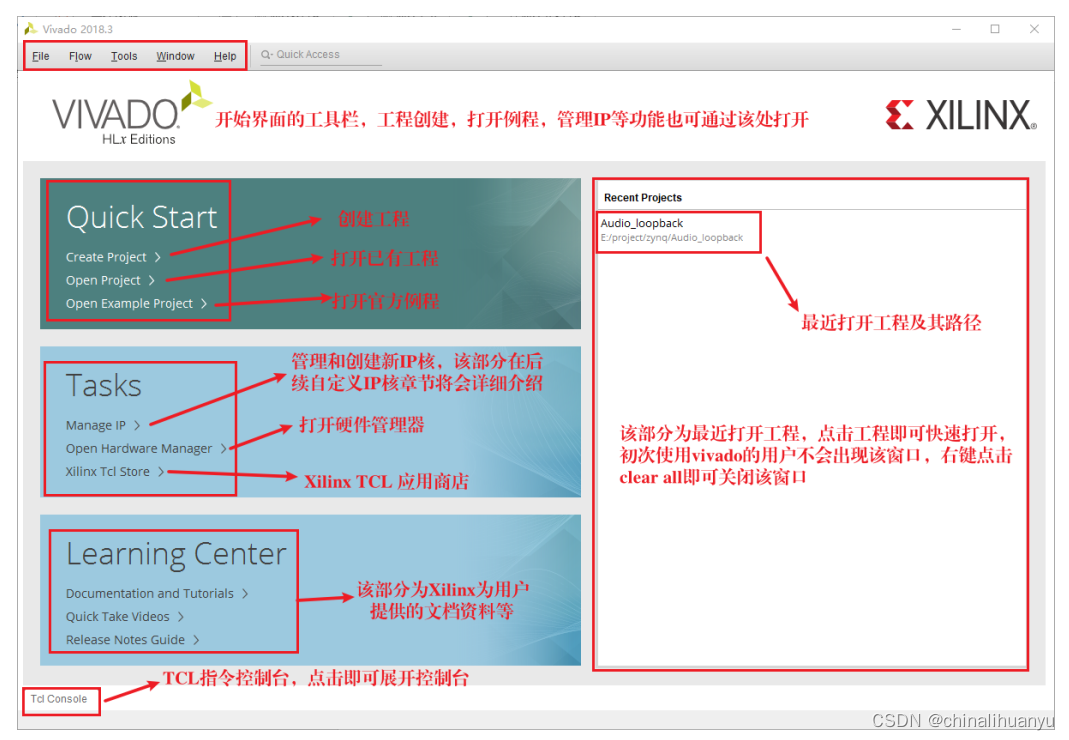

- Quick Start 组包含有 Create Project(创建工程)、 Open Project(打开工程)、 Open Example Project(打开实例工程)。

- Tasks 组包含有 Manage IP(管理 IP)、 Open Hardware Manager(打开硬件管理器)、 Xilinx Tcl Store( Tcl 脚本存储库)。

- Learning Center 组包含有 Documentation and Tutorials(文档和教程)、 Quick Take Videos(快速上手视频)、 Release Notes Guide(发布注释向导)。

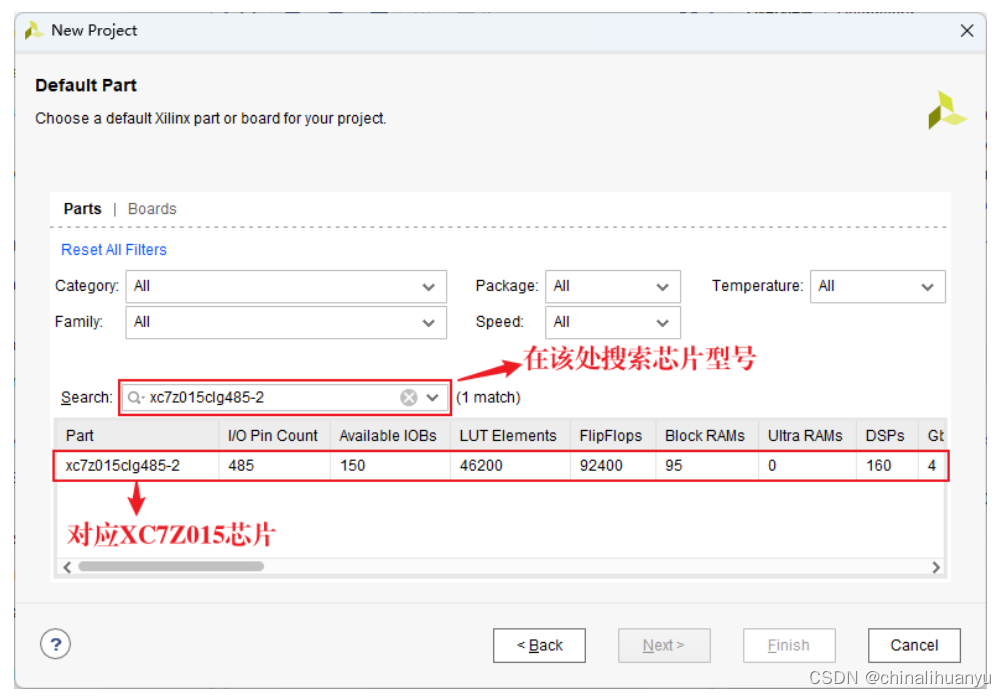

xc 代表 Xilinx 公司, 7z 代表是 7 系列 Zynq 芯片, 015 为芯片编号,clg 代表封装工艺, 485 代表封装的引脚个数为 485 个, -2 代表芯片速度等级为2。

对于软件的各个功能,只需将光标放在对应功能选项上,便会在左下角出现相应的说明。

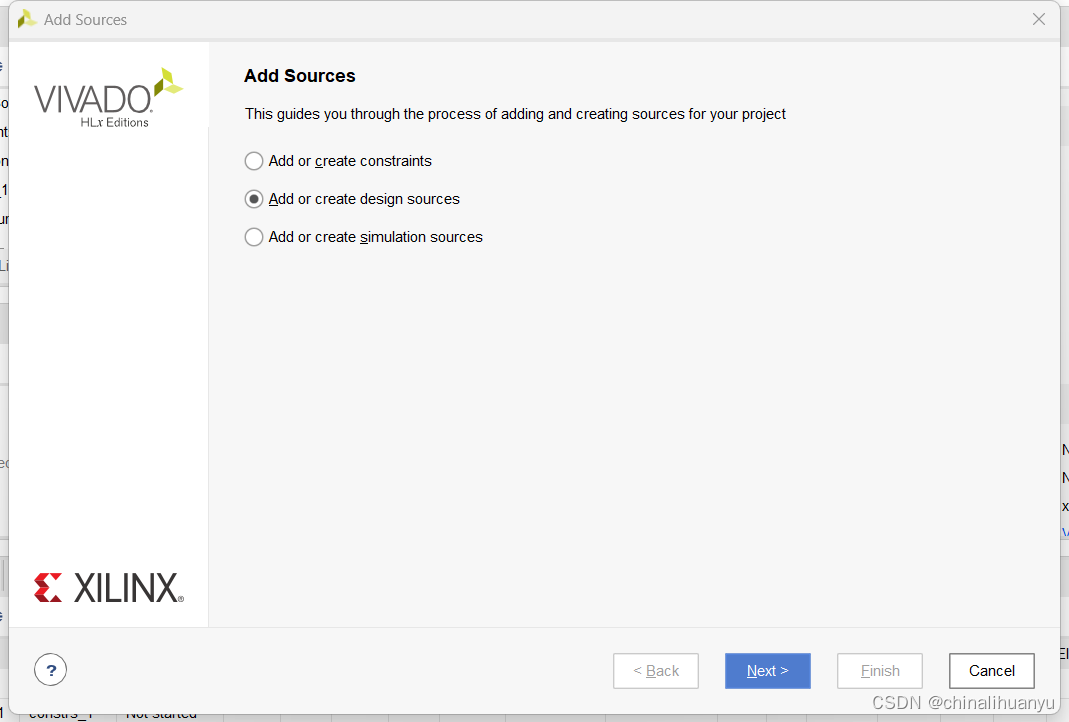

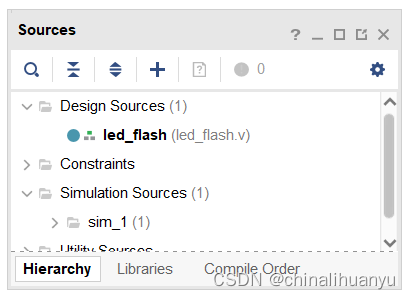

2、添加源文件

(1)在 Flow Navigator 下,找到 Project Manager 并展开,单击 ProjectManager 下的 Add Sources 选项;或者在 Sources 面板下单击 按钮。

(2)Add or Create Constraints(添加或者创建约束);Add or Create Design Sources(添加或者创建设计源文件);Add or Create Simulation Sources(添加或者创建仿真文件);

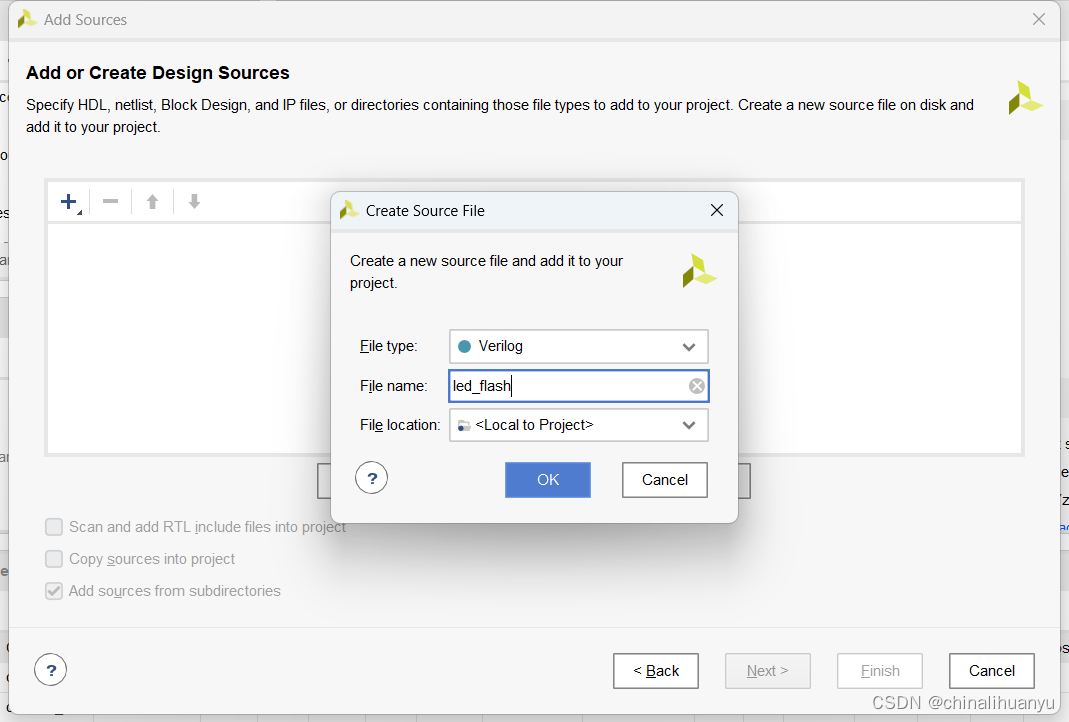

(3)Add Files 来选择添加本地现有的源文件,或单击Create File 按钮来创建一个新的源文件。

(4)在该对话框中选择文件的类型和输入文件的名字。OK->Finish。

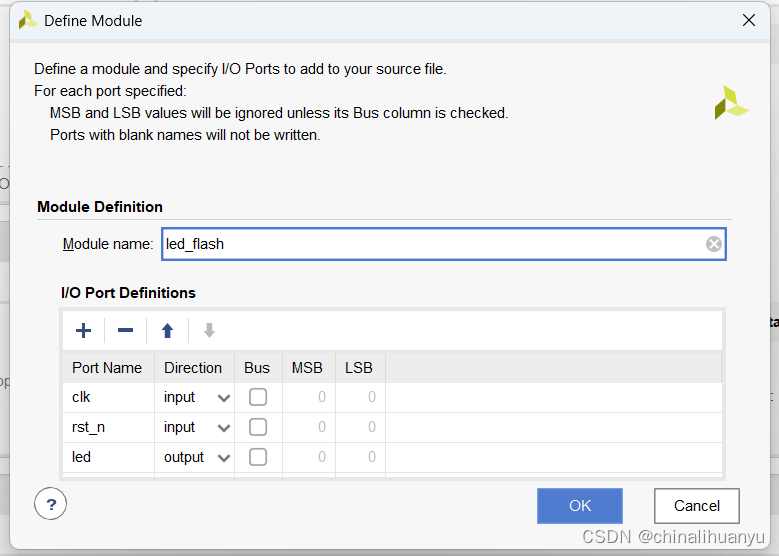

(5)在Define Moudle此处添加设计源文件中的顶层端口信号。OK

(6)添加源文件完成,led_flash.v。双击led_flash.v查看程序。

(7)补全代码

module led_flash(

input clk,

input rst_n,

output reg led

);

reg[25:0] cnt;

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 26'd0;

else if (cnt <= 26'd49_999_999)

cnt <= cnt + 1'd1;

else

cnt <= 26'd0;

end

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

led <= 1'd0;

else if (cnt <= 26'd49_999_999)

led <= ~led;

else

led <= led;

end

endmodule3、RTL描述与分析

Verilog语法错误在编写的过程中会自动检测。RTL 描述与分析功能可以对工程的 RTL结构、语法进行查看,进而可以分析并修正逻辑上的错误。

(1)在 Flow Navigator 下,找到 RTL Analysis,并展开。单击Open Elaborated Design,打开 Elaborated Design。可 以看到 Open Elaborated Design 标题变为 Elaborated Design。等运行完成。

(2)Schematic( RTL 原理图)

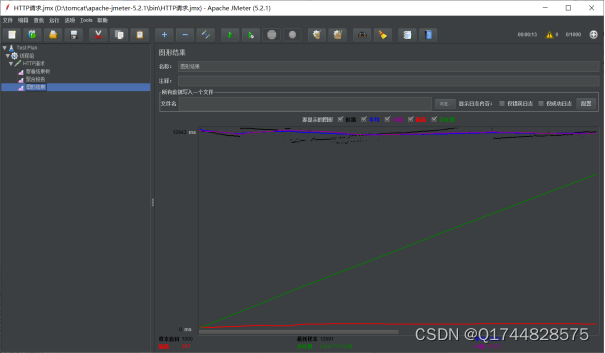

4、激励创建与仿真测试

5、设计综合

(1)在 Flow Navigator 窗口下,找到 Synthesis 并展开。在展开项中,单击 Run Synthesis 开始对设计进行综合。

(2)当综合完成后,出现 Synthesis Completed 对话框。可以选择 Open Synthesis Design 来打开综合后的设计进行观察,单击 OK按钮。

(3)如果之前打开了 Elaborated Design,会出现关闭 Elaborated Design的提示对话框。单击 Yes 按钮即可。

(4)在设计综合完成后的 Synthesis 展开项中工具会列出诸多可以在当前设计下进行的操作。注意在流程向导窗口中 Synthesis下的 Open Synthesized Design 在综合完成并打开设计后变为 Synthesized Design。出来一大堆东西。

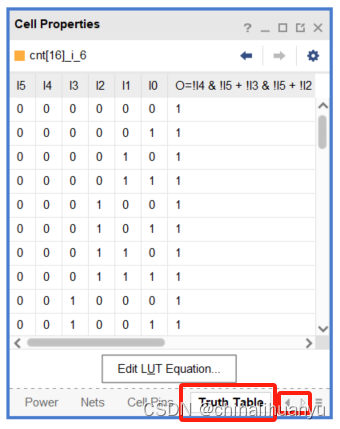

(5)在打开 Synthesis Design 后,默认打开 Schematic 视图,如图所示。如果没有打开,在 Synthesis Design 下单击 Schematic 即可打开。显然,在综合后的原理图视图中,电路网表即采用 FPGA 器件中拥有的基本元件来搭建了,如图中的 LUT6 查找表。

(6)查看 LUT6 的内部映射关系。在原理图窗口内选择 LUT6 对应的 Cell。在 Sources 窗口下方的 Cell Properties 窗口中,选择 Truth Table,可以看到逻辑表达式 O=!I5 + !I0 & !I1 & I5 + !I0 & I1 &I2 & !I4 + !I0 & !I2 & I3 & !I4 以及真值表映射关系。

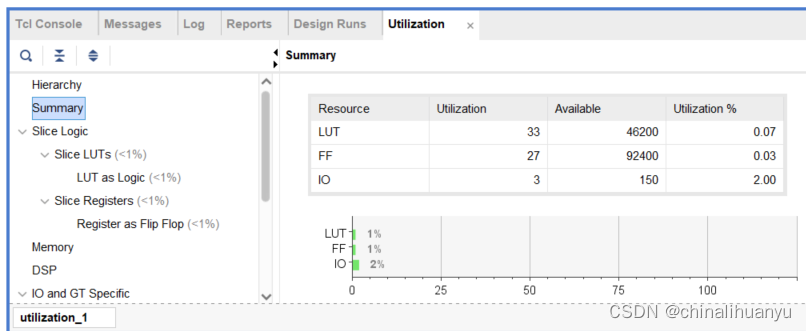

(7)单击 Synthesis Design 下的 Report Utilization 选项。出现 Report Utilization 对话框,如图所示。通过 Report Utilization 功能,我们可以得到工具针对当前设计的资源利用率的详细报告。单击 OK 按钮。 Vivado 开始计算该设计的资源消耗量。

(8)在 Vivado 下方打开了 Utilization-utilization_1 标签窗口。如图所示,给出了该设计的资源利用率:

(9)在查看 Schematic 视图时,不同的阶段,得到的图的体系结构不一定相同,RTL 级别、 Synthesized Design 级别、 Implementation 级别,不一定相同。

6、添加设计约束

FPGA 设计需要在工具中指定对应的 IO 引脚位置以及输入时钟的信息,即需要用户对 IO 进行约

束以及进行时钟周期等时序约束。

(1)在综合完成后的设计上点击 Open Synthesized Design 来打开综合后的设计;在菜单栏视图处下拉 I/O Planning view 点击进入 IO 规划视图界面。

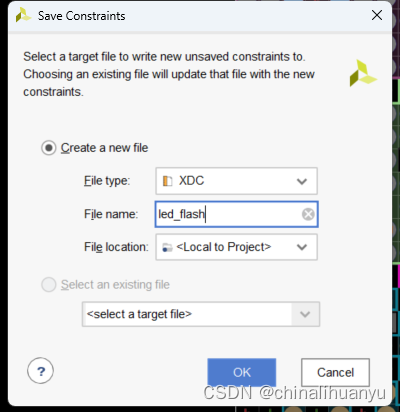

(2)选择之后会进入 IO分配界面, 该界面可用于分配 IO引脚、约束引脚电平、设置驱动强度等等,这里我们需要为设计中的输入输出信号分配 IO 引脚并约束电平。通过原理图查看信号,分配到正确的引脚。左上角保存。

7、设计实现

(1)优化设计 Opt Design : 针对所选器件,对逻辑设计进行优化,以便达到最优实现;

(2)功耗优化设计 Power Opt Design (可选):从降低功耗的角度,对逻辑设计进行优化;

(3)布局设计 Place Design(必选):将设计网表在所选器件上进行布局;

(4)布局后功耗优化 Post-Place Power Opt Design (可选):在布局之后的网表基础上优化功耗;

(5)布局后物理优化 Post-Place Phys Opt Design (可选):在布局之后的网表基础上进行物理优化,主要针对时序性能;

(6)布线设计 Route Design(必选): 在布局后的设计上,进行布线;

(7)布线后物理优化 Post-Route Phys Opt Design (可选):在布线后的设计上,参考布线后的设计延时,对逻辑、布局、布线等情况再次进行优化。

具体步骤:

(1)在 Flow Navigator 下找到并展开 Implementation,如图所示。单击 Run Implementation 选项,开始执行实现过程。

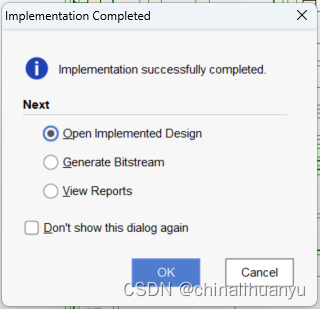

(2)实现过程完成后会出现如图所示的 Implementation Completed 对话框。选择 Open Implemented Design,单击 OK 按钮。

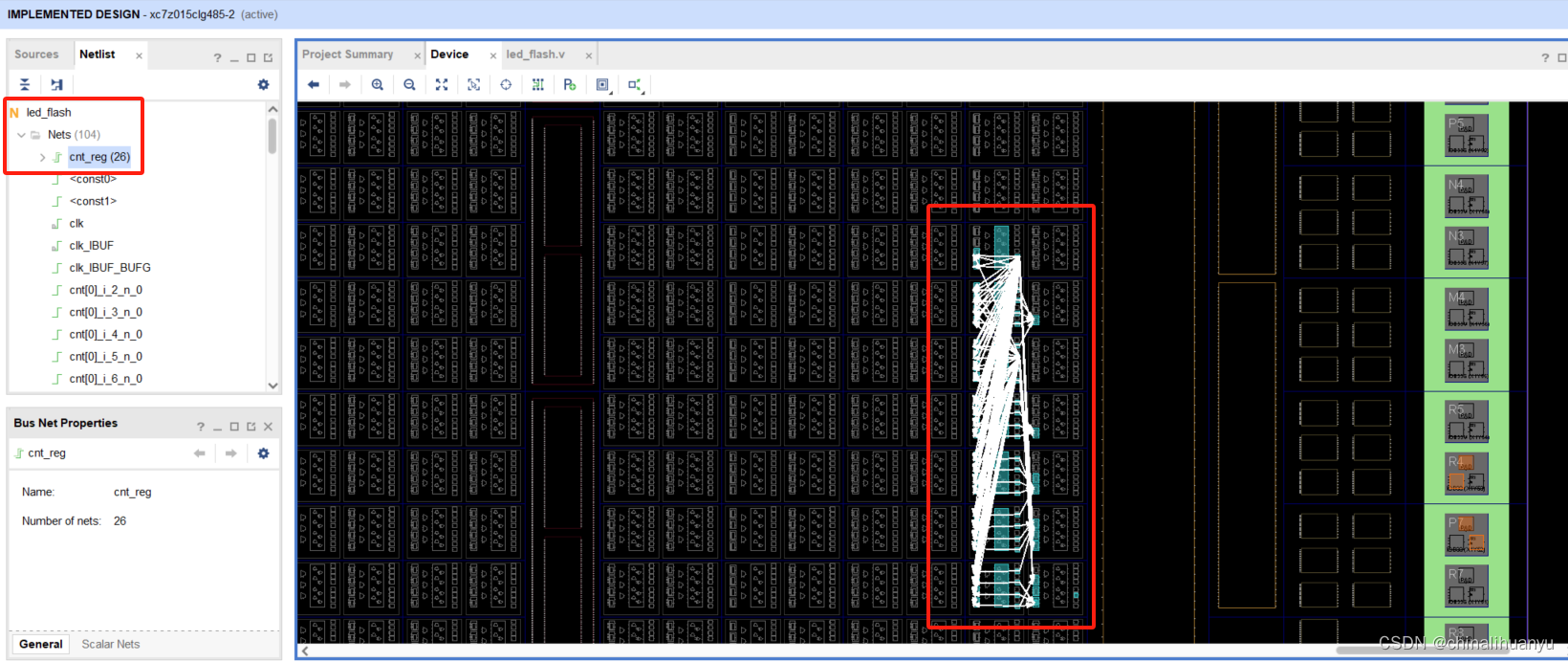

(3)打开 Implemented Design 后, 调整结构图,可以清晰地看到该设计用到的器件和器件之间的连线(即布线)。

8、生成比特流文件

设计的最后一步是将 Vivado 实现产生的网表文件转化为比特流文件,并且将比特流文件下载到 FPGA 芯片中。比特流文件用于完成对 FPGA 进行配置。

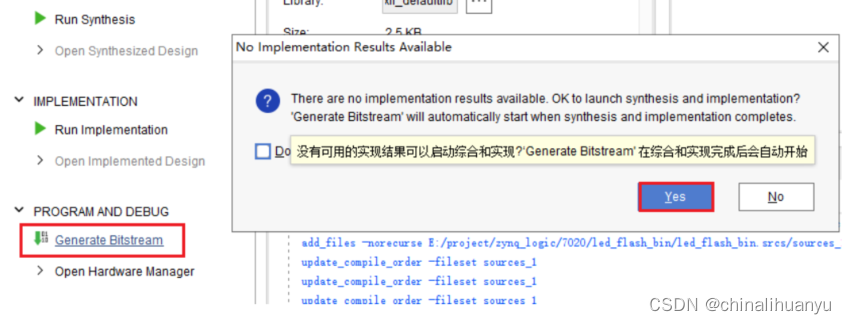

(1)在 Flow Navigator 窗口下找到 Program and Debug 选项并展开。单击 Generate Bitstream 选项,开始生成比特流文件。

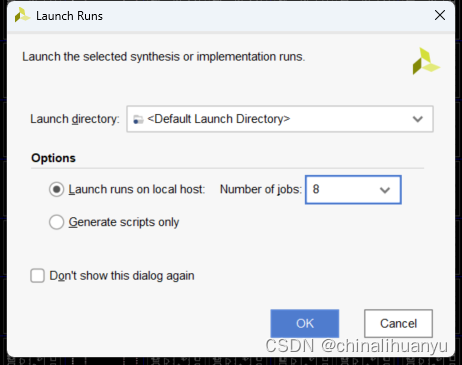

(2)随后软件会出现弹窗提醒运行综合和实现,这里需要选择在本地主机上运行,同时建议将 jobs 设置为最大值,这样能最快的运行完成。

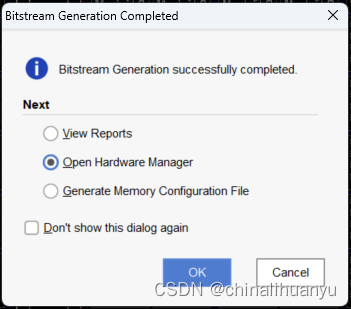

(3)随后等待 bit 文件生成完成,软件会出现如图所示的 Bitstream GenerationCompleted 对话框,选择 Open Hardware Manager 选项。单击 OK 按钮。

(4)软件会为我们打开 Hardware Manager 界面,该界面用于烧录和调试。如果没有打开该界面,则单击 Open Hardware Manager 打开 Hardware Manager。Vivado 右上侧出现 Hardware Manager 界面。

9、硬件连接与烧录

连接USB Type-C和电源线。拨动电源开关到 ON 侧。

(1)在 Hardware Manager 界面中,单击 AutoConnect 连接设备。 如果 Auto Connect 无法连接,则需要检查开发板是否上电或驱动是否安装成功。

(2)Auto Connect 后软件会自动检测并连接器件。

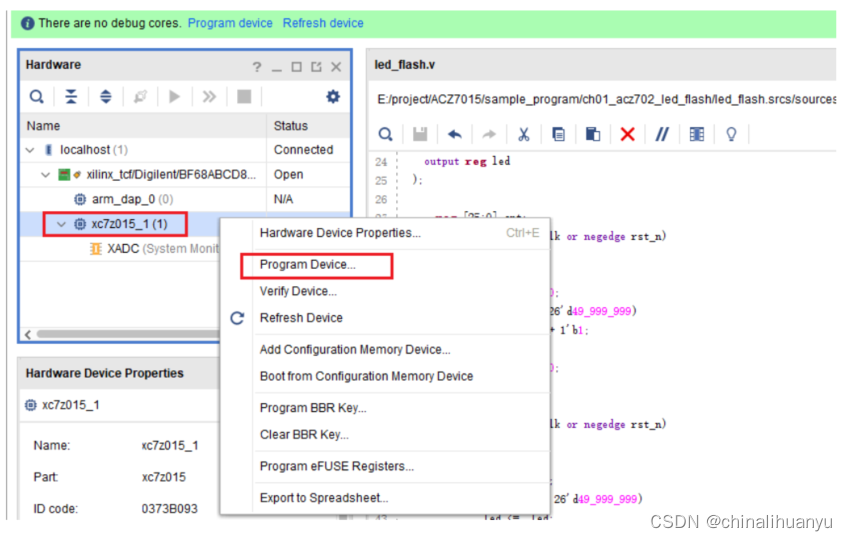

(3)在 Hardware Manager 界面中找到并右键单击 xc7z015_1( 1),在浮动菜单中单击Program Device…选项。

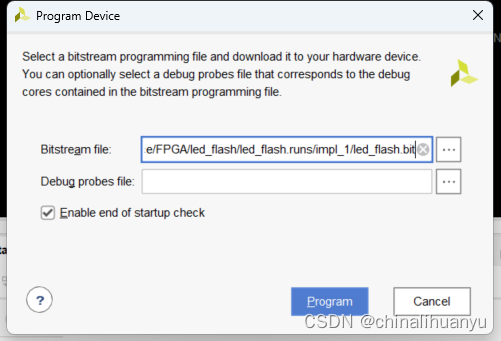

(4)出现 Program Device 对话框。默认情况下比特流文件会自动选中,如果没有单击“…”按钮,找到并选中 led_flash.bit 文件。在 Program Device 对话框中单击 Program 按钮,开始烧录。

(5)观察上板现象,通过观察 LED D0是否按照预期的,每秒进行一次翻转,验证设计是否正确。

10、逻辑程序固化

程序固化就是将程序烧录到非易失性存储器(如 QSPI Flash、 NAND Flash等)上,这样即使开发板断电后,程序也不会丢失。

ZYNQ-7000 系列器件,由于芯片并未向 PL 端提供控制非易失性存储器件的引脚,用户只能使用 SDK 软件通过 PS 端进行固化。

五、硬件调试:ILA的使用

六、Vivado Simulator仿真软件的使用

七、Zynq程序固化

合成BOOT.bin文件

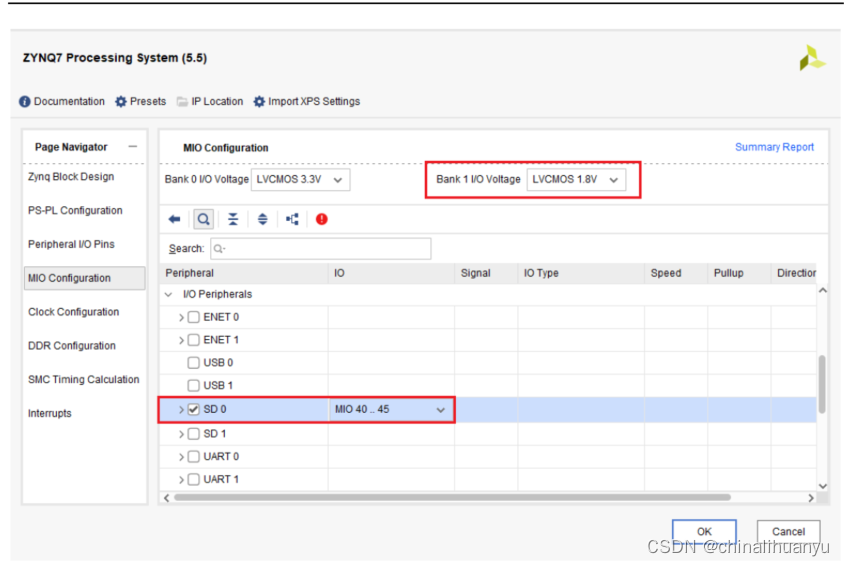

1.在你工程的Zynq IP核中,使能QSPI或SD。

2.Generate Bitstream。

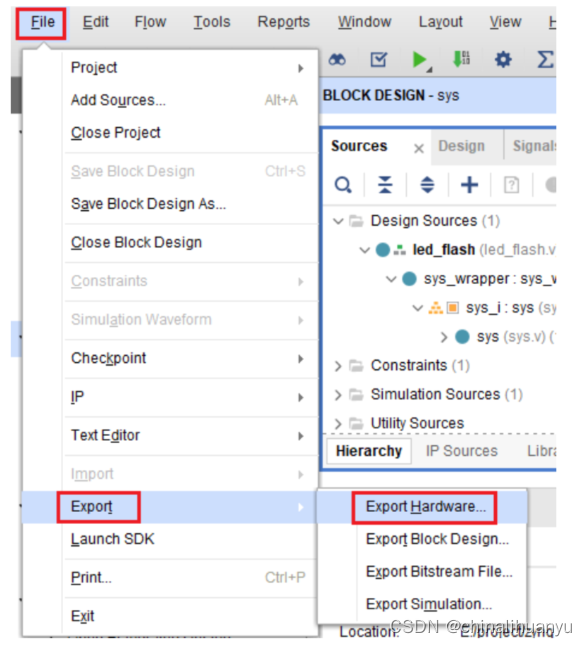

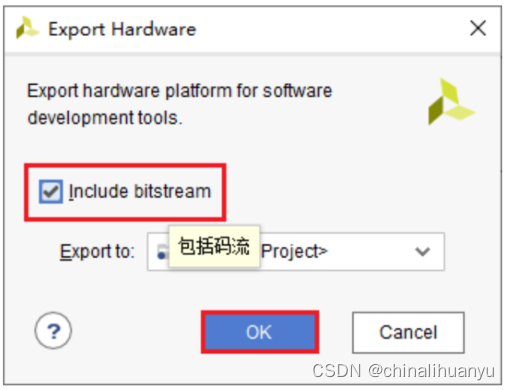

3.导出硬件。

4.运行SDK,保持默认,OK。

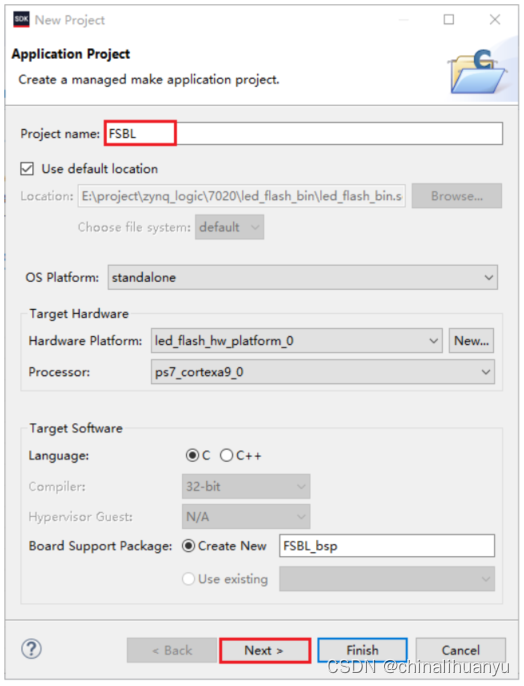

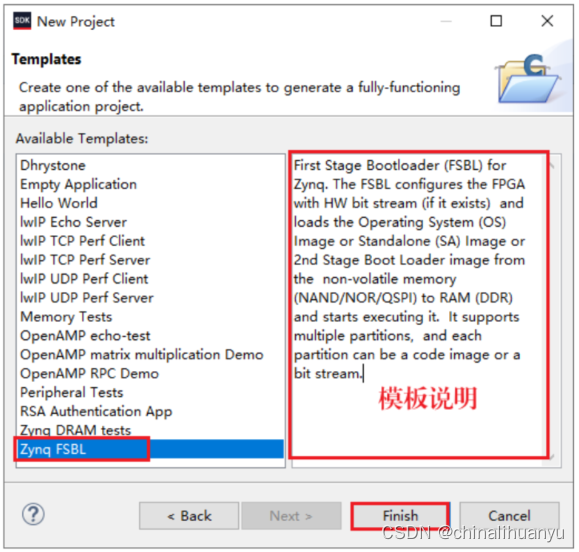

5.生成FSBL.elf。

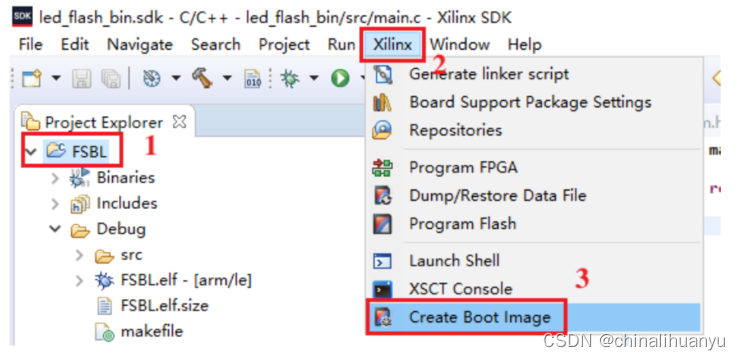

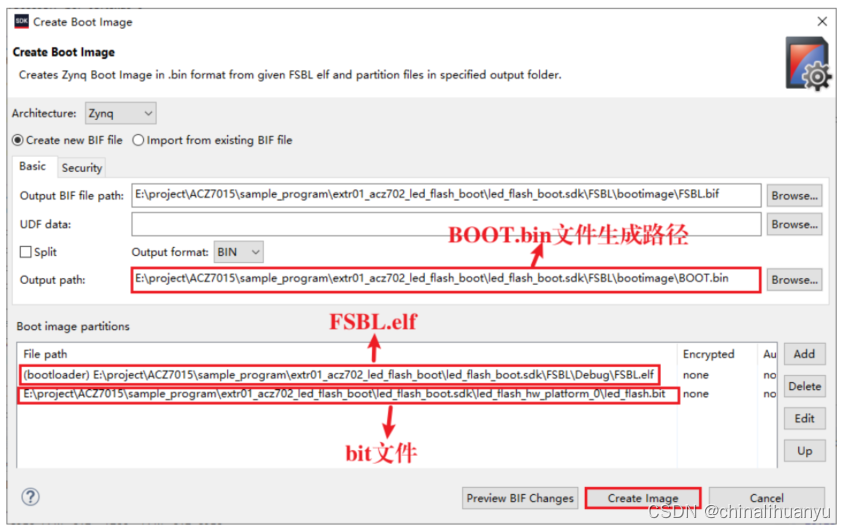

6.生成BOOT.bin文件:点一下FSBL。

第一种:固化到QSPI Flash。

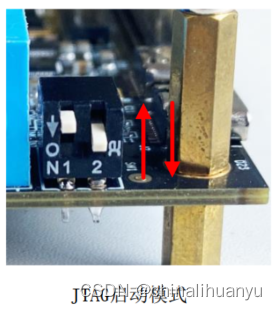

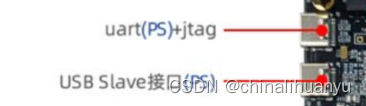

1.确保开发板启动模式为JTAG模式,使用Type-C线连接调试接口(右侧)。

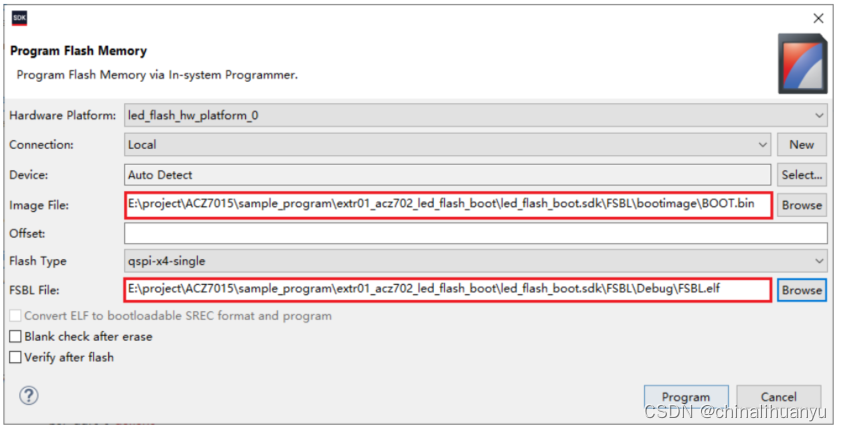

2.在SDK界面,点击Xilinx,选择Program Flash。

3.把BOOT.bin和FSBL.elf放进去,点击Program。

4.开发板断电,启动模式改为QSPI模式。完成。

如果失败请检查IP核QSPI设置、生成的文件、操作是否有问题。

第二种:固化到SD卡。

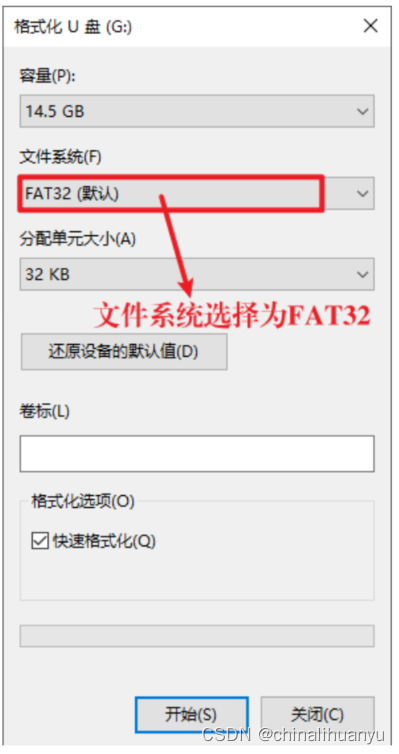

1.准备SD卡,和读卡器。将SD插入读卡器,插入电脑USB口中。接着将SD卡格式化(其他资料请自行保存)为FAT32格式。

2.格式化之后将生成的BOOT.bin文件拷贝到SD卡根目录上。弹出读卡器,拔下SD卡。

3.将SD卡正确安装到开发板上。

4.开发板断电,切换到SD卡启动模式,开发板上电。

如果失败请检查IP核SD设置、生成的文件、操作是否有问题。

常见问题:

【Zynq】按键控制led固化实验失败及解决办法 - ACZ702开发板 - 芯路恒电子技术论坛 - Powered by Discuz! (corecourse.cn)

【Zynq】非原工程路径导致的zynq程序固化失败解决办法 - ACZ702开发板 - 芯路恒电子技术论坛 - Powered by Discuz! (corecourse.cn)