1.简介

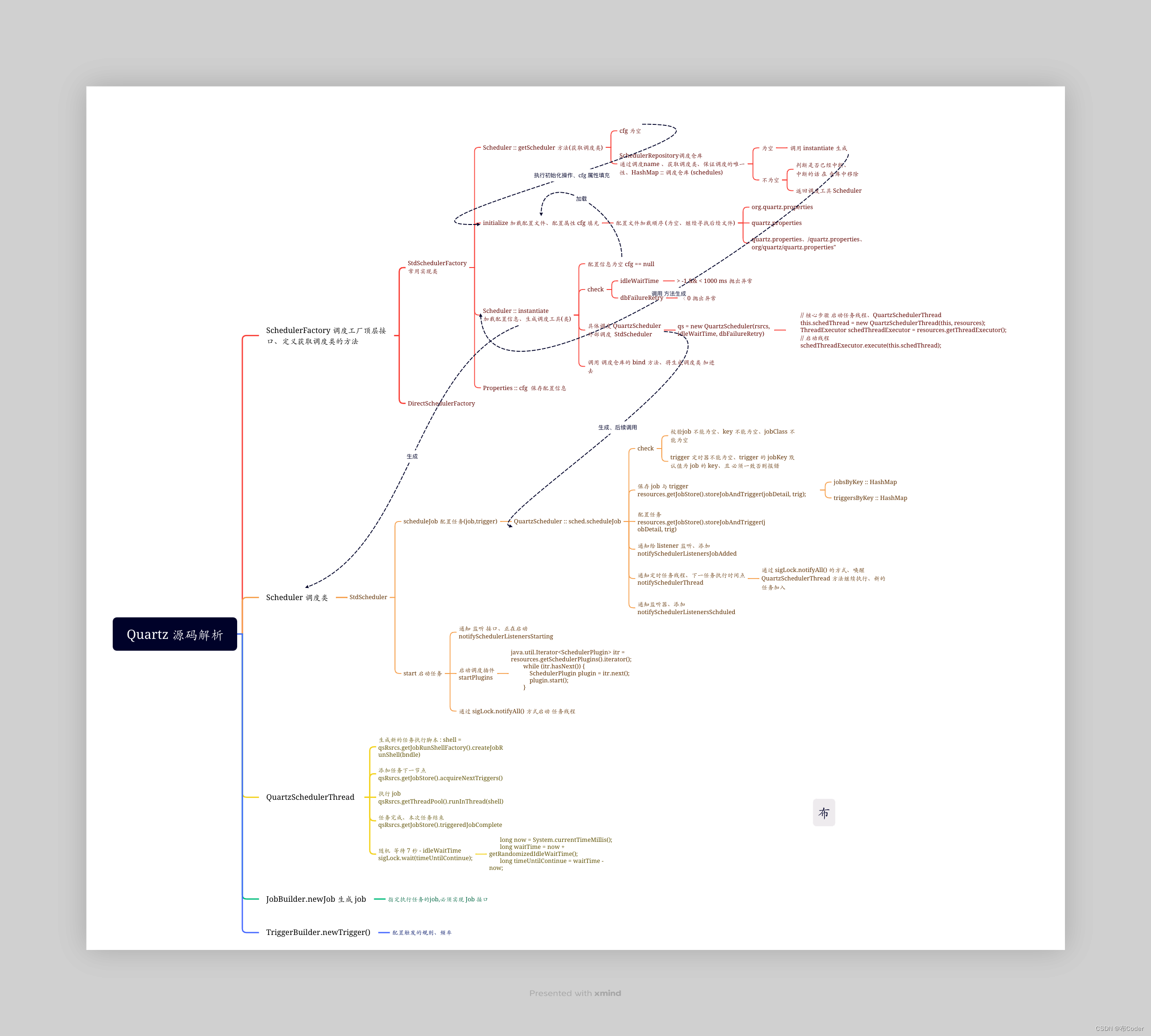

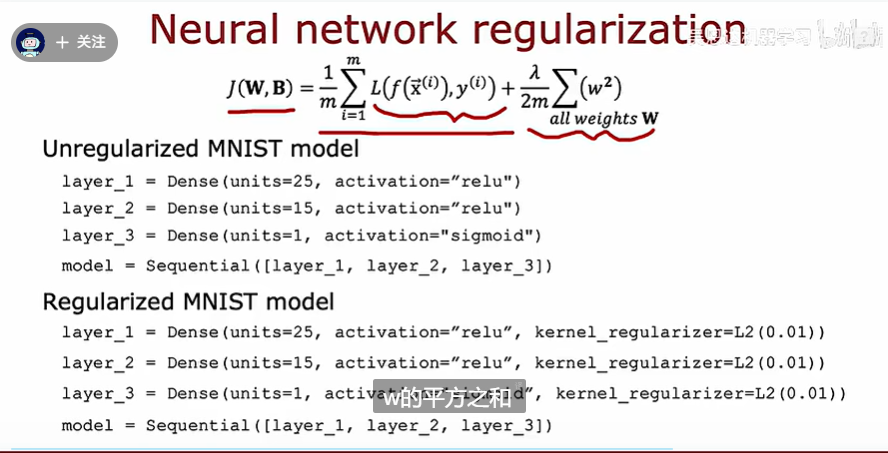

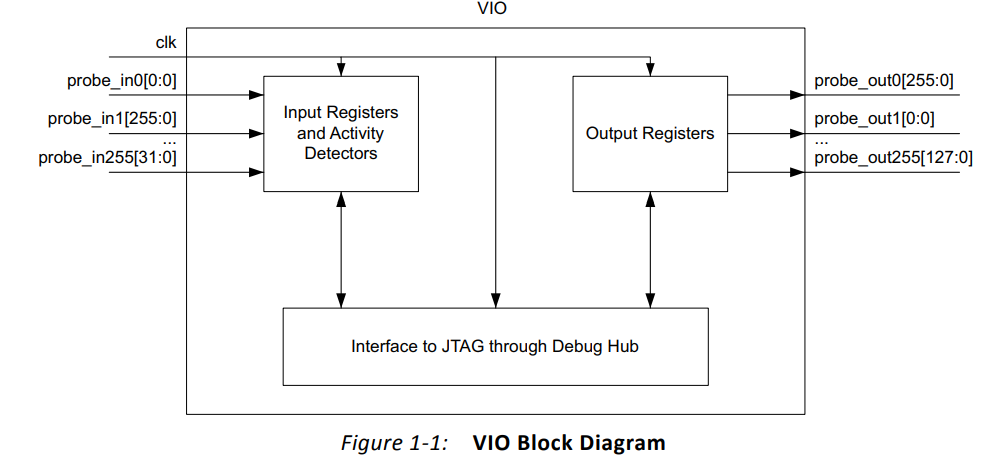

VIO(Virtual Input/Output)IP核是一种用于FPGA设计的IP核,它可以模拟输入/输出设备的功能,如键盘、鼠标、显示器等。VIO IP核可以在FPGA设计中用于调试和验证,帮助工程师快速定位问题并进行调试。如图所示,VIO通过JTAG接口与芯片内部互换信息,其中output指VIO IP的输出对于FPGA内部逻辑是输入信号。Input指VIO IP的输入对于FPGA内部逻辑是输出信号,用来监测信号变化,与ILA相比,VIO无需占用ram资源。

2.使用场景

调试:VIO IP核可以模拟输入设备的信号,帮助工程师验证设计的正确性,快速定位问题并进行调试。验证:VIO IP核可以用于验证设计的功能是否符合预期,提高设计的可靠性和稳定性。监控:VIO IP核可以监控设计中的信号变化,帮助工程师了解设计的工作状态。

3.调试技巧

- 使用VIO IP核连接到设计中的信号,观察信号的变化和波形。

- 设置断点和触发条件,可以在特定条件下暂停设计的运行,方便调试。

- 使用VIO IP核的时钟控制功能,可以控制信号的采样速率,帮助调试设计中的时序问题。

- 结合其他调试工具如逻辑分析仪、仿真工具等,可以更加全面地进行调试。

总之,通过VIO IP核的使用,工程师可以更加高效地进行FPGA设计的调试和验证工作。

4.快速使用

创建一个场景是多路选择器,输入不同的2bit值,输出不同的8bit的值,实现多选一的功能,场景中通过VIO output通道向程序输入2bit值,同时通过VIO input通道检测程序的输出值。

代码如下:

module vio_top(

input sys_clk_p,

input sys_clk_n//200M

);

wire sys_clk;

wire [1:0] mux_sel;

reg [7:0] mux_val;

localparam O1 = 8'd1;

localparam O2 = 8'd2;

localparam O3 = 8'haa;

localparam O4 = 8'hee;

//clk差分转单端

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(sys_clk), // Buffer output

.I(sys_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(sys_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

//多路选择器

always @(*) begin

case(mux_sel)

2'b00: mux_val = O1;

2'b01: mux_val = O2;

2'b10: mux_val = O3;

2'b11: mux_val = O4;

default: mux_val = 8'bx; // 'x'表示不确定值,用于表示非法选择

endcase

end

//VIO

vio_0 vio_instance (

.clk(sys_clk), // input wire clk

.probe_in0(mux_val), // input wire [7 : 0] probe_in0

.probe_out0(mux_sel) // output wire [1 : 0] probe_out0

);

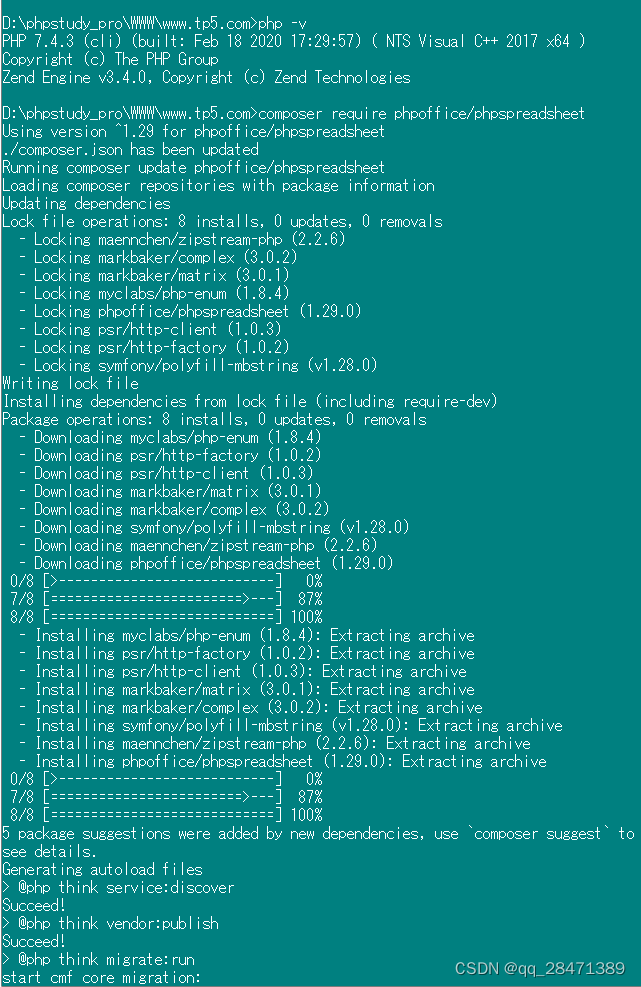

endmoduleIP配置如下:可在输出页配置输出信号的默认值,当前为0。

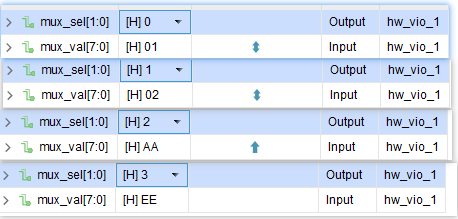

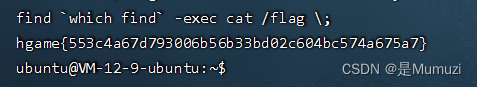

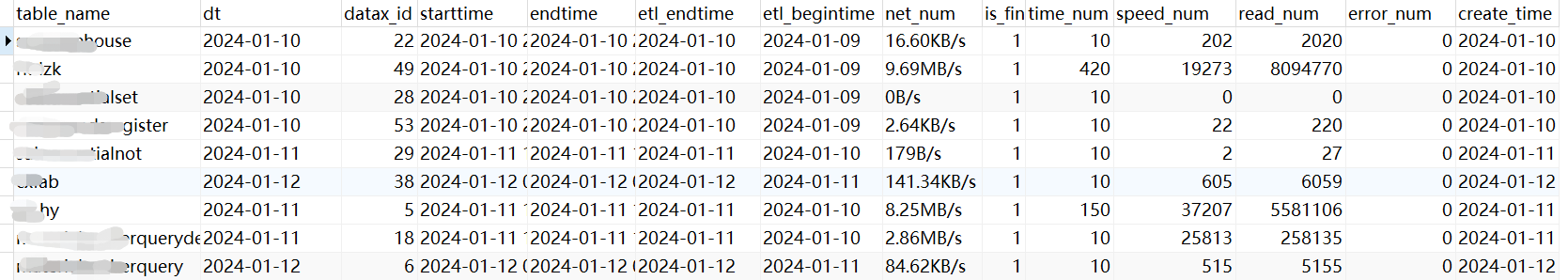

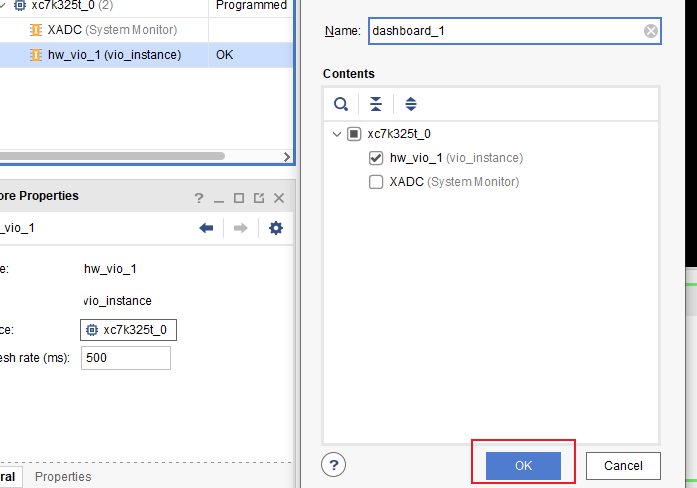

结果如下:双击vio ip显示dashboard信息

可以看到输入不同的数,input端将检测到不同的结果