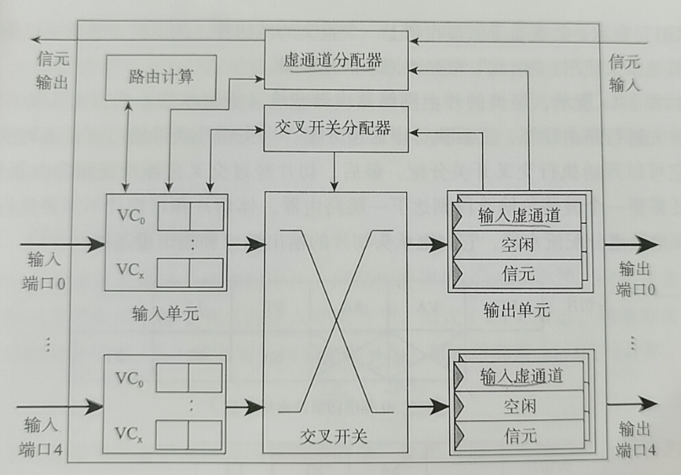

POCV/SOCV的时序报告中有如下变量:

-

Mean: 高斯分布中的μ值(平均值)

-

Sensit: sensitivity,也就是1个Sigma的值;

-

Corner: Sigma边界的最差值

cell的delay = Delay mean + N * Delay sigma;

cell 的Transition = Slew mean + N * Slew sigma;

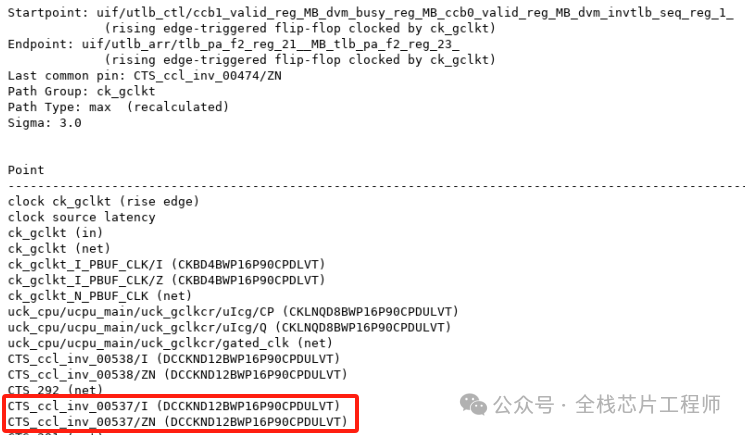

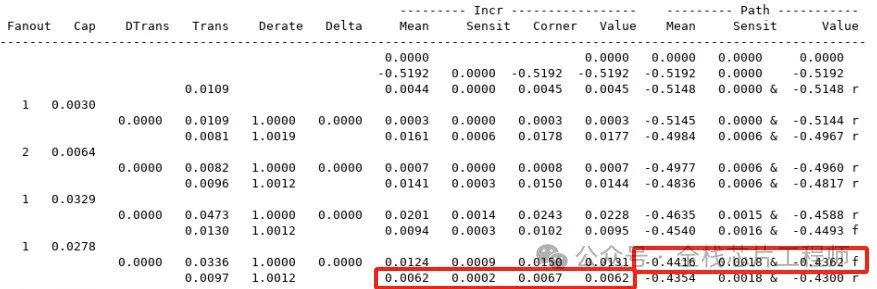

以2.5GHz, 12nm, DVFS, A72数字后端训练营项目为例,下图列出了mean跟sigma值的时序报告:

我们把图放大如下:

incr mean = 0.0062;

incr sigma = 0.0002;

到CTS_ccl_inv_00537/I的pre-Arrival Mean = -0.4416;

则到CTS_ccl_inv_00537/ZN的Arrival mean= -0.4416+0.0062 = -0.4354;

到CTS_ccl_inv_0537/I的Pre-Arrival Sigma= 0.0018;

则到CTS_ccl_inv_0537/ZN的Arrival sigma= sqr (0.0018 ^ 2 + 0.0002 ^ 2)= 0.0018;

所以可得,到CTS_ccl_inv_0537/ZN的Arrival delay 为:

Arrival delay = Arrival mean + N * Arrival sigma = -0.4354 + 3*0.0018 = -0.4300

“ 12nm工艺,2.5GHz频率,DVFS低功耗A72后端培训”

01

12nm Cortex-A72后端实战

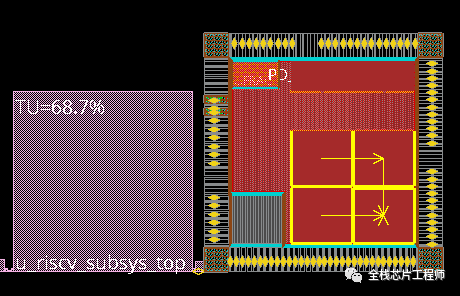

本项目是真实项目实战培训,低功耗UPF设计,后端参数如下:

工艺:12nm

频率:2.5GHz

资源:2000_0000 instances

低功耗:DVFS

为了满足广大学员的诉求,我们将12nm A72 TOP课程分为两个版本:

1、基础版(价格是知名机构的1/5,全国最低价)

2、进阶版(低功耗、hierarchy UPF、Stampling)!业界最先进技术!

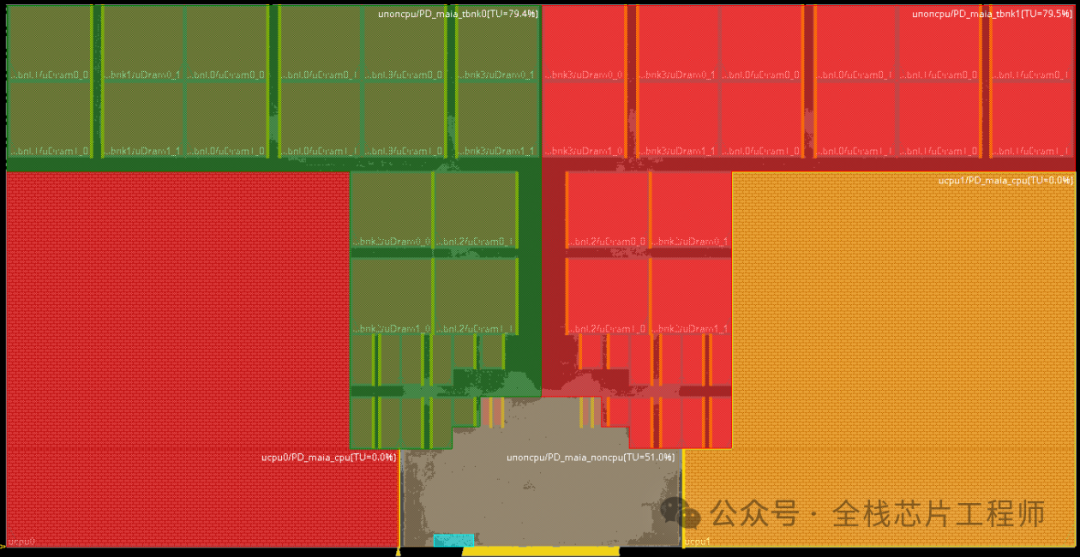

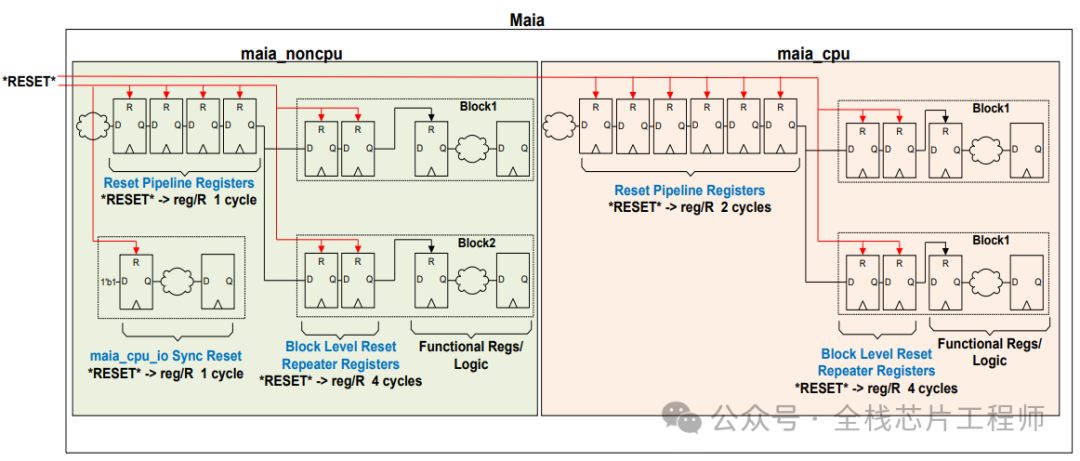

进阶版本的低功耗设计如下:7个power domain

Stampling打起来真是高级手工艺术,全网唯一:

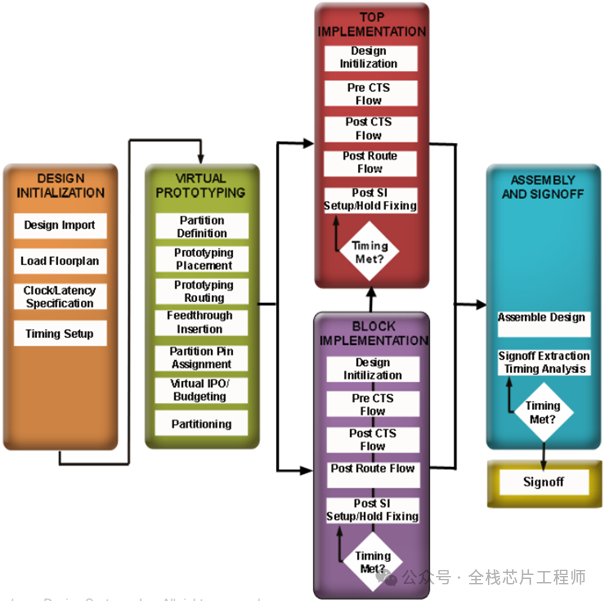

Flow:Partition Flow

时钟结构分析:

复位结构分析:

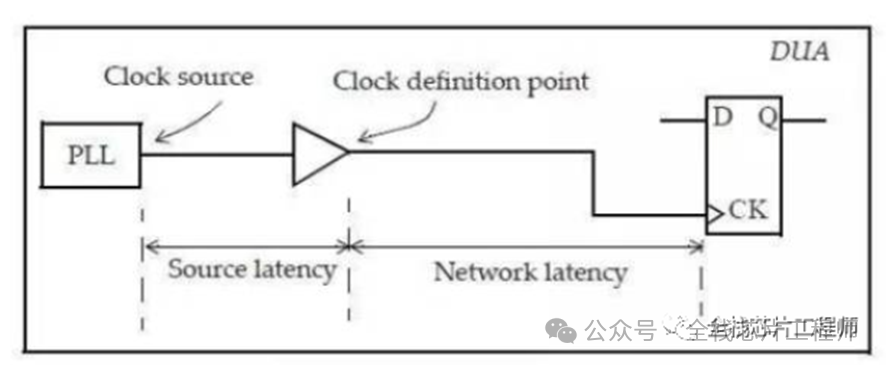

12nm 2.5GHz的A72实战训练营需要特别设置Latency,TOP结构如下,参加过景芯SoC全流程训练营的同学都知道CRG部分我们会手动例化ICG来控制时钟,具体实现参见40nm景芯SoC全流程训练项目,本文介绍下12nm 2.5GHz的A72实战训练营的Latency背景,欢迎加入实战。

时钟传播延迟Latency,通常也被称为插入延迟(insertion delay)。它可以分为两个部分,时钟源插入延迟(source latency)和时钟网络延迟(Network latency)。

大部分训练营同学表示平时都直接将Latency设置为0了,那latency值有什么用呢?其实这相当于一个target值,CTS的engine会根据你设置的latency值来插入buffer来实现你的latency target值。

下图分为1st Level ICG和2nd Level ICG,请问这些ICG为什么要分为两层?

请问,为什么不全部把Latency设置为0?2nd Level ICG的latency应该设置为多少呢?

latency大小直接影响clock skew的计算。时钟树是以平衡为目的,假设对一个root和sink设置了400ps的latency值,那么对另外的sink而言,就算没有给定latency值,CTS为了得到较小的skew,也会将另外的sink做成400ps的latency。请问,为何要做短时钟树?因为过大的latency值会受到OCV和PVT等因素的影响较大,并有time derate的存在。

02

28nm Cortex-A7后端实战

此外,我们提供全国最低价的28nm A7后端设计,价格惊喜!打垮动辄1.5w-2.5w的后端培训价格!

我们再来对比下A72与A7的资源。A72 Gate数目是A7的13倍!如果都采用28nm制程,A72的面积应该是1180790um^2,实际A72采用12nm制程面积是486100um^2,1180790/486100=2.4,符合摩尔定律。

Cortex-A7单核:

Gates=240291 Cells=118421

Cortex-A72单核:

Gates=3125649 Cells=1207766

28nm Cortex-A7单核:

Area=90830.1 um^2

12nm Cortex-A72单核:

Area=486100.9 um^2

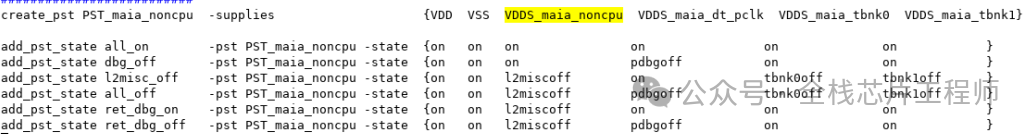

28nm A7后端设计课程采用的全国最低价格来推广,本文不做过多介绍,本文重点介绍下先进的12nm A72进阶版本课程。分享个例子,比如,Cortex-A72低功耗设计,DBG domain的isolation为何用VDDS_maia_noncpu供电而不是TOP的VDD?

答:因为dbg的上一级是noncpu,noncpu下面分成dbg和两个tbnk。

再分享个例子,比如,Cortex-A72低功耗设计,这个switch cell是双开关吗?答:不是,之所以分trickle和hammer,是为了解决hash current大电流,先开trickle,然后再开hammer。

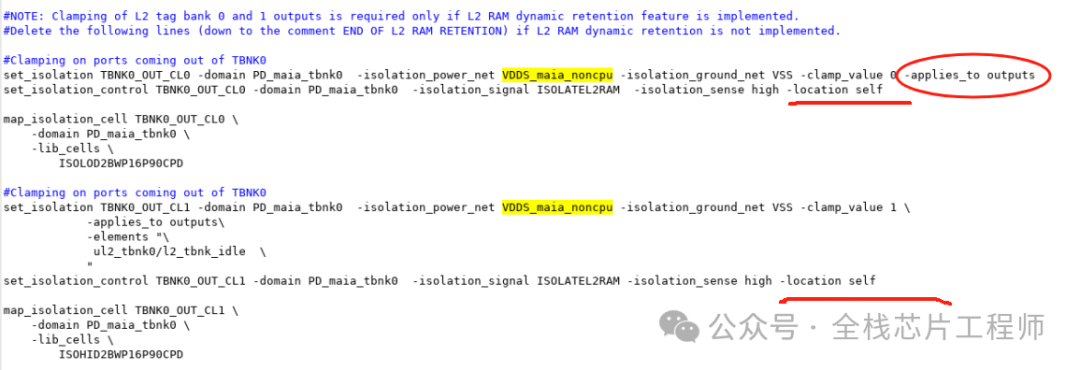

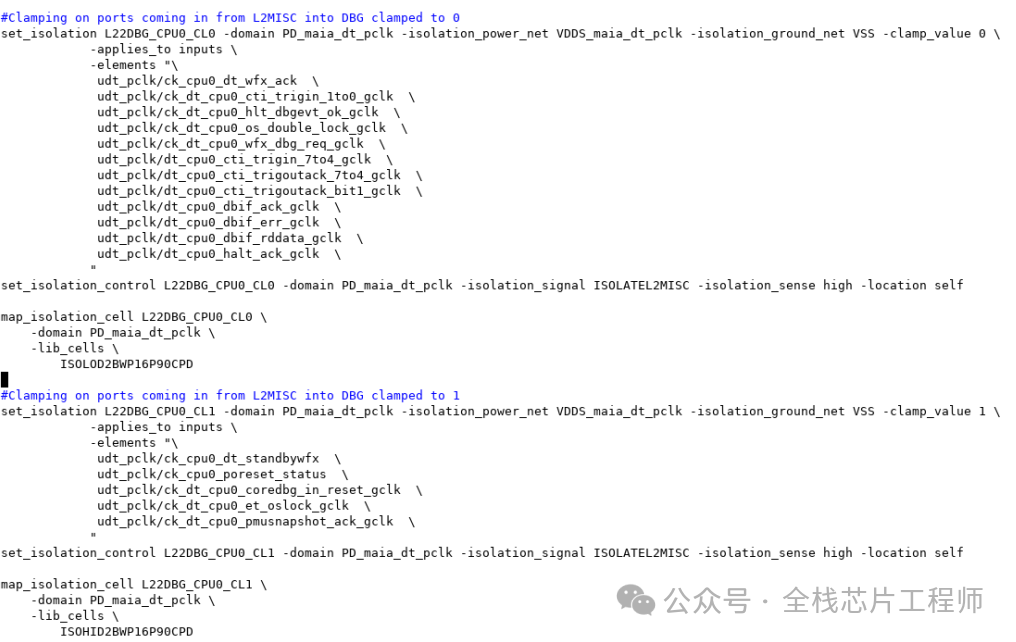

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:请问,如果iso cell输出都要放parent,输入放self,那么下面-applies_to_outputs对应的-location为何是self?

答:这个需要了解CPU的内部设计架构,tbnk掉电 VDDS_maia_noncpu也必然掉电,pst如下,所以-applies_to_outputs对应的-location是可以的,那么注意下debug domain呢?

实际上,没有tbnk到debug domain的信号,因此脚本如下:

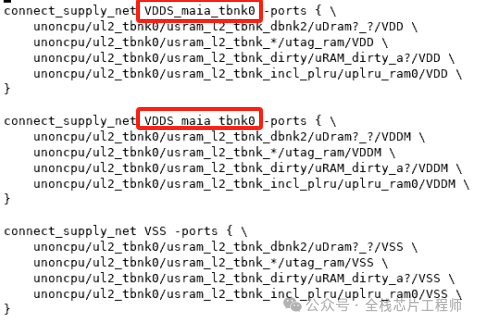

再分享个例子,比如,Cortex-A72进阶版本课程的低功耗例子:为何non_cpu的SRAM的VDD VDDM都接的可关闭电源?SRAM的VDD VDDM分别是常开、和retention电源吧?

答:本来是VDDM作为retention电源设计的,VDD关掉后 VDDM可以供电作为retention使用,但是此处没有去做memory的双电源,sram当成单电源使用,不然sram无法彻底断电。

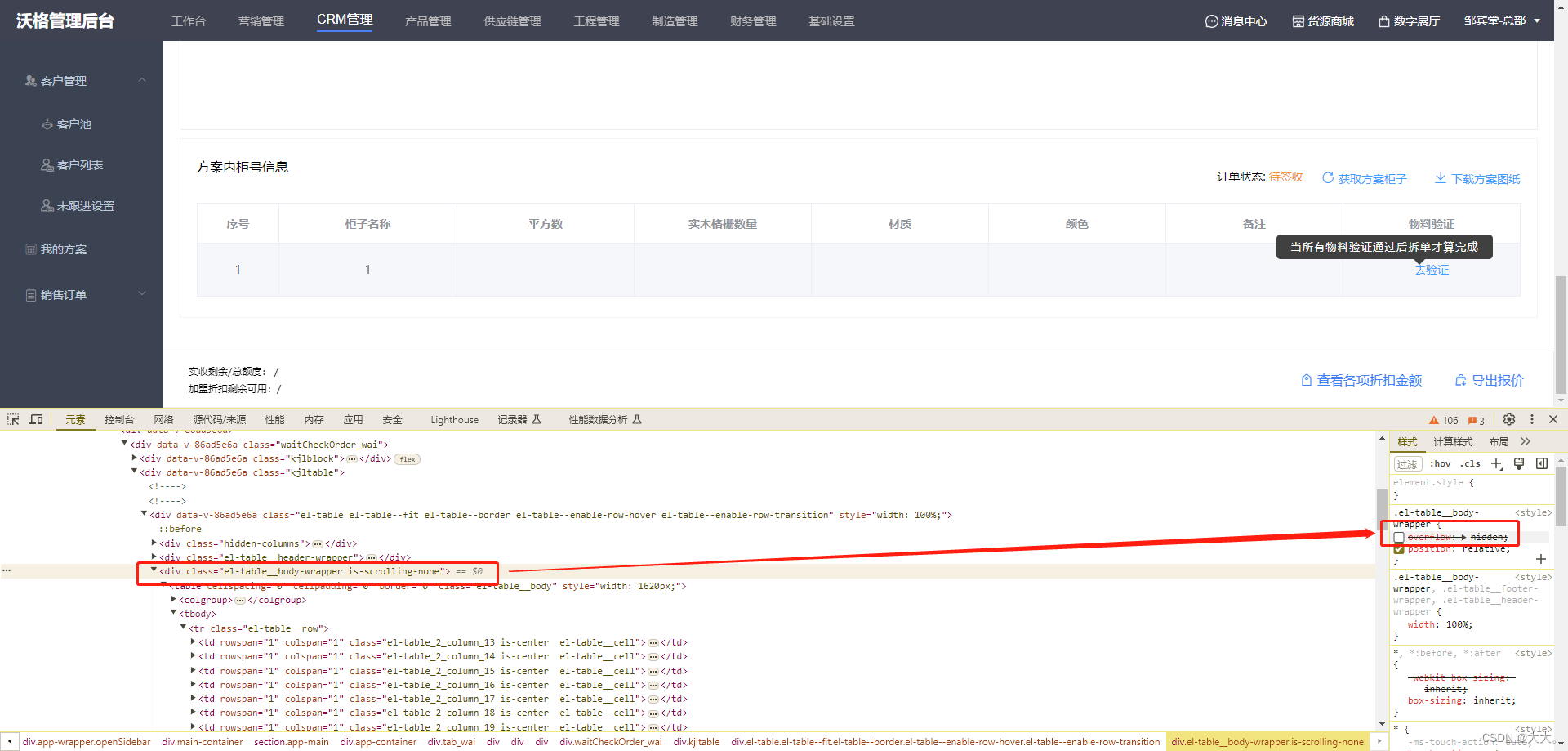

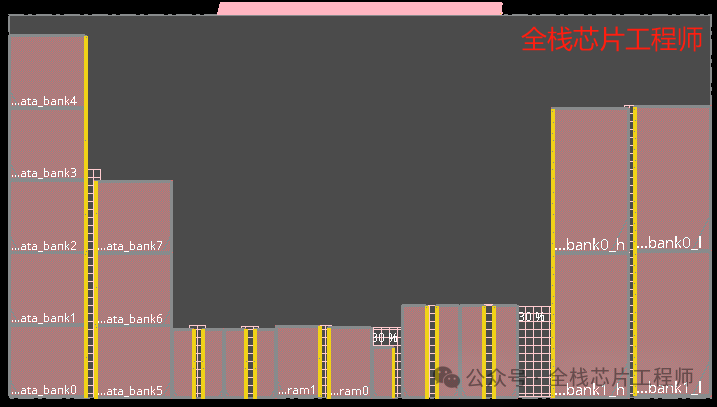

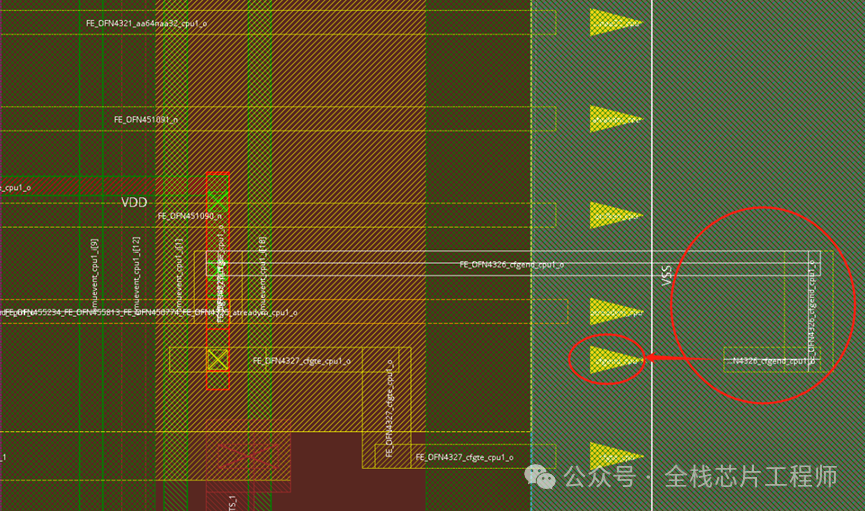

再分享个例子,比如,Cortex-A72基础版课程有学员的Cortex-A72 maia_cpu LVS通过, 但是MAIA顶层LVS比对不过,我们来定位一下。

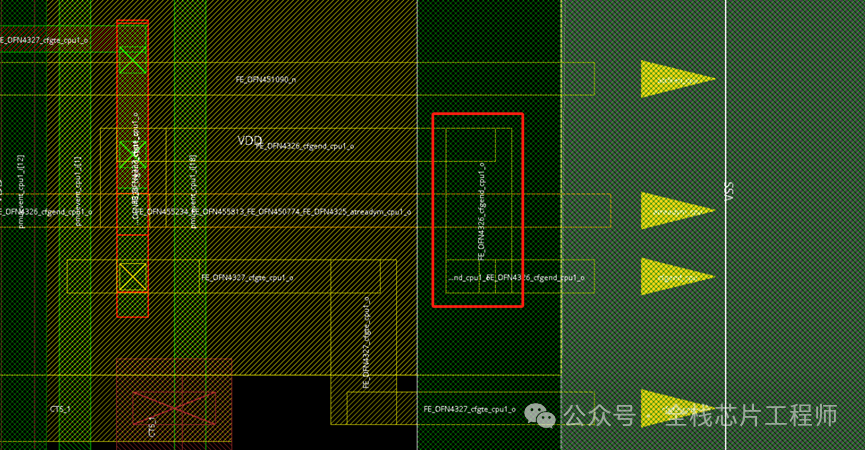

以FE_OFN4326_cfgend_cpu1_o为例,点击下图FE_OFN4326_cfgend_cpu1_o:

找到calibredrv错误坐标:(1949,139)

对应到innovus去看坐标:(1949,139)

看到maia_cpu的pin脚过于密集,造成顶层连接pin脚时候会无法绕线,从而导致innovus从maia_cpu上面走线,形成short。尽管maia_cpu带了blockage,但是invs没有足够的连接pin的routing resource,也就只能在maia_cpu上面去try了。

修改办法很简单,具体操作option参见知识星球。

保存db,重新LVS,比对通过。

03

12nm Cortex-A72—DFT实战

开发完成,全国最低价!

04

景芯SoC—全芯片UPF后端实战

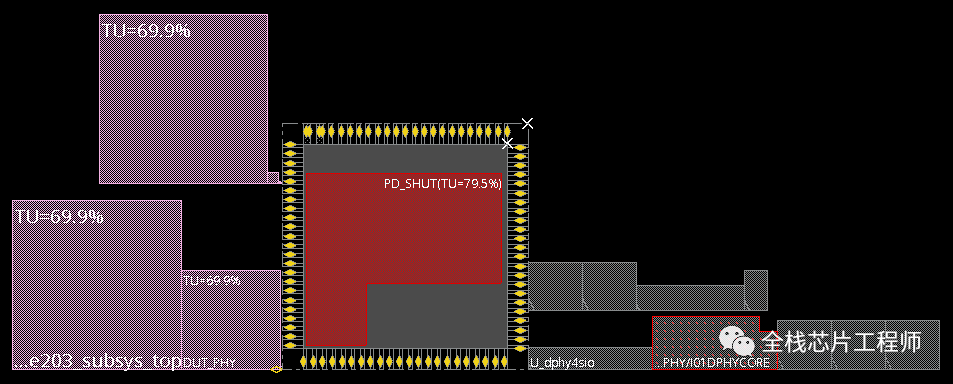

景芯SoC培训的全芯片UPF低功耗设计(含DFT设计)

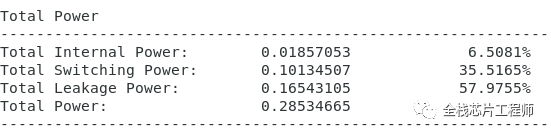

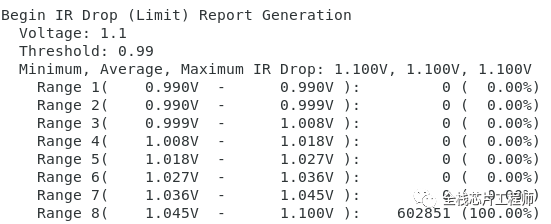

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

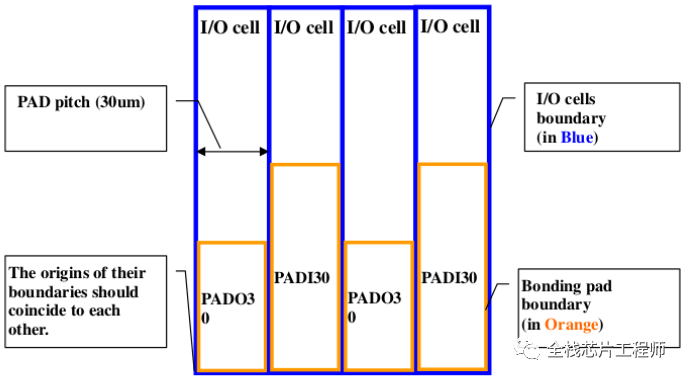

7天冲刺PR训练营有同学问如何给IO添加PAD?请思考景芯SoC的IO和PAD如何实现最佳?

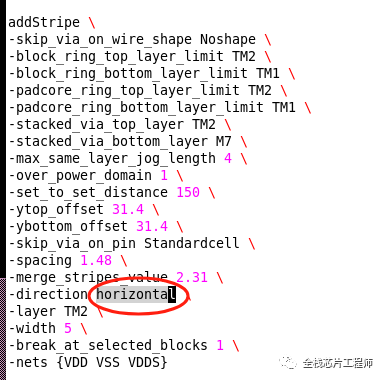

7天冲刺PR训练营有同学问,同样的floorplan,有些同学很快跑完,有些同学则遇到大量DRC问题(EDA工具不停iteration)导致工具始终无法跑完,具体什么问题呢?

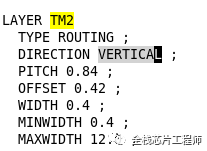

首先,小编发现该同学的stripe把TM2定义为了horizontal,而熟悉景芯工艺的同学知道,TM2的preference direction是VERTICAL。

查询景芯的lef库文件也可以确认:

用错方向有多大影响呢?大家上景芯SoC的后端flow实践一下吧,实践出真知。

7天冲刺PR训练营有同学问,为啥PR花了一天一夜24个小时完成布线还大量DRC错误?小编已经将设计规模尽可能减小以加速PR设计,实际上2小时就可以跑完routing,为何这么慢?原因就是低功耗单元的走线。具体原因及解决办法欢迎加入景芯训练营讨论。

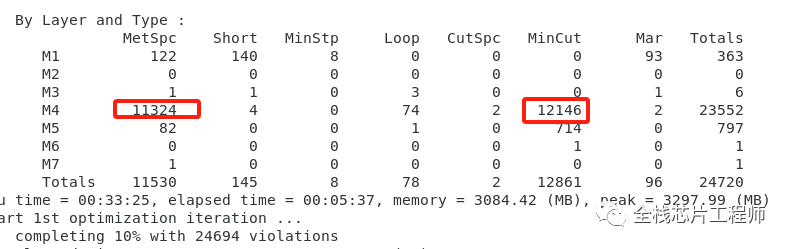

其错误主要集中在M4上,请思考如何解决。

7天冲刺PR训练营有同学问,power switch cell的secondPG pin(VDDG)从M1接出的,而不是M2, 请思考有什么问题?如何解决?

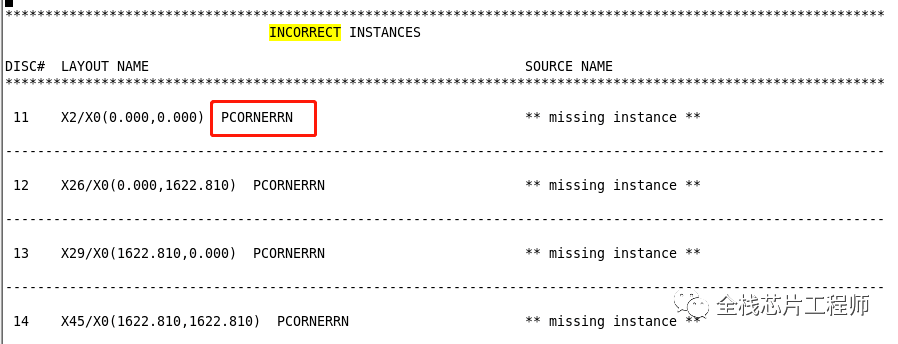

7天冲刺PR训练营有同学问,景芯SoC培训营同学遇到Corner Pad LVS不过怎么处理?

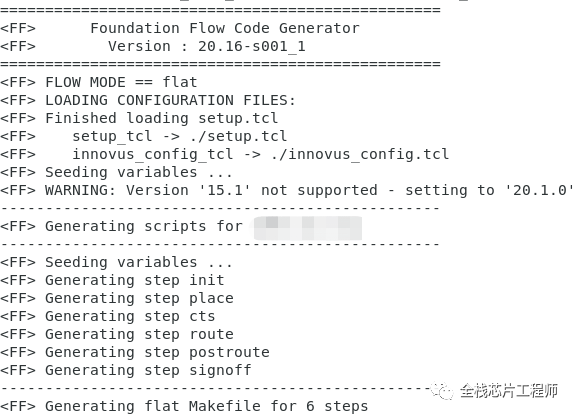

完成景芯SoC培训的前端设计仿真、DFT后,我们来到后端flow,本教程教你一键式跑完数字后端flow。

生成脚本命令如下:

tclsh ./SCRIPTS/gen_flow.tcl -m flat all

生成flow脚本之前需要配置setup.tcl等相关参数,具体参见【全网唯一】【全栈芯片工程师】提供自研的景芯SoC前端工程、DFT工程、后端工程,带你从算法、前端、DFT到后端全流程参与SoC项目设计。

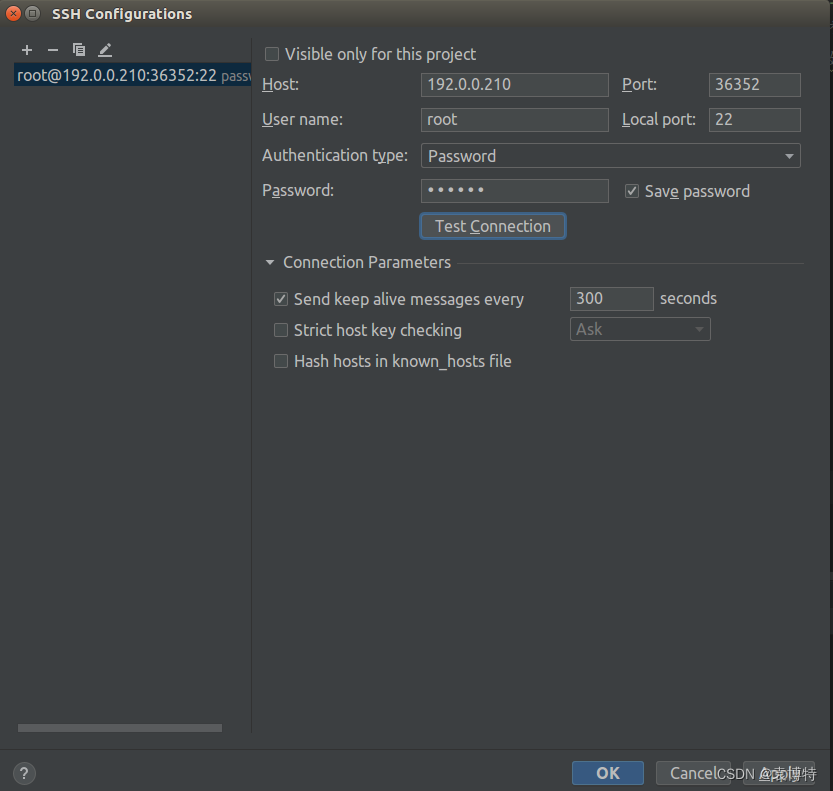

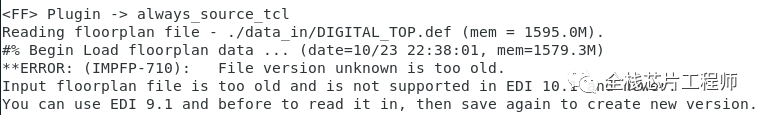

景芯SoC训练营的同学问,为何innovus读取做好的floorplan def文件报Error? 首先看log:

Reading floorplan file - ./data_in/DIGITAL_TOP.def (mem = 1595.0M).

#% Begin Load floorplan data ... (date=10/23 22:38:01, mem=1579.3M)

**ERROR: (IMPFP-710): File version unknown is too old.

以前EDI的时期,我们可以通过定义fp_file的方式来加载floorplan:

set vars(fp_file) "./data_in/DIGITAL_TOP.def"

但是现在innovus升级并放弃了fp_file的加载方式,当然也可以用老版本的EDI9.1及以前版本来加入fp_file,然后转存为新版本,这方式明显没有必要。正如下log提示所说,检查log是非常好的工程师习惯。

Input floorplan file is too old and is not supported in EDI 10.1 and newer.

You can use EDI 9.1 and before to read it in, then save again to create new version.

小编的直觉告诉我,先去看看同学保存的def文件是哪个def版本?

同学保存方式如下:

那么请问如何解决?请大家加入景芯训练营实践。

景芯SoC用了很多异步FIFO,关注异步RTL实现的同学,可以抓取异步FIFO出来看一下版图连线:

查看下所有异步FIFO cell的面积;

dbget [dbget top.insts.pstatus unplaced -p].area

查下所有异步FIFO的cell的名字:

dbget [dbget top.insts.pstatus unplaced -p].name

那么怎么抓出异步路径来观察版图走线呢?如何让report_timing呢?更多内容参见知识星球和SoC训练营。