目录

1.1 Avlon 总线

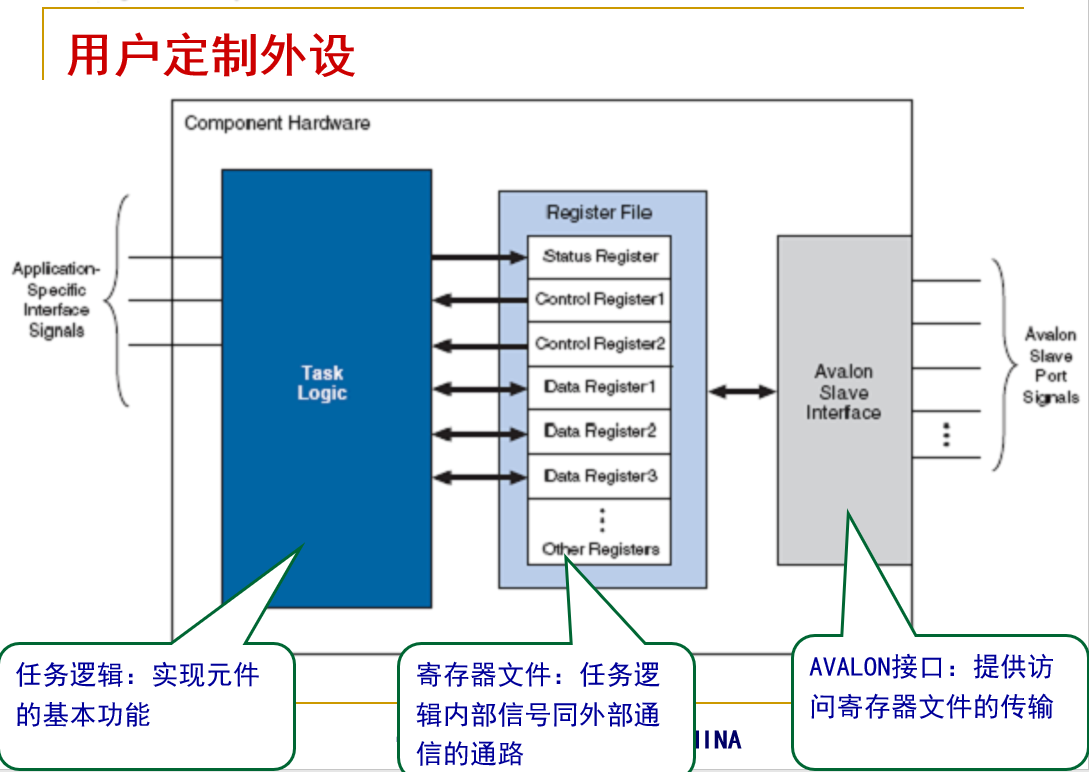

定制 外设 IP 核的框架

从端口传输

从端口信号类型

从端口传输模式列举

基本单周期读写传输

固定等待周期的读写传输

可变等待周期的读写传输(推荐)

具有建立时间和保持时间读写传输

主端口传输

主端口信号类型

主端口传输模式列举与参数说明

主端口 单/可变周期 的读传输

主端口 单/可变周期 的写传输

其它 Avalon 传输模式

编辑整理 by Staok,始于 2021.2 且无终稿。转载请注明作者及出处。整理不易,请多支持。

本文件是“瞰百易”计划的一部分,尽量遵循“二项玻”定则,致力于与网络上碎片化严重的现象泾渭分明!

本文系广泛撷取、借鉴和整理,适合刚入门的人阅读和遵守,已经有较多经验的人看一看图个乐,如有错误恭谢指出!本文已经是长期积累和堆叠而形成一定规模,不必按照从前到后的顺序去看,可以挑感兴趣的章节去看。

本文为简述风格,本意即记录要点和便于快速拾起。

本文对应的 Github/Gitee 仓库地址,本文最新的原文 和 一些源码、备查手册等等 均放在里面。

1.1 Avlon 总线

Intel FPGA Avalon 总线,其灵活特点有:

- 时钟同步的;分主、从信号线和时序,主外设能发起传输;多主多从;

- 主、从时钟频率可不同,位宽可不同;

- 专用的地址总线、数据总线和控制总线,支持高达 1024 位的数据宽度、不是 2 的偶数幂的数据宽度;

- 高性能,易实现,占用资源少,开放使用。

- 多种模式,时延和时序可调整,定制外设 IP 核超级灵活。

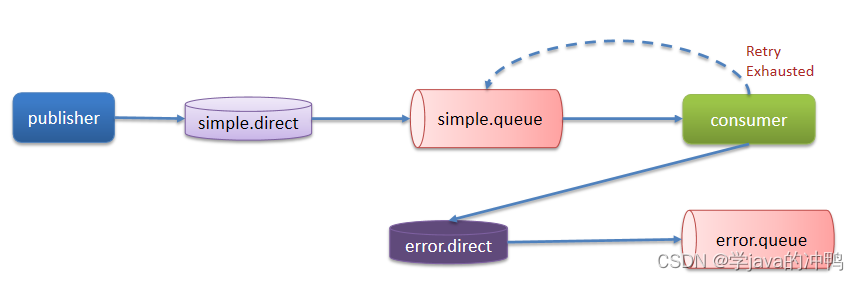

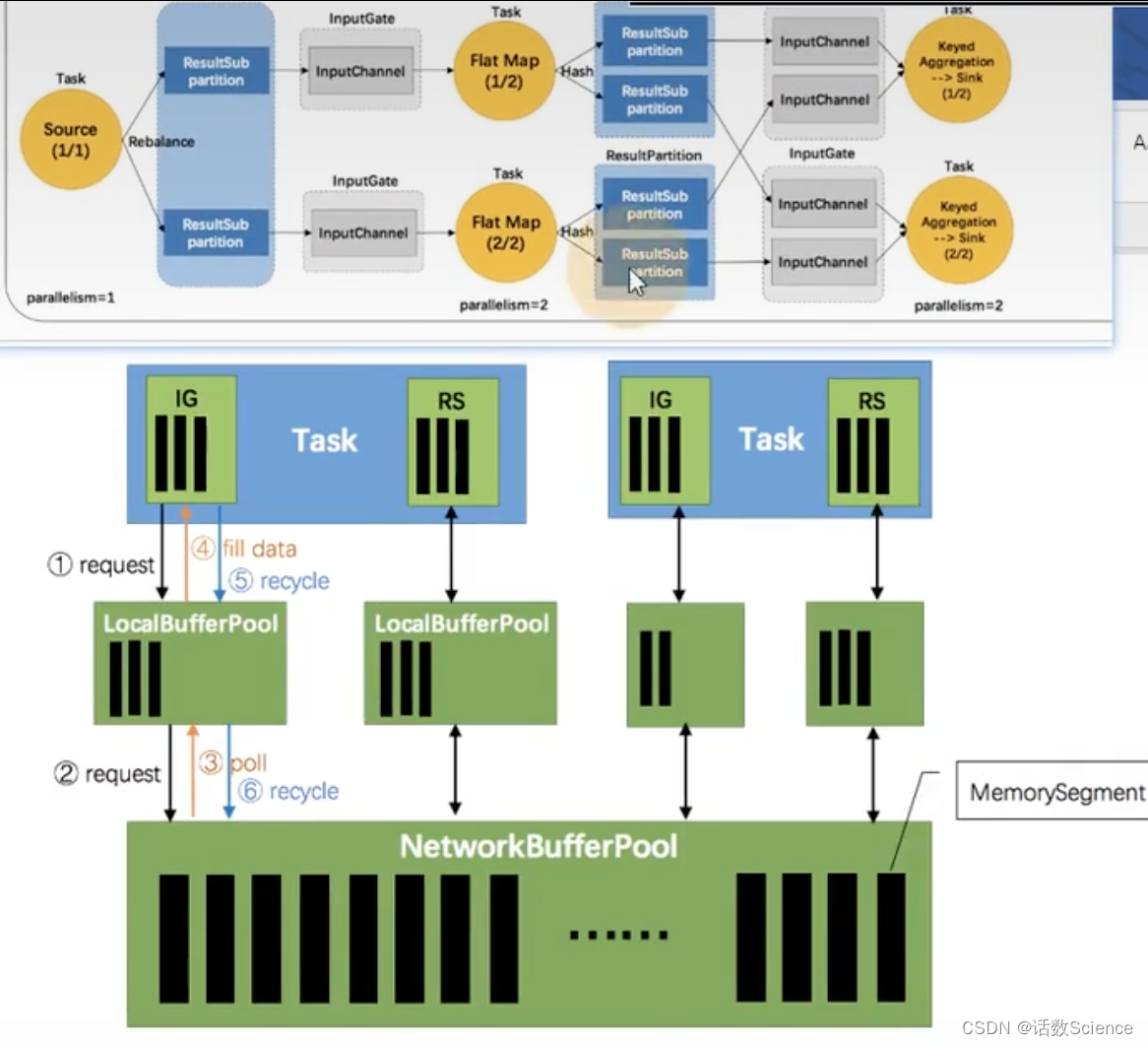

若只使用 Quartus II 的 Qsys 自带的定制的 Avalon 总线外设构建 SOPC 系统,不需了解 Avalon 总线,因为这些自带外设的接口都已经写好了 Avalon 总线,在图形化连接总线时,就是在把各个外设的从 Avalon 接口挂载到 Nios II 的主 Avalon 总线上;若采用用户定制外设构建 SOPC 系统,所开发外设必须符合 Avalon 总线规范,需要熟悉 Avalon 总线。下图为典型 Avalon 架构。下图最右面上下两个外设框分别为用户自定义主端口和用户自定义从端口。

Avalon 主端口发起对 Avalon 总线的传输,Avalon 从端口响应来自 Avalon 总线的传输。主从端口对即在某次数据传输过程中,通过 Avalon 总线连接起来的主端口和从端口。

定制 外设 IP 核的框架

从端口传输

从端口信号类型

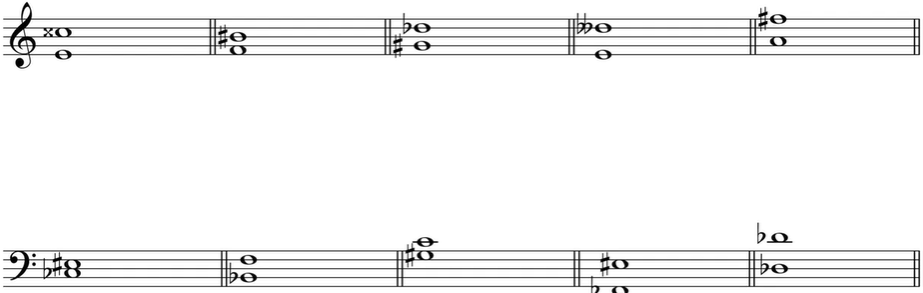

*p.s 其中前九个(标粗体的)最常用;不带 “_ n” 后缀的都是高电平有效;还有流水线信号、突发信号、三态信号和流控信号等,没有列出。*

p.s 不带任何读写功能的、最基本信号:clk、reset_n、chipselect、address 四个,即下表中的前四个。

p.s address 地址的信号宽度最好都设置为 32 位宽,地址对齐的时候一一对应,最简便。

p.s Avalon 接口规范没有对 Avalon 外设的信号指定命名规则;Avalon 外设的信号的名字可以与信号类型名相同,也可以遵循 用户 / 系统级的命名规则。

p.s 下表只列基本信号,其它如流水线信号、突发信号、流控制信号、三态信号等不予列出。

| 信号类型 | 信号宽度 | 方向 | 功能和使用描述 |

|---|---|---|---|

| clk | 1 | IN | Avalon从端口的同步时钟,所有信号必须与clk同步,异步外设可以忽略clk信号。 |

| reset_n | 1 | IN | 从外设复位信号。该信号有效时,从外设进入确定的复位状态。 |

| chipselect | 1 | IN | Avalon从端口的片选信号。 |

| address | 1~32 | IN | Avalon从端口的地址线,指定了从外设地址空间的字的地址偏移,要访问外设寄存器的地址,从0x00开始。 |

| read | 1 | IN | 读从端口的请求信号。若使用了该信号,则必须使用readdata或data信号。 |

| readdata | 1~1024 | OUT | 读传输时,输出到Avalon总线的数据线。若使用了该信号,则data信号不能使用。 |

| write | 1 | IN | 写从端口的请求信号。若使用了该信号,必须使用writedata或data信号,writebyteenable信号不能使用。 |

| writedata | 1~1024 | IN | 写传输时,来自Avalon总线的数据线。若使用了该信号,data信号不能使用。 |

| waitrequest | 1 | OUT | 若从端口不能立即响应Avalon总线,用该信号来暂停Avalon总线。用于可变等待周期模式。 |

| irq_n | 1 | OUT | 从外设的中断请求信号。 |

| byteenable | 2,4,6,8,16,32,64,128 | IN | 按字节寻址访问使能信号。在对宽度大于8位的存储器进行写传输时,该信号用于选择特定的字节段。若使用了该信号,writedata信号必须使用,writebyteenable信号不能使用。 |

| writebyteenable | 2,4,6,8,16,32,64,128 | IN | 该信号是byteenable信号和write信号的逻辑与操作。write和byteenable信号不能使用。 |

| Begin transfer | 1 | IN | 在每次传输的第一个周期内有效,使用用法取决于具体外设。 |

32 位从端口的 byteenable 信号功能定义表如下。

| byteenable[3..0] | 写操作 |

|---|---|

| 1111 | 全 32 位写操作 |

| 0011 | 2 个低字节的写操作 |

| 1100 | 2 个高字节的写操作 |

| 0001 | 字节 0 的写操作 |

| 0010 | 字节 1 的写操作 |

| 0100 | 字节 2 的写操作 |

| 1000 | 字节 3 的写操作 |

IN (输入)类型的信号都是 Avalon 总线进行置位,从端口不能对其操作,从端口只能操作 OUT (输出)类型的信号。

主端口信号类型表略。

从端口传输模式列举

- 基本单周期读写时序传输。固定等待周期的读写传输。可变等待周期的读写传输(个人推荐常用)。(只对从端口有)

- 具有建立时间和保持时间的固定等待周期的读写传输(用于异步外设,了解)。(只对从端口有)

- 流水线读传输(带固定延迟和可变延迟)。

- 流控制时序传输。

- 三态时序传输。

- 突发时序传输。

下面分别列举时序图。可以看时序图直接上手编写逻辑,但提醒还是先多参考参考,熟悉广泛使用的成熟的编写架构和思路。

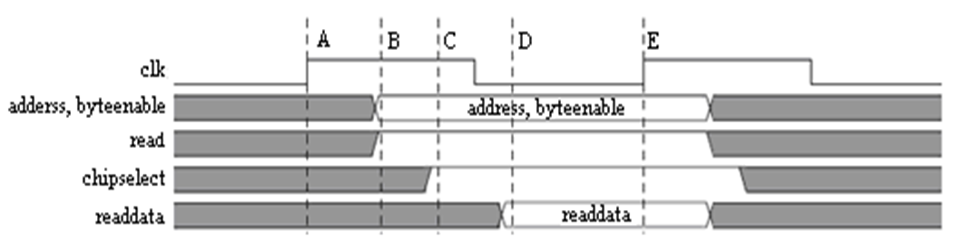

基本单周期读写传输

读时序:

A 沿为主端口发起 读传输,E 沿 为主端口取走要读的数据;在 E 沿之前从端口的外设必须提前在 readdata 数据线上准备好数据。

基本读传输适用于异步从外设,只要外设被选中或地址发生变化,外设就立刻返回数据。readdata 须在下一个时钟上升沿之前保持稳定。

从端口通常在 clk 下降沿 检测 chipselect 和 read 两个信号同时为高时,就认为一次读传输。

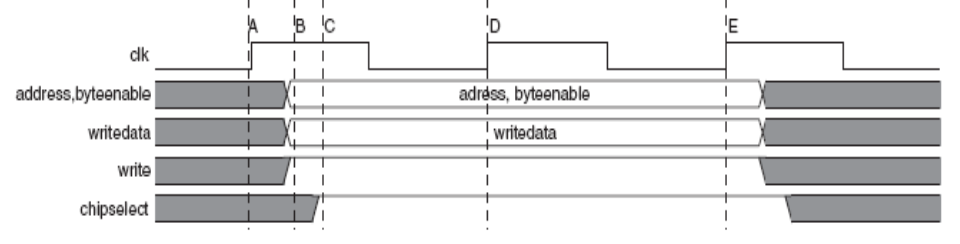

写时序:

A 沿为主端口发起 写传输,D 沿为主端口准备好要写的数据,在此沿从端口外设要取走数据。基本写传输适用于片内同步外设。

从端口通常在 clk 下降沿 检测 chipselect 和 write 两个信号同时为高时,就认为一次读传输。从端口可以在 D 沿取走数据。

基本写传输适用于片内同步外设。

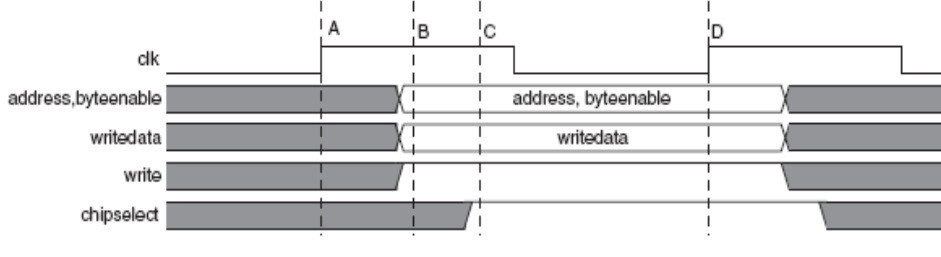

固定等待周期的读写传输

读传输:等待周期允许从端口使用一个或多个时钟周期来捕获地址和/或返回有效 readdata,等待周期会影响从端口的吞吐量。

写传输:等待周期允许从端口使用一个或多个时钟周期来捕获地址和 writedata,等待周期会影响从端口的吞吐量。

用于同步外设访问,读传输等待周期是必须的,写传输非必须。

在 Qsys 中导入定制 IP 核时,可设要等待的固定周期,读和写时序的等待周期是一样的;可以在 clk 上升沿检测主端口的 读/写 传输。

读时序:

写时序:

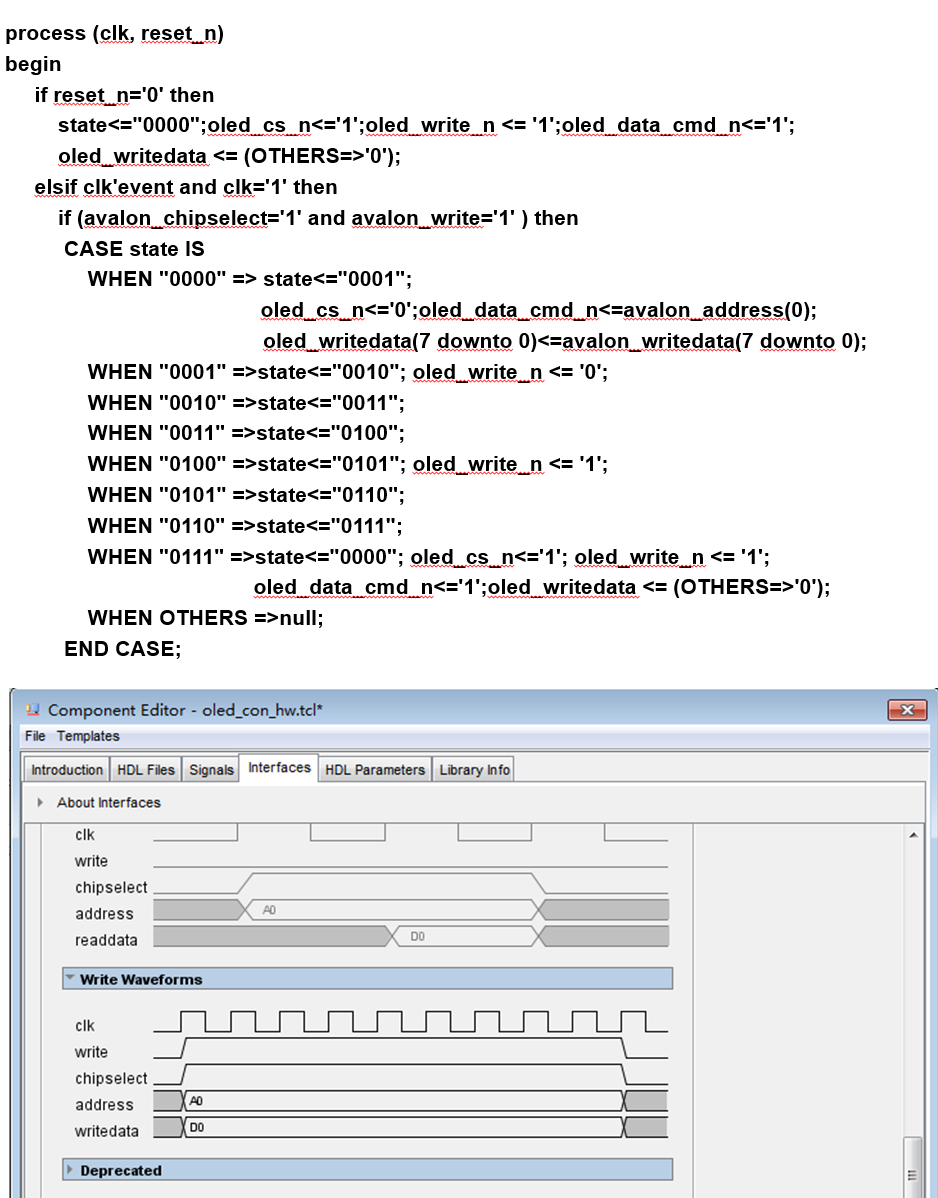

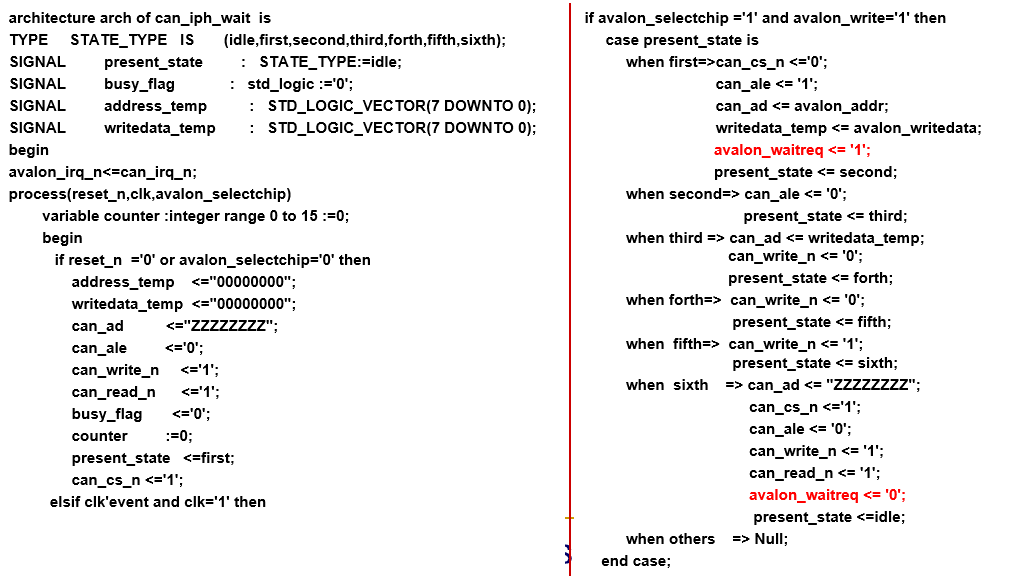

固定等待周期写传输的一个例子:

OLED 定制外设 IP 的部分源码,从端口的写传输实现,VHDL;第二个图是软件设置固定等待周期数,要与源码中的一致。

可变等待周期的读写传输(推荐)

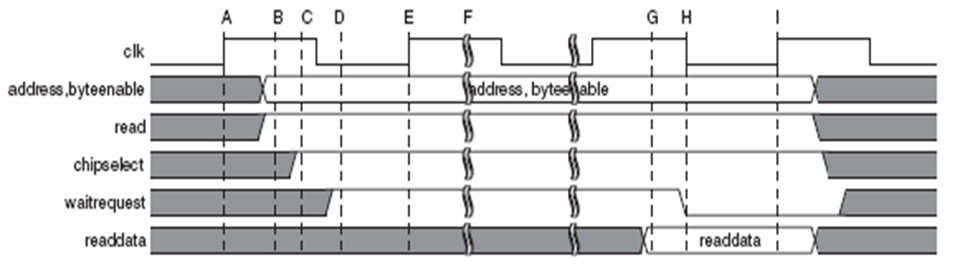

读传输:等待周期允许从端口使用一个或多个时钟周期来捕获地址和/或返回有效readdata,等待周期会影响从端口的吞吐量。

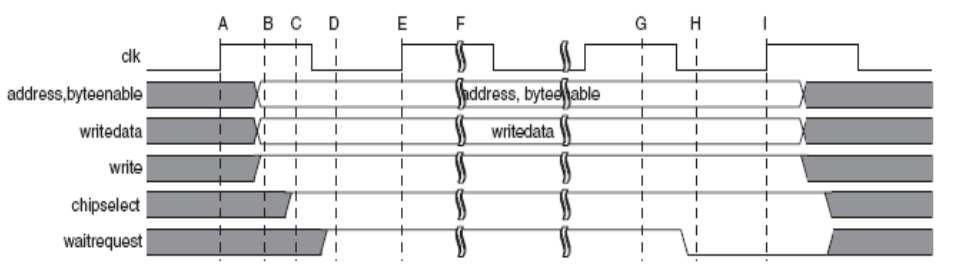

写传输:等待周期允许从端口使用一个或多个时钟周期来捕获地址和writedata,等待周期会影响从端口的吞吐量。

可变等待周期采用 waitrequest 信号实现,看时序图就容易明白。从端口必须在第一个总线时钟周期内设置 waitrequest 有效,直到从端口处理好数据再置 waitrequest 信号无效,然后总线在下一个时钟上升沿捕获数据,结束本次传输。

读时序:

写时序:

可变等待周期写传输的一个例子:

OLED 定制外设 IP 的部分源码,从端口的写传输实现,VHDL。

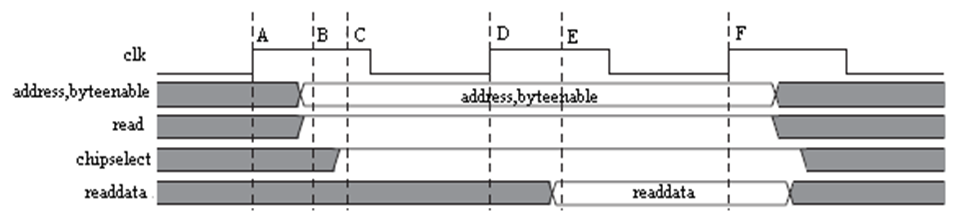

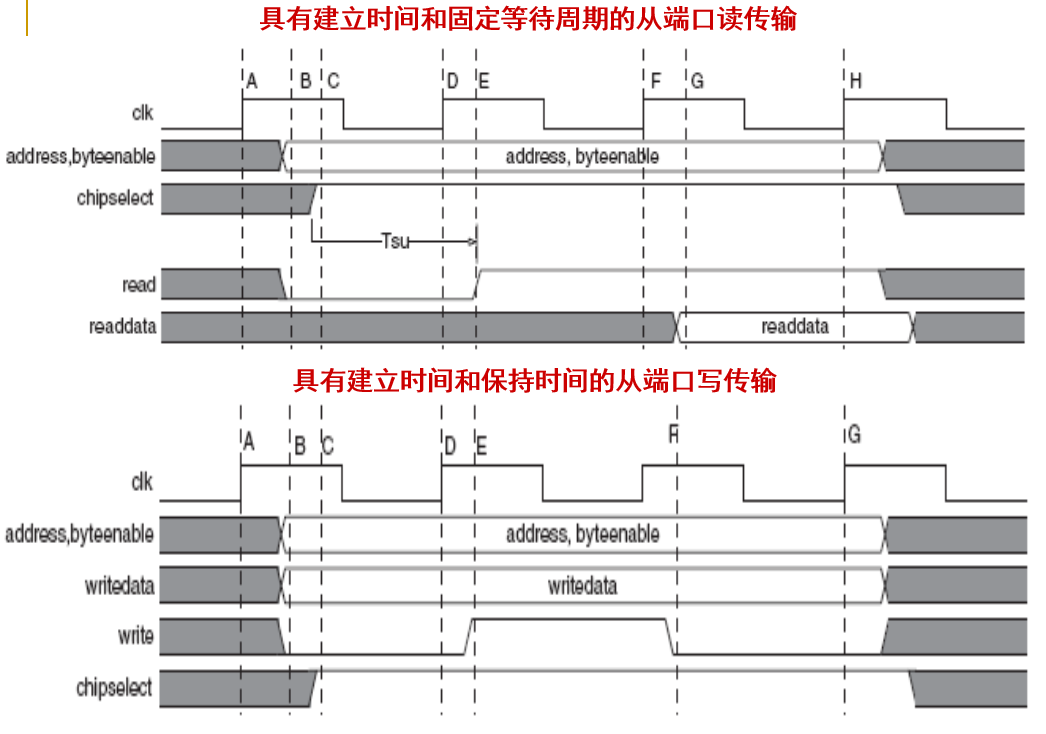

具有建立时间和保持时间读写传输

具有建立时间和保持时间的固定等待周期的读写传输,用于异步外设,了解。

具有建立时间和固定等待周期的从端口读传输,对于片外从端口异步外设,在主端口发出 read 有效信号之前,需要地址和 chipselect 等信号先稳定一段时间,然后将 read 信号置位有效,这样异步外设可以在 read 上升沿开始根据其他信号做出反应,而不会引起冒险竞争,因为在 read 上升沿时其他信号均已稳定。可以设置固定等待周期。即具有建立时间、固定等待周期的读传输(建立时间和可变等待周期不能同时采用)。下图中,上面的时序图,Tsu 即建立时间。

具有建立时间和保持时间的从端口写传输,对于片外从端口异步外设,在主端口发出 write 有效信号之前,需要 address、byteenable、writedata 和 chipselect 信号保持几个周期的稳定时间。即具有建立时间、固定等待周期、保持时间的写传输。下图中,下面的时序图,C 沿到 E 沿 之间的时间 即建立时间,E 沿到 F 沿 之间的时间 即保持时间。

端口读传输和写传输的建立时间必须相同。

对于一些 ram 等芯片的时序,设置的当可以把 Avalon 总线 直连 此类芯片的总线接口,即该从端口时序通常用于片外外设。

“建立时间、固定等待周期和保持时间” 属性在 Qsys 中设置;端口读传输和写传输的建立时间必须相同;建立时间和可变等待周期不能同时采用。

主端口传输

主端口信号类型

p.s Avalon 主端口必须有三个信号:clk、address、waitrequest。

p.s 下表只列基本信号,其它如流水线信号、突发信号、流控制信号、三态信号等不予列出。

| 信号类型 | 信号宽度 | 方向 | 必需 | 功能及使用描述 |

|---|---|---|---|---|

| clk | 1 | In | Yes | Avalon主端口的同步时钟, 所有的信号必须与clk同步。 |

| waitrequest | 1 | In | Yes | 迫使主端口等待, 直到Avalon总线准备好处理传输。 |

| address | 1~32 | Out | Yes | 从Avalon主端口到Avalon总线的地址线。 表示的是一个字节的地址, 主端口只发出字边界的地址。 |

| read | 1 | Out | No | 主端口的读请求信号。 主端口不执行读传输时不需要该信号。 若使用了该信号,readdata或data信号线必须使用。 |

| readdata | 8,16,32,64,128,256,512,1024 | In | No | 读传输时,来自Avalon总线的数据线。 当主端口不执行读传输时,不需要该信号。 若使用了该信号,read信号必须使用,data信号不能使用。 |

| write | 1 | Out | No | 主端口的写请求信号,不执行写传输时不需要该信号。使用该信号,writedata或data信号必须使用。 |

| writedata | 8,16,32,64,128,256,512,1024 | Out | No | 写传输时,到Avalon交换架构的数据线。当主端口不执行写传输时,不需要该信号。使用该信号,write信号必须使用,data信号不能使用。 |

| byteenable | 2,4,6,8,16,32,64,128 | Out | No | 字节使能信号。在对宽度大于8位的存储器进行写传输时,该信号用于选择特定的字节段。读传输时,主端口必须置所有的byteenable信号线有效。 |

| Irq | 1,32 | In | No | 中断请求信号。 如果Irq信号是一个32位的矢量信号,那么它的每一位直接对应一个从端口上的中断信号;如果Irq是一个单比特信号,那么它是所有从外设的Irq信号的逻辑或,中断优先级irqnumber信号确定。 |

| irqnumber | 6 | In | No | 在irq信号为单比特信号时,使用irqnumber信号来确定外设的中断优先级。 Irqnumber的值越小,所代表的中断优先级越高。 |

| reset | 1 | In | No | 全局复位信号。实现跟外设相关。 |

| resetrequest | 1 | Out | No | 允许外设将整个Avalon系统复位。 |

主端口传输模式列举与参数说明

主端口传输模式列举:

- 单 / 可变等待周期 的读写传输。

- 流水线读传输(带可变延迟)。

- 流控制时序传输;

- 三态时序传输;

- 突发时序传输。

主端口的等待周期、建立时间、保持时间属性:

- 等待周期:主端口使用 waitrequest 信号接受 Avalon 总线的不确定等待周期。主端口被动地支持可变等待周期,不支持固定等待周期。

- 建立时间和保持时间:主端口不使用建立和保持时间属性。若一个目标从外设有建立 和/或 保持时间属性,Avalon 总线管理主从端口对的信号时序的转换。

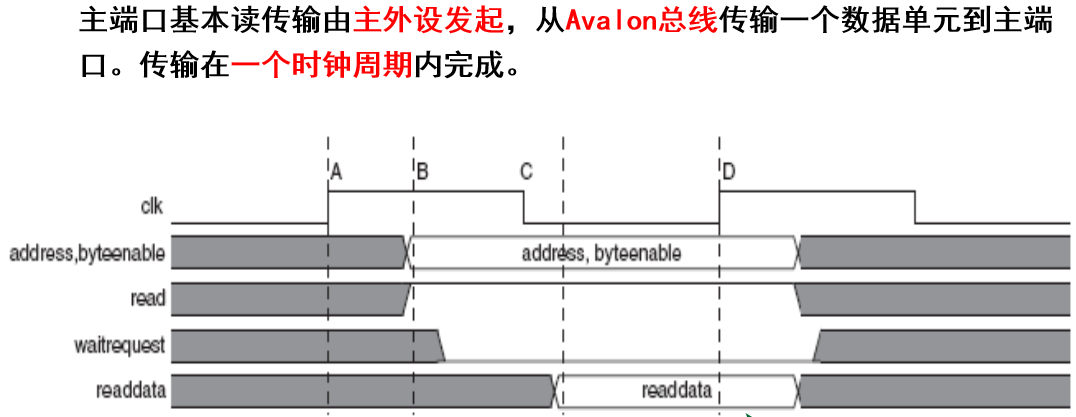

主端口 单/可变周期 的读传输

主端口 单等待周期 的读传输

主端口在 clk 上升沿后紧接着 设置目标外设地址 address 和 置 read 有效,等待 waitrequst 信号失效 便可从 readdata 取数据。

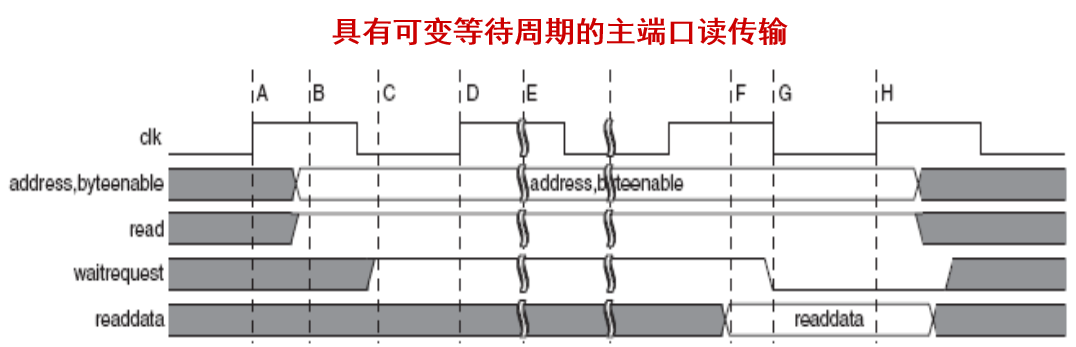

主端口 可变等待周期 的读传输

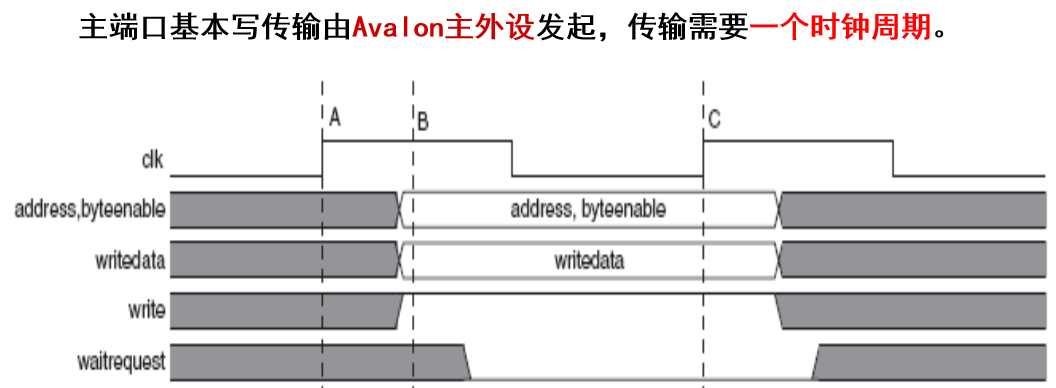

主端口 单/可变周期 的写传输

主端口 单等待周期 的写传输

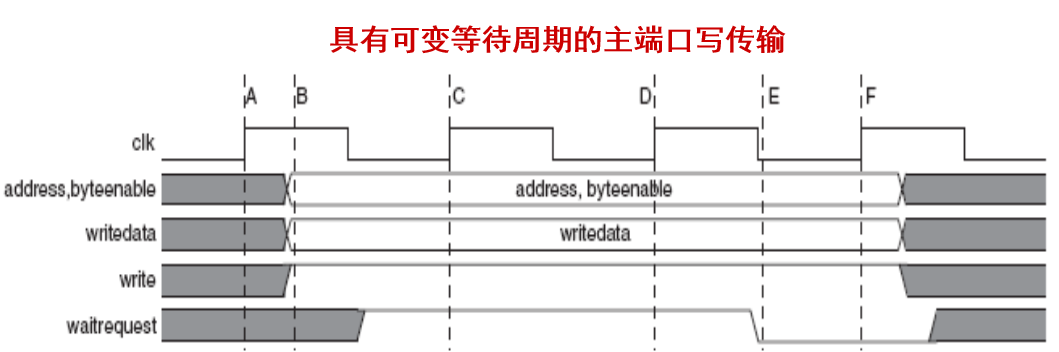

主端口 可变等待周期 的写传输

其它 Avalon 传输模式

这里略。

- 流水线读传输。

- 流控制时序传输;

- 三态时序传输;

- 突发时序传输。

- 中断与复位,地址对齐等内容。

![[计网底层小探索]:实现并部署多线程并发Tcp服务器框架(基于生产者消费者模型的线程池结构)](https://img-blog.csdnimg.cn/direct/c033820068dd452f96c57916b5fce352.jpeg#pic_center)