🔥点击查看精选 UCIe 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/128578536】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

文章目录

- 1. DLP/DLLP 概念

- 2. DLP 在 Flit 中的位置

- 3. DLP Bytes

- 3.1 DLP[0:1]

- 3.2 DLP[2:5]

- 3.2.1 DLLP 作用及分类

- PCIe DLLP 分类

- UCIe DLLP 分类

- NOP DLLP

- 3.2.2 Flit_Marker

- 3.2.3 Optimized_Update_FC

- 4. DLLP 的传输

- 4.1 DLLP 发送

- 4.2 DLLP 接收

- 5. 参考

1. DLP/DLLP 概念

从 PCIe 6.0 开始,PCIe Base Spec 中便出现了 DLP 的概念,UCIe 中也沿用了这个概念。大部分人把 DLP 跟 DLLP 当成同一个东西,称不上错,但实际上两者稍有区别。

DLP,Data Link Layer Payload,数据链路层载荷。我们在说 DLP 的时候,通常是指 Flit 中的 6B DLP Bytes。PCIe DLP 中包括 4B DLLP 及 2B CRC,UCIe DLP 包含 2B Flit Header + 4B DLLP (或 Optimized_FC、Flit_Marker)。

DLLP,Data Link Layer Packet,数据链路层包。我们在说 DLLP 的时候,通常是指 DLP Bytes [2:5] 这 4B(下称 DLP[2:5])。

DLLP 仅在 PCIe 或 UCIe 链路两端设备的数据链路层之间传输,其源于发送端设备的数据链路层,终于接收端设备的数据链路层。在 PCIe 中,DLLP 用以链路管理及维护(链路初始化、电源管理等);在 UCIe 中,Sideband 及 FDI/RDI 接口上的握手信号分担了链路初始化及 PM 的工作,因此 UCIe DLLP 的功能主要是 Flow Control 这一项(应该也支持 Vendor Defined DLLP)。

2. DLP 在 Flit 中的位置

在 UCIe 1.0 支持的各种 Flit Mode 中,只有 PCIe 及 CXL.io 256B Flit 中存在 DLP Bytes。UCIe DLP 或 DLLP,都是对 ① Standard 256B Flit Mode for PCIe 6.0 (Format 3) 、② Standard 256B Flit Mode for CXL.io (Format 4) 及 ③ Latency Optimized 256B Flit Mode for CXL.io (Format 5 & 6) 这三种 Flit Mode 而言的。对于其他的 64B 或 68B Flit Mode,都没有 DLP 或 DLLP 的概念。

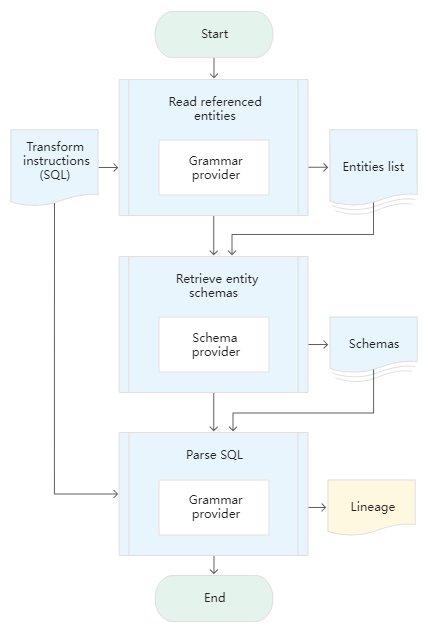

不同 Flit Mode下 DLP 在 Flit 中的位置分别如图 1,2,3 所示。有一点要注意,在 Latency Optimized 256B Flit Mode for CXL.io 操作模式中,在 DLP[2:5] 之外单独为 Flit_Marker 分配了位置。

3. DLP Bytes

3.1 DLP[0:1]

UCIe 的 DLP0 及 DLP1 位置替换为了 Flit Header,不带 Retry 的 Format 3 或 Format 4 Flit Header 格式如表 1 所示。Flit Header 由协议层及 Adapter 共同填充。

3.2 DLP[2:5]

DLP[2:5] 的位置,可以是常规的 Update_FC DLLP 或 Vendor Defined DLLP,也可以是 Optimized_Update_FC 或 Flit_Marker。严格意义上说,Flit_Marker 及 Optimized_Update_FC 都不算是 DLLP,这两种包都没有特定的 DLLP Type 编码,它们只是占用了 DLP Bytes 中 DLLP 的位置。UCIe 1.0 中通过 Flit Header Byte0 Bit4 来指示当前 DLP[2:5] 位置是 DLLP Payload 还是 Flit_Marker 或 Optimized_Update_FC。

3.2.1 DLLP 作用及分类

PCIe DLLP 分类

在 PCIe 中,根据功能的不同,DLLP 大致可分以下几类:

- ACK/NAK DLLP(TLP 应答 DLLP)。包括 ACK、NAK,用以决定重传还是丢弃 Tx Retry Buffer 中的 TLP。仅用于 Non-Flit Mode。

- FC DLLP(Flow Control DLLP)。包括 InitFC1-P、InitFC1-NP、InitFC1-Cpl、InitFC2-P、InitFC2-NP、InitFC2-Cpl、UpdateFC-P、UpdateFC-NP 及 UpdateFC-Cpl,用以初始化及更新流控信用量(Flow Control Credit)。

- PM DLLP (Power Management DLLP)。包括 PM_Enter_L1、PM_Enter_L23、PM_Active_State_Request_L1 及 PM_Request_Ack,用以进行功耗及电源管理。

- LM DLLP (Link Management DLLP),仅用于 Flit Mode 下 L0p 相关链路管理。

- Vendor Defined DLLP。厂商自定义的 DLLP。

ACK/NAK、FC 及 PM DLLP 均为链路管理 DLLP。此外,还有 MR、NOP 及 Data_Link_Feature DLLP。各 DLLP 类型之间通过 DLLP 中的 Tyte 字段 (Byte0) 进行区分。

PCIe 工作在 Flit Mode 时,PCIe Retry 机制所需的 Ack/Nak 及 SN 等 Ack/Nak DLLP 信息拆分到了 Flit Header 中,没有专门的 Ack/Nak DLLP。

UCIe DLLP 分类

UCIe DLLP 是 PCIe DLLP 的子集。跟 PCIe DLLP 相比,UCIe DLLP 主要有以下不同:

- 在 UCIe 中,Sideband 及 FDI/RDI 接口上的握手信号分担了 PM 的工作,因此 UCIe 中没有 PM DLLP。

- UCIe 不具备 PCIe 6.0 的 L0p 低功耗状态,也不具备 L0p 相关的 LM DLLP。

跟 PCIe Flit Mode 一样,Ack/Nak 机制仍然通过 Flit Header (DLP0/DLP1) 中相关字段来保证,本篇不作展开。

NOP DLLP

UCIe 的 NOP DLLP 是指 DLP[2:5] 位置全 0 的 DLLP,当没有 DLLP(Format 3 & 4 时也没有 Optimized_Update_FC 及 Flit_Marker) 要发送时,Adapter 在 DLP[2:5] 填充 NOP DLLP。具体可参考 《UCIe NOP 介绍》第 3 节 NOP DLLP 及 NOP2 DLLP 相关描述。

3.2.2 Flit_Marker

Flit_Marker 用以指示当前 Flit 中最后一笔 TLP 的状态,并携带有 PTM 相关消息。Flit_Marker 包跟 Flit 中的 TLP 强相关,Flit Marker 是包含在 Flit 中的,其在 FDI 接口上走 lp/pl_data,而非 lp/pl_dllp。

Flit_Marker 不是真正的 DLLP,其没有特定的 DLLP Type 编码,通过 Flit Header 中的相关字段及 DLLP Bytes 最高位来指示当前是否为 Flit_Marker,其中 Flit Header Byte0 bit4 为 1 表示当前 Flit 中 DLLP Bytes 为 Optimized_Update_FC 或 Flit_Marker;进一步地,DLLP Bytes 最高位(bit31)为 1 表示 Flit_Marker,为 0 表示 Optimized_Update_FC。

笔者理解,对于发送端而言,其 DLLP 独立于 Flit,仅通过 Flit Header 即可确认当前 Flit 中是否携带 Flit_Marker;对于接收端而言,DLLP 是嵌在 Flit 中的,需要依据 Flit Header 及 DLLP Bytes 最高位共同来判断当前是否为 Flit_Marker。也就是说,Adapter 接收到本端协议层填充的 DLP0 bit4 =1,只能指示当前 Flit 携带了 Flit_Marker,不用以指示 Optimized_Update_FC。对于 Adapter 收到的来自对端的 Flit, DLP0 bit4 =1 才用来指示当前 Flit 中携带有 Flit_Marker 或 Optimized_Update_FC,然后通过 DLP[2:5] 最高位来区分是 Flit_Marker 还是 Optimized_Update_FC。

对于 Standard 256B Flit Mode for PCIe & CXL.io (Format 3 & 4),Flit_Marker 占用了 DLLP 的位置。在发送端,若 Adapter 发现协议层发来的 Flit 中携带有 Flit_Marker,则按照 Flit_Marker 中相关状态来处理,无需填充 DLLP。

对于 Latency Optimized 256B Flit Mode for CXL.io (Format 5 & 6) 中单独预留了 Flit_Marker 的位置,Adapter 接收到协议层发来的带有 Flit_Marker 的 Flit 时,仍然可以在其 DLP[2:5] 填充相关 DLLP。

Flit_Marker 相关介绍可参考《PCIe 每日一问一答(2022.11 已归档)》。

3.2.3 Optimized_Update_FC

Optimized_Update_FC 是一种优化后的流控包,其也不是严格意义上的 DLLP。Optimized_Update_FC 相关介绍可参考《PCIe 每日一问一答(2022.11 已归档)》。对于发送端而言,协议层通过 FDI 接口的 lp_dllp_ofc 信号来指示当前 lp_dllp 中是否为 Optimized_Update_FC;对于接收端而言,则需要依据 Flit Header 及 DLLP Bytes 最高位共同来判断当前 Flit 中是否携带 Flit_Marker。当 Adapter 向协议层传递 Optimized_Update_FC 时,Optimized_Update_FC 在 FDI 接口上走 lp_dllp,而非 lp_data。

有两种方式可以产生 Optimized_Update_FC:

- 协议层直接发送 Optimized_Update_FC 给 Adapter,并通过 lp_dllp_ofc=1 告知 Adapter 当前为 Optimized_Update_FC ;

- 在 Adapter内部 将协议层发来的多笔 Update_FC 整合成一笔 Optimized_Update_FC。

4. DLLP 的传输

4.1 DLLP 发送

UCIe Adapter 负责接收来自协议层的 Flit Data 及 DLLP Data,由 Adapter 将 DLLP 插入 Flit 对应位置。

FDI 提供了 lp_data 信号来传递 Flit Data,Flit Data 中有 DLLP 的位置,但协议层并不用 lp_data 来传递 DLLP,而是提供了独立的 lp_dllp 信号在协议层与 Adapter 之间传递 DLLP。之所以将两者分离开来,是因为 TLP 与 DLLP 并不存在强绑定关系,即便 DLLP 与 Flit Data 中的 TLP 同一时刻到达 Adapter,也不意味着这笔 DLLP 就需要插入该 Flit 中。一来 Adapter 内可能正在发送 Retry Buffer 内的 Flit Data,这时 DLLP 就应该插入到 Retry Buffer 内取出的 Flit 中,协议层最新下发的 Flit Data 放在 Tx Buffer 中待发;二来协议层下发的 DLLP 并不一定会被发送到对端,比如前一 Updata_FC 放在了 Tx Buffer 中待发,在发送这笔 DLLP 之前收到了协议层下发的带有最新 Credit 的 Update_FC,则 Adapter 直接丢掉过期的 DLLP,转而发送最新的 Update_FC DLLP。

RDI 接口上没有独立的信号来传递 DLLP。由于 Adapter 已经将 DLLP 填充到了 Flit 中,此时 RDI 接口 lp_data 内的 DLLP 字段是有效的,DLLP 字段完全通过 lp_data 信号进行传递,Adapter 到物理层之间的 RDI 接口上无需独立的信号来传递 DLLP 信息。

lp_dllp 位宽是可定制化的,若发送一笔 DLLP (4B) 占用多个 lp_dllp Cycle,需按照 LSB 小端模式按序发送 DLLP Data,先发送 DLLP Byte0。

Adapter 接收到的协议层发来的 DLLP(包括 Optimized_Update_FC) 不一定能够被及时发送出去,对于每个 VC (Virtual Channal,虚通道) 的每一种类型的 DLLP,Adapter 中必须为其分配独立的缓存空间且能够存储至少一笔该类型的 DLLP。

发送 DLP 时,标准的 DLLP 及 Optimized_Update_FC 均无需保存进 Retry Buffer。Flit_Marker 跟 TLP 状态有关,需要跟 TLP 一起保存在 Retry Buffer 中。

DLLP 发送频率遵循协议规定,按照一定频率进行交换,防止 Timeout。如果协议层没有 TLP 要发送,需要插入 NIO Flits,便于 Adapter 有机会插入 DLLP。

4.2 DLLP 接收

在接收端,UCIe Adapter 负责从接收到的 Flit 中提取 DLP Bytes,并解析为 DLLP、Optimized_Update_FC 或 Flit_Marker。Adapter 可以根据 Flit Header 中相关信息获知当前 Flit 中含有 Optimized_Update_FC 或 Flit_Marker,并根据 DLP[2:5] 中的最高位来区分到底是两者中的哪一种。接收到的 NOP DLLP 不得传递到协议层,其他 DLLP、Optimized_Update_FC 及 Flit_Marker 均需通过 Flit 中的独立字段或 FDI 接口的 pl_dllp 信号转发到协议层。

5. 参考

- UCIe Spec r1.0, Chapter 3,8

- UCIe NOP 介绍

- PCIe 每日一问一答(2022.05 已归档)

- PCIe 每日一问一答(2022.11 已归档)

|

|

🔥 精选往期 UCIe 协议系列文章,请查看【 Chiplet 专栏】🔥

⬆️ 返回顶部 ⬆️