目录

简单的Verilog HDL程序介绍:

模块的结构 :

模块的端口定义:

模块内容:

I/O说明的格式:

内部信号说明:

功能定义:

简单的Verilog HDL程序介绍:

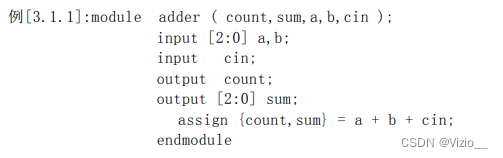

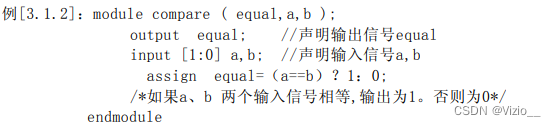

下面先介绍几个简单的Verilog HDL程序,然后从中分析Verilog HDL程序的特性。

这个例子通过连续赋值语句描述了一个名为adder的三位加法器可以根据两个三比特数a、b和进位 (cin)计算出和(sum)和进位(count)。 从例子中可以看出整个Verilog HDL程序是嵌套在module 和 endmodule 声明语句里的。

这个程序通过连续赋值语句描述了一个名为compare的比较器。对两比特数 a、b 进行比较,如a与b 相等,则输出equal为高电平,否则为低电平。在这个程序中,/*........*/和//.........表示注释 部分,注释只是为了方便程序员理解程序,对编译是不起作用的。

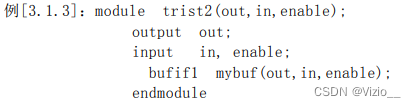

这个程序描述了一个名为trist2的三态驱动器。程序通过调用一个在Verilog语言库中现存的三态驱 动器实例元件bufif1来实现其功能。

• Verilog HDL程序是由模块构成的。每个模块的内容都是嵌在module和endmodule两个 语句之间。每个模块实现特定的功能。模块是可以进行层次嵌套的。正因为如此,才可 以将大型的数字电路设计分割成不同的小模块来实现特定的功能,最后通过顶层模块 调用子模块来实现整体功能。

• 每个模块要进行端口定义,并说明输入输出口,然后对模块的功能进行行为逻辑描述。

• Verilog HDL程序的书写格式自由,一行可以写几个语句,一个语句也可以分写多行。

• 除了endmodule语句外,每个语句和数据定义的最后必须有分号。

• 可以用/*.....*/和//.......对Verilog HDL程序的任何部分作注释。一个好的,有使 用价值的源程序都应当加上必要的注释,以增强程序的可读性和可维护性。

模块的结构 :

Verilog的基本设计单元是“模块”(block)。一个模块是由两部分组成的,一部分描述接口,另一部 分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明:

Verilog结构完全嵌在module和endmodule声明语句之间,每个Verilog程序 包括四个主要部分:端口定义、I/O说明、内部信号声明、功能定义。

模块的端口定义:

模块的端口声明了模块的输入输出口。其格式如下:

module 模块名(口1,口2,口3,口4, ………);

模块内容:

模块的内容包括I/O说明、内部信号声明、功能定义。

I/O说明的格式:

输入口: input 端口名1,端口名2,………,端口名i; //(共有i个输入口)

输出口: output 端口名1,端口名2,………,端口名j; //(共有j个输出口)

I/O说明也可以写在端口声明语句里。其格式如下:

module module_name(input port1,input port2,…

output port1,output port2… );

内部信号说明:

在模块内用到的和与端口有关的wire 和 reg 变量的声明。

reg [width-1 : 0] R变量1,R变量2 。。。。;

wire [width-1 : 0] W变量1,W变量2 。。。。;

………..

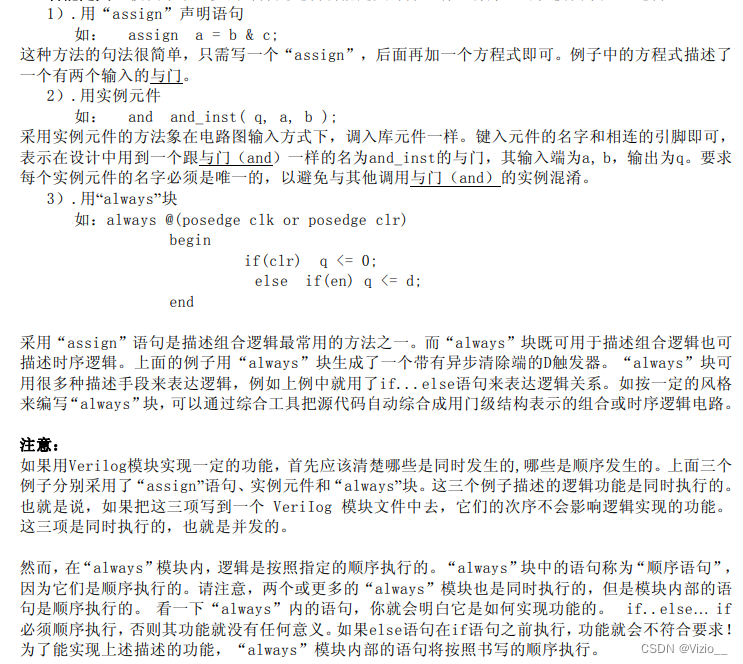

功能定义:

模块中最重要的部分是逻辑功能定义部分。有三种方法可在模块中产生逻辑。