文章目录

- 多功能数据处理器描述

- verilog 无符号数与有符号数

- 8'd100 + 8'd155

- 8'd100 + 8'd156

- 8'd100 + 8'd157

- verilog 代码实现

- TestBench 代码

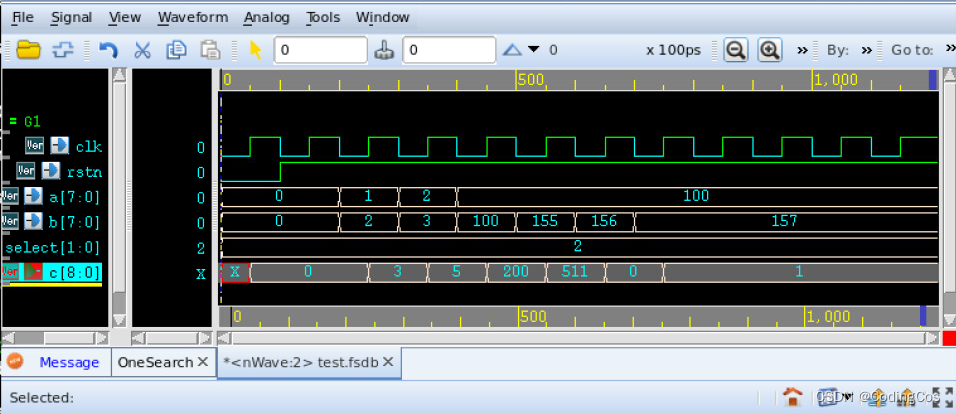

- VCS 仿真结果

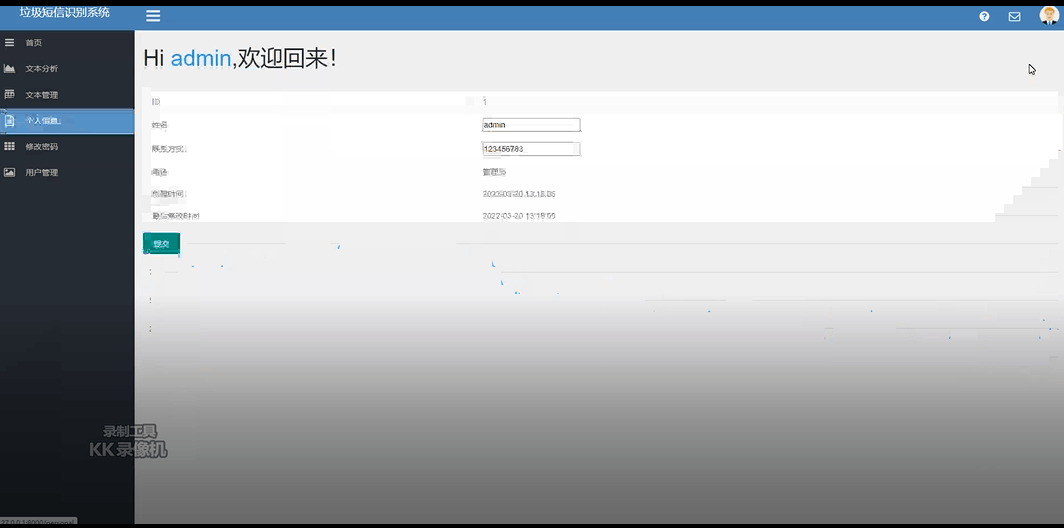

多功能数据处理器描述

根据指示信号select的不同,对输入信号a,b实现不同的运算。输入信号a,b为8bit有符号数:

- 当select信号为0,输出a;

- 当select信号为1,输出b;

- 当select信号为2,输出a+b;

- 当select信号为3,输出a-b.

接口信号图如下:

使用Verilog HDL实现以上功能并编写testbench验证。

输入描述:

- clk:系统时钟

- rst_n:复位信号,低电平有效

- a,b:8bit位宽的有符号数

- select:2bit位宽的无符号数

输出描述:

- c:9bit位宽的有符号数

verilog 无符号数与有符号数

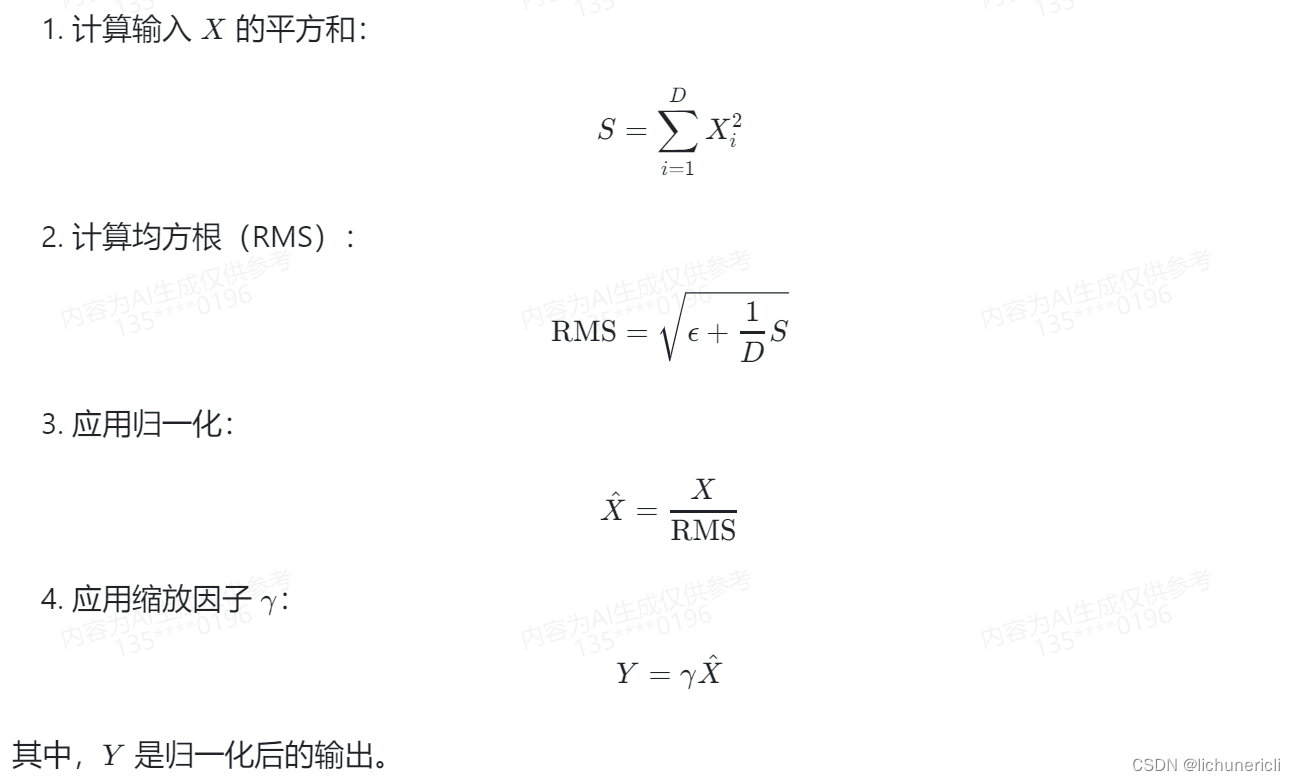

在Verilog中,对于有符号数的加法运算,其操作过程与在二进制算术中的标准加法类似,但需要特别注意数值的溢出和符号位。Verilog中的有符号数是使用补码(two’s complement)表示的,其中最高位用作符号位(0为正,1为负)。

对于8位有符号整数,表示的范围是从-128(10000000)到+127(01111111)。当超出这个范围时,就会发生溢出。在Verilog中,溢出的行为会继续按照二进制加法规则进行,导致结果环绕。

考虑以下三个例子的加法:

8'd100 + 8'd1558'd100 + 8'd1568'd100 + 8'd157

在Verilog中,8'd100表示一个8位的有符号十进制数100,其二进制形式为01100100。对于其他数也是类似的表示。

让我们依次计算这些加法:

8’d100 + 8’d155

100的二进制补码表示:01100100

155的二进制补码表示:10011011(-101的补码)

加法结果是:

01100100

+10011011

-----------

11111111

11111111是-1的补码表示,因此结果是-1。

8’d100 + 8’d156

100的二进制补码表示:01100100

156的二进制补码表示:10011100(-100的补码)

加法结果是:

01100100

+ 10011100

-----------

1 00000000

这里,最左边的1表示发生了溢出(在8位加法中被丢弃),结果是00000000,即0。

8’d100 + 8’d157

100的二进制补码表示:01100100

157的二进制补码表示:10011101(-99的补码)

加法结果是:

01100100

+ 10011101

-----------

1 00000001

同样,发生溢出,结果是00000001,即1。

所以,对于上面的例子:

8'd100 + 8'd155结果是-18'd100 + 8'd156结果是08'd100 + 8'd157结果是1

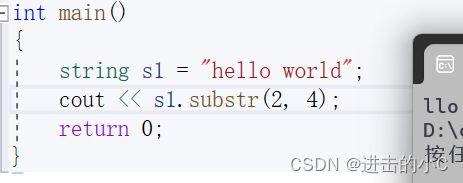

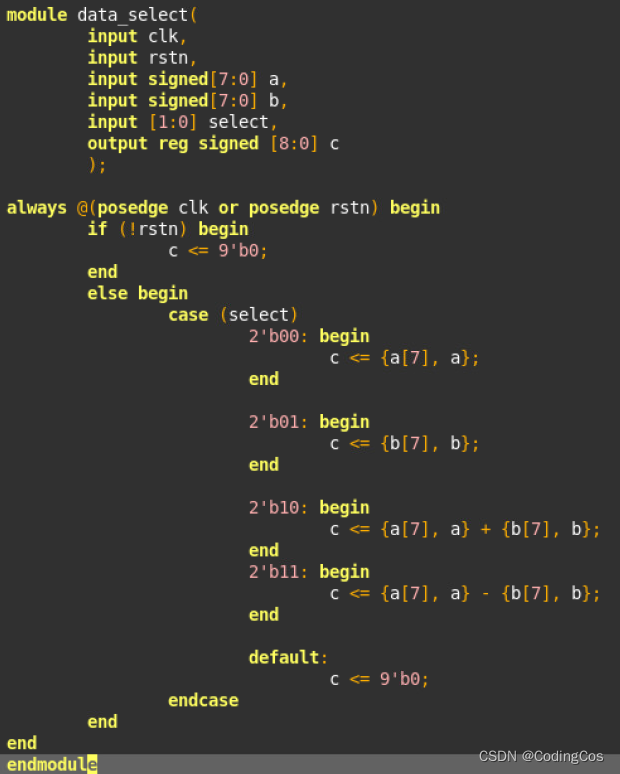

verilog 代码实现

如上图所示,代码中使用位拼接的方法将 a、b的最高位(符号位)补给c。

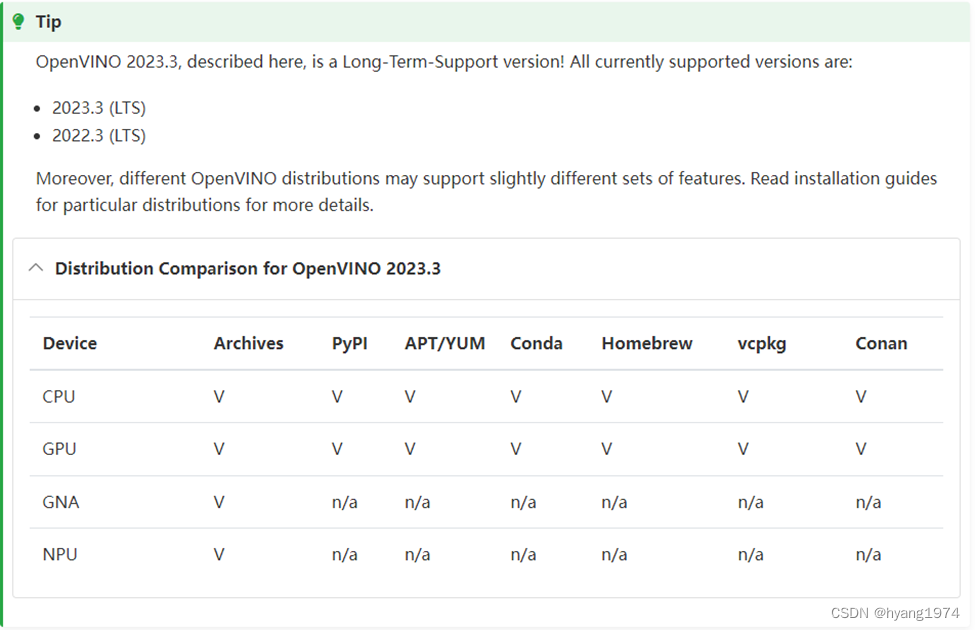

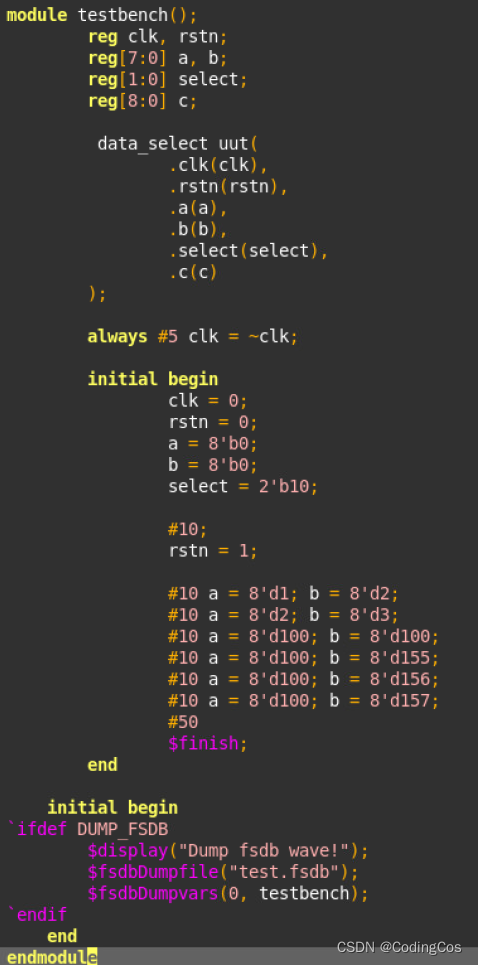

TestBench 代码

VCS 仿真结果