🔥点击查看精选 CXL 系列文章🔥

🔥点击进入【芯片设计验证】社区,查看更多精彩内容🔥

📢 声明:

- 🥭 作者主页:【MangoPapa的CSDN主页】。

- ⚠️ 本文首发于CSDN,转载或引用请注明出处【https://mangopapa.blog.csdn.net/article/details/135945270】。

- ⚠️ 本文目的为 个人学习记录 及 知识分享。因个人能力受限,存在协议解读不正确的可能。若您参考本文进行产品设计或进行其他事项并造成了不良后果,本人不承担相关法律责任。

- ⚠️ 若本文所采用图片或相关引用侵犯了您的合法权益,请联系我进行删除。

- 😄 欢迎大家指出文章错误,欢迎同行与我交流 ~

- 📧 邮箱:mangopapa@yeah.net

- 💬 直达博主:loveic_lovelife 。(搜索或点击扫码)

文章目录

- 0. 引言

- 1. 单 CPU 拓扑

- 2. 多 CPU 拓扑

- Q&A

- 参考

0. 引言

单个 eRCD 支持多个上行端口(Upstream Port,UP),多个 UP 可通过独立的 Flex Bus Link 直接连接到多个 eRCH 下行端口(Downstream Port,DP)上。eRCH 位于 CPU 内,根据该 eRCD 内多个 UP 上行连接的 CPU 数量,可分类为单 CPU 拓扑及多 CPU 拓扑。

下述仅适用于直接跟 eRCH 相连的 eRCD,不适用于 CXL VH;也不适用于连接到 CXL Switch 上的 eRCD。

1. 单 CPU 拓扑

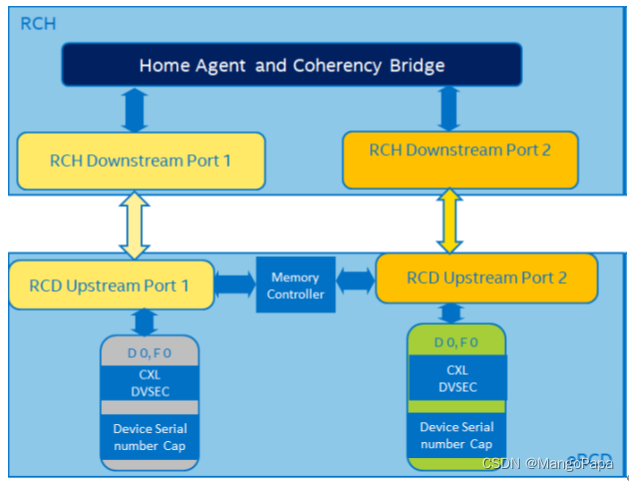

若当前 eRCD 内的多个 UP 连接到同一 CPU 内的多个 eRCH DP,称为单 CPU 拓扑(如下图)。

对于上图中的单 CPU 拓扑,System Firmware 枚举期间两个 eRCD DP-eRCD UP 形成的链路会被识别为两个 PCI 主桥,且两个 eRCD UP 的 Device0 Function0 均会实现该 RCD 所需的 CXL DVSEC 及 PCIe Device Serial Number Extended Capability。两配置空间提供的 Vendor ID 及设备序列号相同,System Firmware 可依此判断出两者同属一个 CXL Device,并进行相关流程或配置上的优化。

采用该拓扑时,允许 CXL 设备驱动屏蔽其中一个 D0F0,即上层软件只向未屏蔽的 D0F0 提交任务。即便如此,在不违反编程模型的前提下,eRCD 内的硬件仍能通过任意一个 UP 向 CPU 发 Traffic 或进行 Snoop。

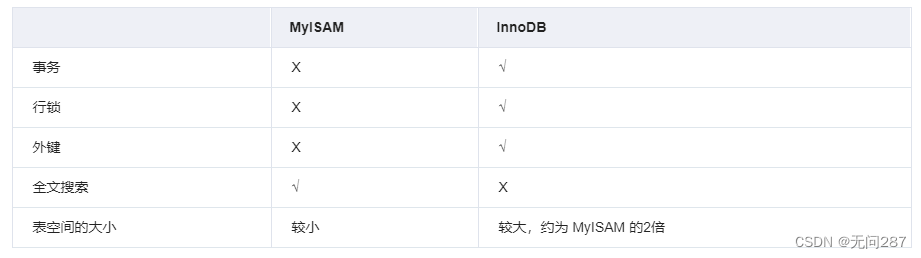

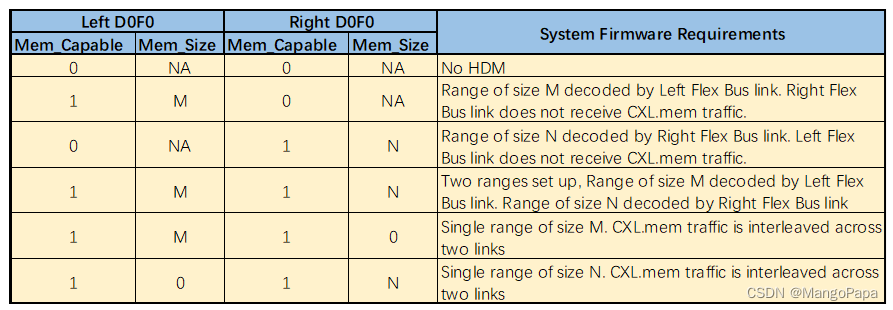

采用该拓扑时,则两个 UP 的 Mem_Capable 能力及 Mem_Size 需求可以独立进行配置并映射到系统地址空间,相关解码规则如下表所示。

根据上表有以下结论:

- 若两个 UP 均支持 CXL.mem 且独立分配了地址空间,则两个链路独立访问各自的 HDM Range;

- 若两个 UP 均支持 CXL.mem 但只有一个分配了空间,则可以通过两个 Link 进行 Interleave 访问,带宽更大。

2. 多 CPU 拓扑

若当前 eRCD 内的多个 UP 连接到多个 CPU 内的多个 eRCH DP,称为多 CPU 拓扑(如下图)。

跟单 CPU 拓扑相同,对于上图中的双 CPU 拓扑,System Firmware 枚举期间两个 eRCD DP-eRCD UP 形成的链路会被识别为两个 PCI 主桥,且两个 eRCD UP 的 Device0 Function0 均会实现该 RCD 所需的 CXL DVSEC 及 PCIe Device Serial Number Extended Capability。两配置空间提供的 Vendor ID 及设备序列号相同,System Firmware 可依此判断出两者同属一个 CXL Device,并进行相关流程或配置上的优化。

跟单 CPU 拓扑相同,采用该双 CPU 拓扑时,允许 CXL 设备驱动屏蔽其中一个 D0F0,即两个 CPU 中的上层软件只向未屏蔽的 D0F0 提交任务。这在不支持在多 Function 间进行分布式计算的 Accelerator 框架或上层应用的场景中很有必要。即便如此,在不违反编程模型的前提下,eRCD 内的硬件仍能通过任意一个 UP 向 CPU 发 Traffic 或进行 Snoop。为了减少无效的 Snoop,eRCD 加速卡需要能够区分两个 CPU 的系统空间,从而将 Snoop 送到对应的 CPU 域。ACPI SRAT 可以或者这些地址信息并通过 Device 自定义的机制把它告知给 eRCD 加速卡中的设备驱动。

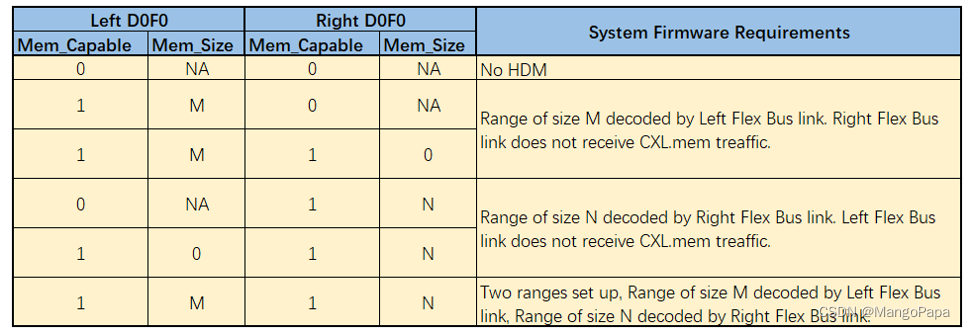

跟单 CPU 拓扑相同,采用该拓扑时,则两个 UP 的 Mem_Capable 能力及 Mem_Size 需求可以独立进行配置并映射到系统地址空间,相关解码规则如下表所示。

根据上表有以下结论:

- 若两个 UP 均支持 CXL.mem 且独立分配了地址空间,则两个链路独立访问各自的 HDM Range;

- 只有支持 CXL.mem 且分配了 HDM 空间的 UP,才能通过其链路访问其 HDM 范围;

- 若两个 UP 均支持 CXL.mem 但只有一个分配了空间,则只有支持 CXL.mem 的链路能够访问其 HDM 范围,另一链路不能访问,也不支持 Interleaving 访问。

Q&A

- 为什么不适用于 VH,为什么不适用于 DSP?

参考

- CXL Base Spec, r3.0

|

|

🔥 精选往期 CXL 协议系列文章,请查看【 CXL 专栏】🔥

⬆️ 返回顶部 ⬆️