视频讲解

[AG32VF407]国产MCU+FPGA Verilog编写控制2路gpio输出不同频率方波实验

实验过程

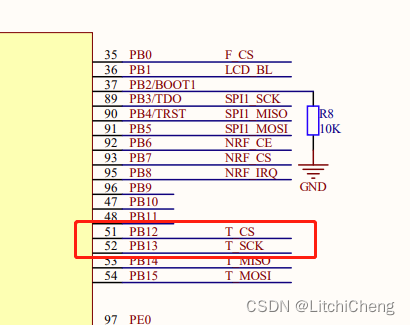

根据原理图,选择两个pin脚作为输出

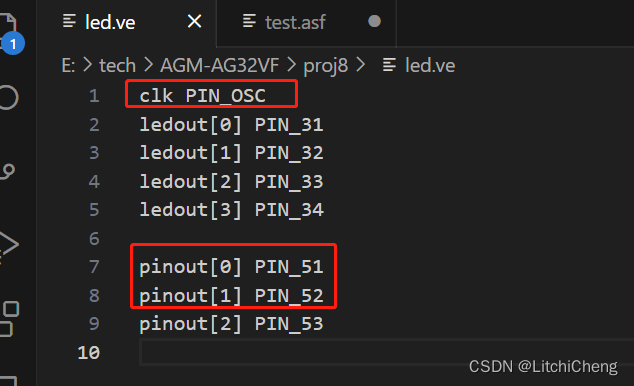

修改VE文件,clk选择PIN_OSC,使用内部晶振8Mhz,gpio使用PIN_51和52,pinout是数组

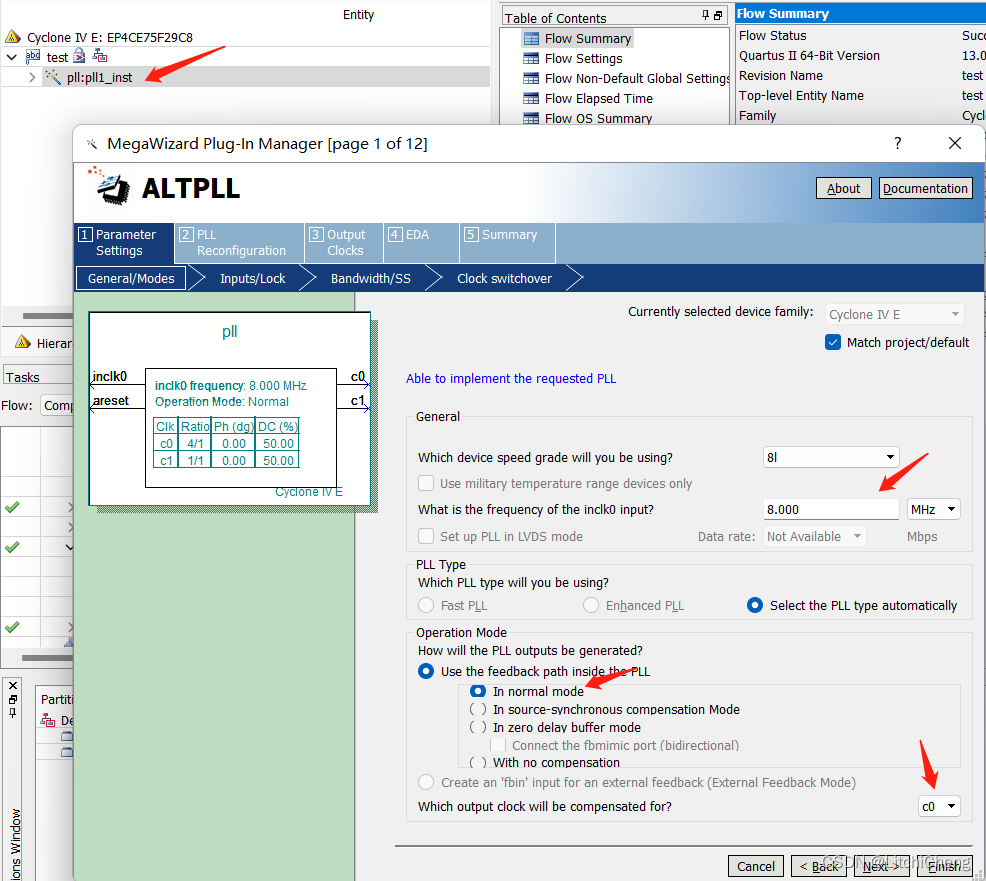

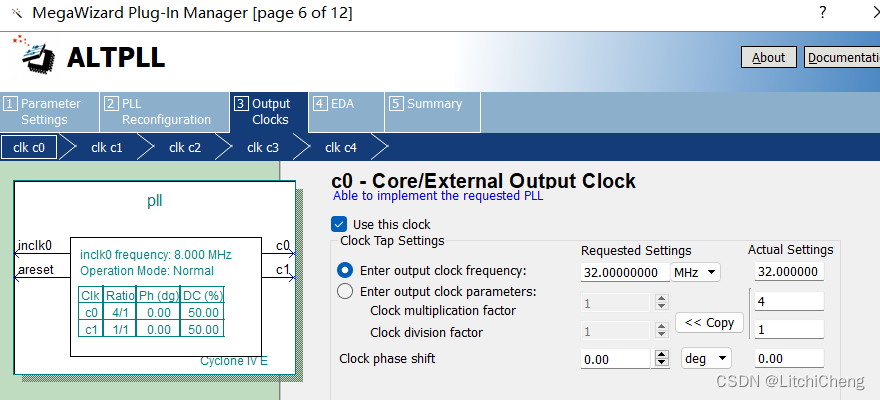

添加pll,修改pll,输入频率8M 输出c0,32Mhz

输出c0,32Mhz

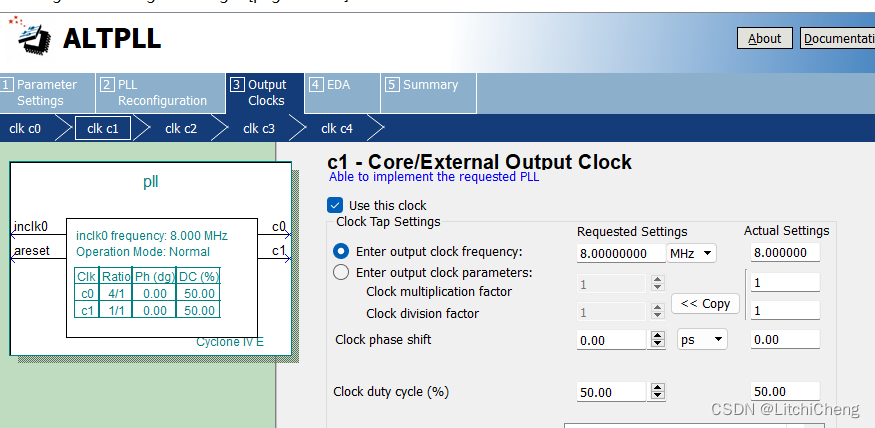

输出c1,8Mhz

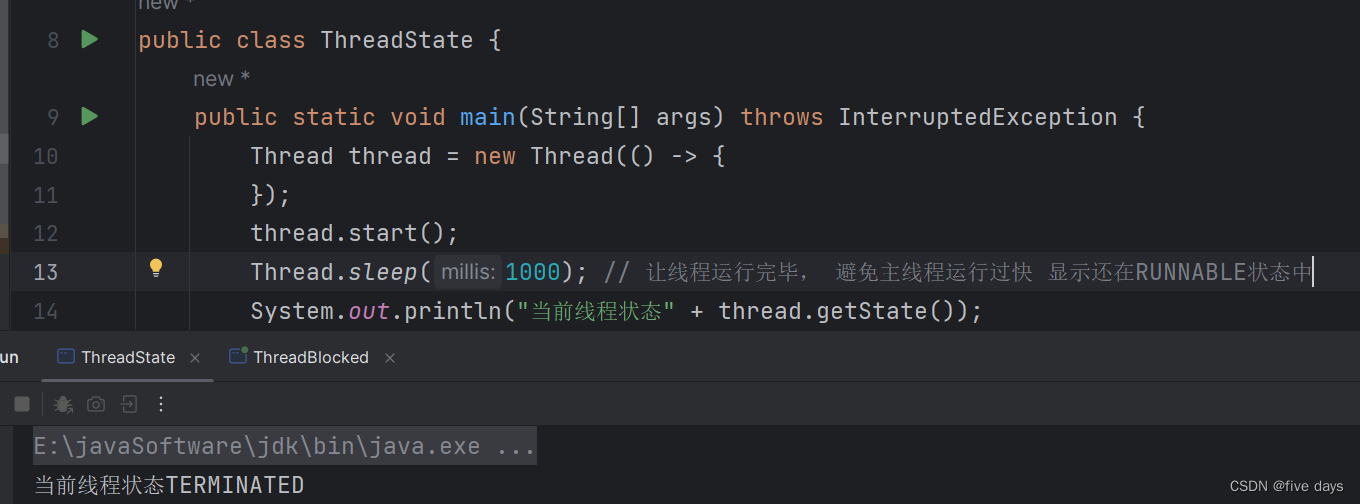

增加verilog逻辑代码,两个always循环,按照c0和c1翻转pin_51和pin_52

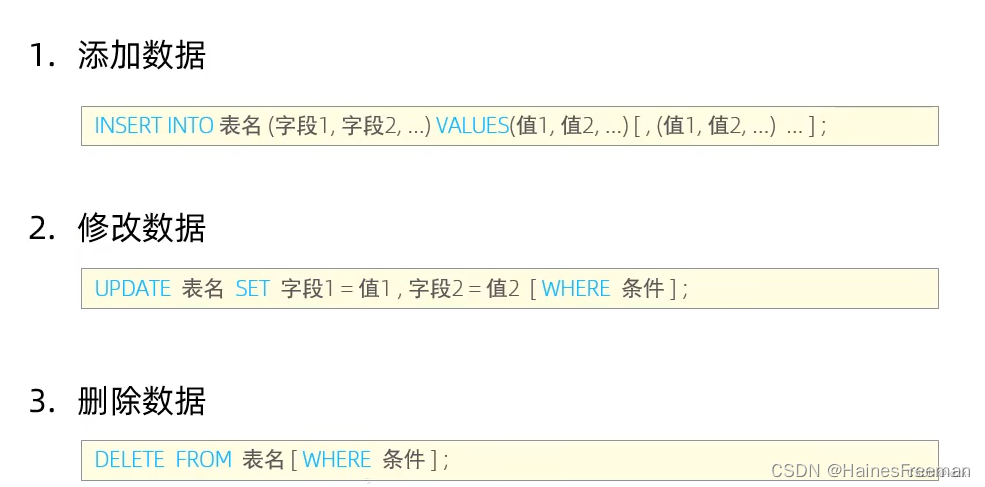

`timescale 1ns / 1ns

module test(clk,pinout);

input clk;

output [2:0] pinout;

reg [2:0] pinout;

pll pll1_inst (

.areset ( 1'b0 ),

.inclk0 ( clk ),

.c0 ( c0 ),

.c1 ( c1 )

);

wire c0;

wire c1;

initial begin

pinout = 3'b111;

end

always@(posedge c0) begin

pinout[0] = ~pinout[0];

end

always@(posedge c1) begin

pinout[1] = ~pinout[1];

end

endmodule

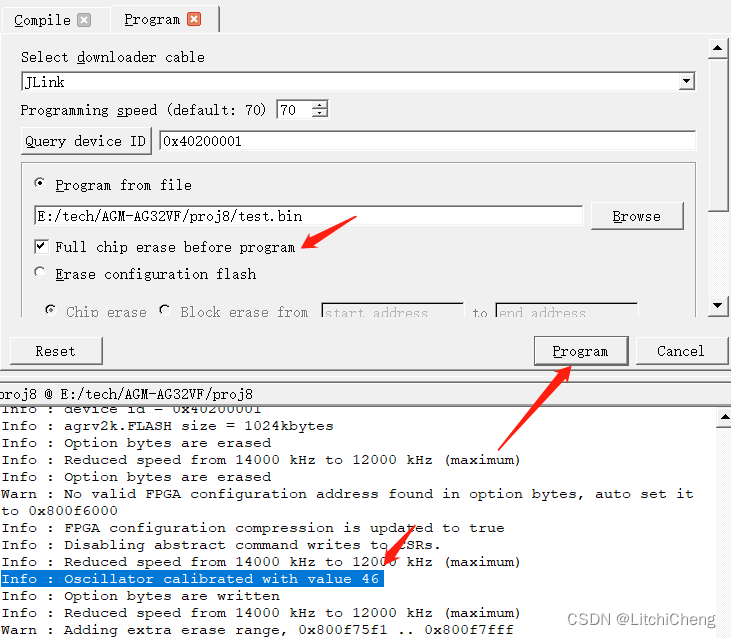

烧录,选择full chip erase before program

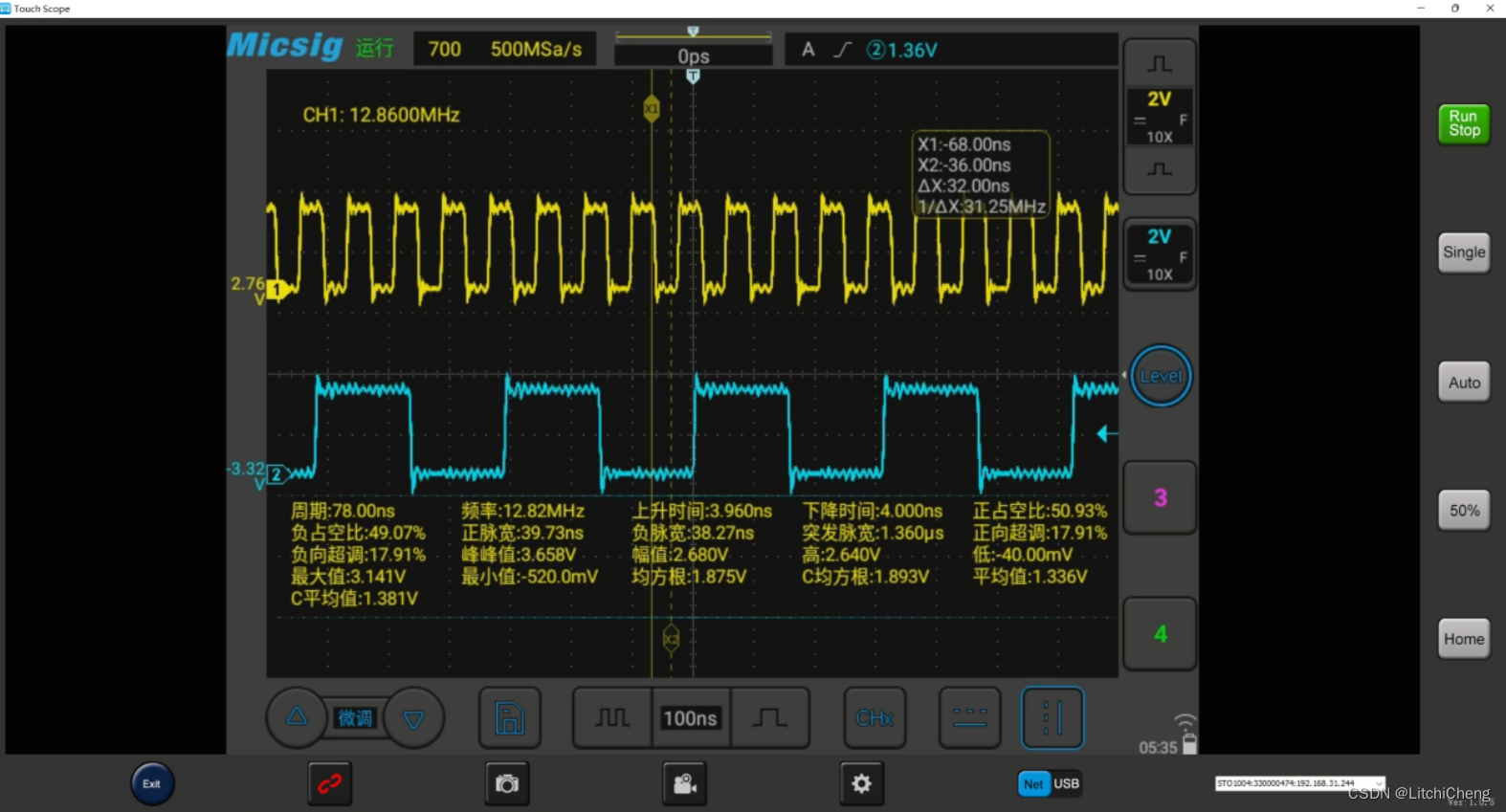

实测波形,这里12Mx2=24M,还有3.2Mx2=6.4M,和实际设置有差异,不确定是内部晶振问题还是配置问题,还需要和AGM进行技术咨询,总体的逻辑是符合预期,调整clock out的比例,波形输出也成比例。

![洛谷P8599 [蓝桥杯 2013 省 B] 带分数](https://img-blog.csdnimg.cn/direct/2012e5afc8034938b4f4e014ebcd1ca8.png)