🌈个人主页:Sarapines Programmer

🔥 系列专栏:《机组 | 模块单元实验》

⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。

目录

一、实验目的

二、实验要求

三、实验说明

四、实验步骤

实验一 不带进位位逻辑或运算实验

实验二 不带进位位加法运算实验

实验三 带进位的加法运算实验

实验四 数据输入通用寄存器

实验五 寄存器内容无进位位左移实验

实验六 寄存器内容无进位位右移实验

实验七 32位ALU实验

实验八 32位寄存器实验

实验九 32位寄存器组实验

实验十 32位程序计数器 PC实验

实验十一 中断控制实验

📝总结

一、实验目的

1、掌握运算器的数据传输方式。

2、掌握74LS181的功能和应用。

3、学习并掌握利用FPGA器件通过原理图进行算术逻辑单元的设计。

二、实验要求

1、完成32位不带进位位算术、逻辑运算实验。按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

2、通过原理图配置EP2C5的内部电路结构,使其替代分离的算术逻辑运算单元的设计。

三、实验说明

1、ALU单元实验构成

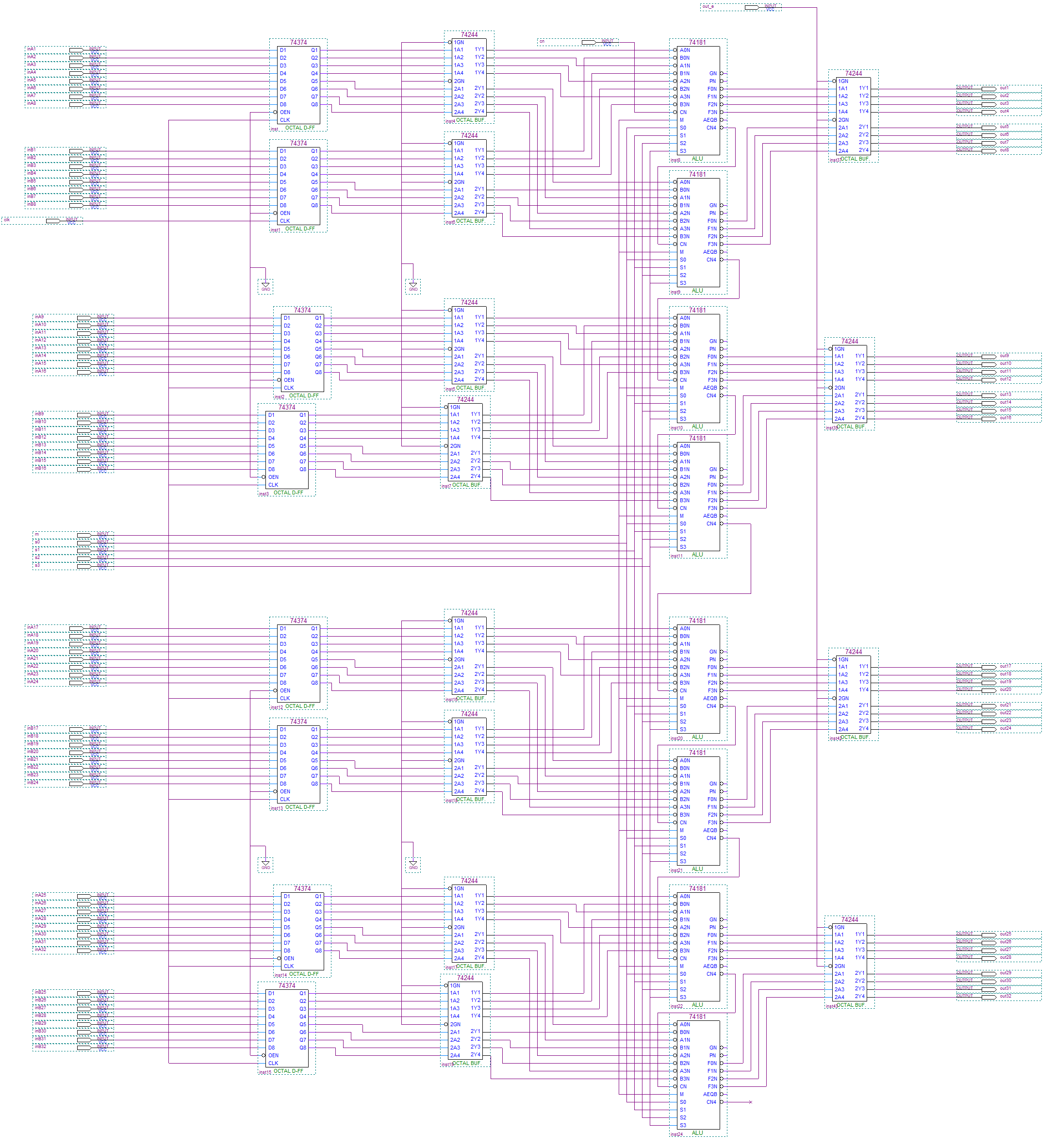

(1)运算器由8片74LS181构成32位字长的ALU单元。

(2)8片74LS374作为数据锁存器,8片74LS244作为数据驱动器,8个8芯插座作为数据输入端,可通过长8芯扁平电缆,把数据输入端连接到二进制开关上。

运算器的数据输出由4片74LS244(输出缓冲器)来控制,4个8芯插座作为数据输出端,由开关控制显示32位输出结果。可通过8芯扁平电缆线把数据输出端连接到微指令LED灯上。

2、ALU单元的工作原理

CLK有上升沿时,把来自数据总线的两路32位数据打入输入锁存器。

算术逻辑运算单元的核心是由8片74LS181组成,它可以进行2个32位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1(对应通道1数据)、DR2(对应通道2的数据)内的数据。由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。

输出缓冲器采用4片74LS244,当控制信号ALU-O为低电平时,两片74LS244导通,把74LS181的运算低位结果输出到数据总线,并在微指令单元LED上显示。

3、控制信号说明

| 信号名称 | 作 用 | 有效电平 |

| CLK | 寄存器工作脉冲 | 上升沿有效 |

| S0~S3 | 74LS181工作方式选择 | 见附表 |

| M | 选择逻辑或算术运算 | 高电平为逻辑运算,低电平为算术运算 |

| CN | 有无进位输入 | 高电平有效 |

| CLK | 进位寄存器的工作脉冲 | 上升沿有效 |

| ALU-OUT | 74LS181计算结果16位输出至总线 | 低电平有效 |

四、实验步骤

实验一 不带进位位逻辑或运算实验

将右板中间的计算机组成原理连线板拔下,换成8位/16位/32位计算机组成原理与系统结构 扩展板。

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入通道1)。

把IO5(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J3插座相连(对应二进制开关S1~S8);把IO6(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J13插座相连(对应二进制开关S33~S48);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J14插座相连(对应二进制开关S49~S56);把IO14(8芯的盒型插座,FPGA扩展实验区)与母板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23)。(S1~S8,S33~S48,S49~S56,H16~H23为32位数据输入通道2)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

把IO188(CLK)用连线连到脉冲单元的PLS1上作为输入寄存器控制时钟信号。

把IO191(ALU-O)用连线连到二进制单元的H6上作为输出允许控制信号。

把IO193(S3), IO197(S2), IO168(S1), IO164(S0)用连线分别连到二进制单元的H5,H4,H3,H2上用于控制74LS181的工作方式。

把IO162(M)用连线连到二进制单元的H1上用于控制74LS181的算术运算还是逻辑运算。

把IO160(CN)用连线连到二进制单元的H0上用于控制74LS181的带进位还是不带进位。

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入A[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入A[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入A[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入A[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I05(输入B[31:24]位) | J1(扩展板二进制开关S1-S8) |

| I06(输入B[23:16]位) | J13(扩展板二进制开关S33-S48) |

| IO13(输入B[15:8]位) | J14(扩展板二进制开关S49-S56) |

| IO14(输入B[7:0]位) | J01(母板二进制开关H16-H23) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(输出使能ALU-O) | 母板二进制开关H6 |

| IO193(S3), IO197(S2), IO168(S1), IO164(S0) | 母板二进制开关H5,H4,H3,H2 |

| IO162(工作模式选择M) | 母板二进制开关H1 |

| IO160(进位模式选择CN) | 母板二进制开关H0 |

把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验1 不带进位位逻辑或运算\alu32文件夹中的alu32.sof程序下载到FPGA。

二进制开关作为数据输入通道1,置33333333H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

二进制开关作为数据输入通道2,置55555555H(对应开关如下表)。

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | 数据总线值 |

| B31 | B30 | B29 | B28 | B27 | B26 | B25 | B24 | B[31:24]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| S33 | S34 | S35 | S36 | S37 | S38 | S39 | S48 | 数据总线值 |

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | B[23:16]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| S49 | S50 | S51 | S52 | S53 | S54 | S55 | S56 | 数据总线值 |

| B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B[15:8]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| H23 | H22 | H21 | H20 | H19 | H18 | H17 | H16 | 数据总线值 |

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | B[7:0]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

置各控制信号如下:

| H6 | H5 | H4 | H3 | H2 | H1 | H0 |

| ALU-0 | S3 | S2 | S1 | S0 | M | CN |

| 0 | 1 | 1 | 1 | 0 | 1 | 0 |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿,把33333333H以及55555555H打入输入数据锁存器。

经过74LS181的计算,把运算结果(F=A或B)输出到数据总线上,数据总线上的LED灯显示灯显示77777777H。

实验二 不带进位位加法运算实验

将右板中间的计算机组成原理连线板拔下,换成8位/16位/32位计算机组成原理与系统结构 扩展板。

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入通道1)。

把IO5(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J1插座相连(对应二进制开关S1~S8);把IO6(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J13插座相连(对应二进制开关S33~S48);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J14插座相连(对应二进制开关S49~S56);把IO14(8芯的盒型插座,FPGA扩展实验区)与母板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23)。(S1~S8,S33~S48,S49~S56,H16~H23为32位数据输入通道2)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

把IO188(CLK)用连线连到脉冲单元的PLS1上作为输入寄存器控制时钟信号。

把IO191(ALU-O)用连线连到二进制单元的H6上作为输出允许控制信号。

把IO193(S3), IO197(S2), IO168(S1), IO164(S0)用连线分别连到二进制单元的H5,H4,H3,H2上用于控制74LS181的工作方式。

把IO162(M)用连线连到二进制单元的H1上用于控制74LS181的算术运算还是逻辑运算。

把IO160(CN)用连线连到二进制单元的H0上用于控制74LS181的带进位还是不带进位。

把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验2 不带进位加法运算\alu32文件夹中的alu32.sof程序下载到FPGA。

二进制开关作为数据输入通道1,置33333333H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 33H |

二进制开关作为数据输入通道2,置55555555H(对应开关如下表)。

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | 数据总线值 |

| B31 | B30 | B29 | B28 | B27 | B26 | B25 | B24 | B[31:24]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| S33 | S34 | S35 | S36 | S37 | S38 | S39 | S48 | 数据总线值 |

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | B[23:16]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| S49 | S50 | S51 | S52 | S53 | S54 | S55 | S56 | 数据总线值 |

| B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B[15:8]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

| H23 | H22 | H21 | H20 | H19 | H18 | H17 | H16 | 数据总线值 |

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | B[7:0]位数据 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 55H |

置各控制信号如下:

| H6 | H5 | H4 | H3 | H2 | H1 | H0 |

| ALU-0 | S3 | S2 | S1 | S0 | M | CN |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿,把33333333H及55555555H打入输入数据锁存器。

经过74LS181的计算,把运算结果(F=A+B)输出到数据总线上,数据总线上的LED显示灯应该显示88888888H。

附74LS181的逻辑(改变程序可设置不同的工作方式)

| 方式 | M=1逻辑运算 | M=0算术运算 | |

| S3 S2 S1 S0 | 逻辑运算 | CN=1(无进位) | CN=0(有进位) |

| 0000 | F=/A | F=A | F=A加1 |

| 0001 | F=/(A+B) | F=A+B | F=(A+B)加1 |

| 0010 | F=/A B | F=A+/B | F=(A+/B)加1 |

| 0011 | F=0 | F=减1(2的补) | F=0 |

| 0100 | F=/(AB) | F=A加A/B | F=A加A/B加1 |

| 0101 | F=/B | F=(A+B)加A/B | F=(A+B)加A/B加1 |

| 0110 | F=A⊕B | F=A减B减1 | F=A减B |

| 0111 | F=A /B | F=A/B减1 | F=A/B |

| 1000 | F=/A+B | F=A 加AB | F=A 加AB加 1 |

| 1001 | F= /(A⊕B ) | F=A加B | F=A加B加1 |

| 1010 | F=B | F=(A+/B)加AB | F=(A+/B)加AB加1 |

| 1011 | F=AB | F=AB减1 | F=AB |

| 1100 | F=1 | F=A加 A | F=A加 A 加1 |

| 1101 | F=A+/B | F=(A+B) 加 A | F=(A+B) 加 A 加1 |

| 1110 | F=A+B | F=(A+/B)加A | F=(A+/B)加A加1 |

| 1111 | F=A | F=A减1 | F=A |

实验三 带进位的加法运算实验

进位电路与通用寄存器、ALU有着非常紧密的关系,算术逻辑单元的进位输出和通用寄存器带进位移动都会影响进位寄存器中的结果。

若实验者在做算术逻辑实验时,选择了算术运算方式,当ALU的计算结果输出至总线时,在CCK上来一个上升沿,将把74LS181的进位输出位(Cn+4)上的值(为了统一进位标识,1表示有进位,0表示无进位),打入进位寄存器中,并且有进位时LED(CY)发光。

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入A[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入A[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入A[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入A[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I05(输入B[31:24]位) | J1(扩展板二进制开关S1-S8) |

| I06(输入B[23:16]位) | J13(扩展板二进制开关S33-S48) |

| IO13(输入B[15:8]位) | J14(扩展板二进制开关S49-S56) |

| IO14(输入B[7:0]位) | J01(母板二进制开关H16-H23) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(输出使能ALU-O) | 母板二进制开关H6 |

| IO193(S3), IO197(S2), IO168(S1), IO164(S0) | 母板二进制开关H5,H4,H3,H2 |

| IO162(工作模式选择M) | 母板二进制开关H1 |

| IO160(进位模式选择CN) | 母板二进制开关H0 |

3.1 控制信号说明

| 信号名称 | 作 用 | 有效电平 |

| CLK | 输入寄存器工作脉冲 | 上升沿有效 |

| S0~S3 | 74LS181工作方式选择 | 见附表 |

| M | 选择逻辑或算术运算 | 低电平为逻辑运算,高电平为算术运算 |

| CN | 有无进位输入 | 高电平有效 |

| ALU-OUT | 74LS181计算结果16位输出至总线 | 低电平有效 |

3.2实验步骤

将右板中间的计算机组成原理连线板拔下,换成8位/16位/32位计算机组成原理与系统结构 扩展板。

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入通道1)。

把IO5(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J1插座相连(对应二进制开关S1~S8);把IO6(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J13插座相连(对应二进制开关S33~S48);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J14插座相连(对应二进制开关S49~S56);把IO14(8芯的盒型插座,FPGA扩展实验区)与母板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23)。(S1~S8,S33~S48,S49~S56,H16~H23为32位数据输入通道2)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

把IO188(CLK)用连线连到脉冲单元的PLS1上作为输入寄存器控制时钟信号。

把IO191(ALU-O)用连线连到二进制单元的H6上作为输出允许控制信号。

把IO193(S3), IO197(S2), IO168(S1), IO164(S0)用连线分别连到二进制单元的H5,H4,H3,H2上用于控制74LS181的工作方式。

把IO163(M)用连线连到二进制单元的H1上用于控制74LS181的算术运算还是逻辑运算。

把IO162(CN)用连线连到二进制单元的H0上用于控制74LS181的带进位还是不带进位。

把IO161(CCK)用连线连到连到脉冲单元的PLS4上。

把IO160(CY)用连线连到母板微指令单元M15上,作为进位输出指示。

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入A[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入A[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入A[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入A[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I05(输入B[31:24]位) | J1(扩展板二进制开关S1-S8) |

| I06(输入B[23:16]位) | J13(扩展板二进制开关S33-S48) |

| IO13(输入B[15:8]位) | J14(扩展板二进制开关S49-S56) |

| IO14(输入B[7:0]位) | J01(母板二进制开关H16-H23) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(输出使能ALU-O) | 母板二进制开关H6 |

| IO193(S3), IO197(S2), IO168(S1), IO164(S0) | 母板二进制开关H5,H4,H3,H2 |

| IO163(工作模式选择M) | 母板二进制开关H1 |

| IO162(进位模式选择CN) | 母板二进制开关H0 |

| IO161(CCK) | 时序单元PLS4 |

| IO160(进拉输出CY) | 微指令单元M15 |

将右板中间的计算机组成原理连线板拔下,把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验3 带进位位的加法运算\alu32文件夹中的alu32.sof程序下载到FPGA。

二进制开关作为数据输入通道1,置65656565H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 65H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 65H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 65H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 65H |

二进制开关作为数据输入通道2,置A7A7A7A7H(对应开关如下表)。

| S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | 数据总线值 |

| B31 | B30 | B29 | B28 | B27 | B26 | B25 | B24 | B[31:24]位数据 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | A7H |

| S33 | S34 | S35 | S36 | S37 | S38 | S39 | S48 | 数据总线值 |

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | B[23:16]位数据 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | A7H |

| S49 | S50 | S51 | S52 | S53 | S54 | S55 | S56 | 数据总线值 |

| B15 | B14 | B13 | B12 | B11 | B10 | B9 | B8 | B[15:8]位数据 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | A7H |

| H23 | H22 | H21 | H20 | H19 | H18 | H17 | H16 | 数据总线值 |

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 | B[7:0]位数据 |

| 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | A7H |

置各控制信号如下:

| H6 | H5 | H4 | H3 | H2 | H1 | H0 |

| ALU-0 | S3 | S2 | S1 | S0 | M | CN |

| 0 | 1 | 0 | 0 | 1 | 0 | 1 |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿的脉冲,把65656565H及A7A7A7A7H打入输入数据锁存器。

按脉冲单元中的PLS4脉冲按键,在CCK上产生一个上升沿,把74LS181的进位打入进位寄存器中,在有进位的情况下,CY指示灯M15亮,并且数据总线上的LED显示灯应该显示0D0D0D0CH。

实验四 数据输入通用寄存器

一、实验目的

了解通用32位寄存器的组成和硬件电路,利用通用寄存器实现数据的置数、左移、右移等功能。

二、实验要求

按照实验步骤完成实验项目, 实现通用寄存器移位操作。了解通用寄存器单元的工作原理运用。

三、实验说明

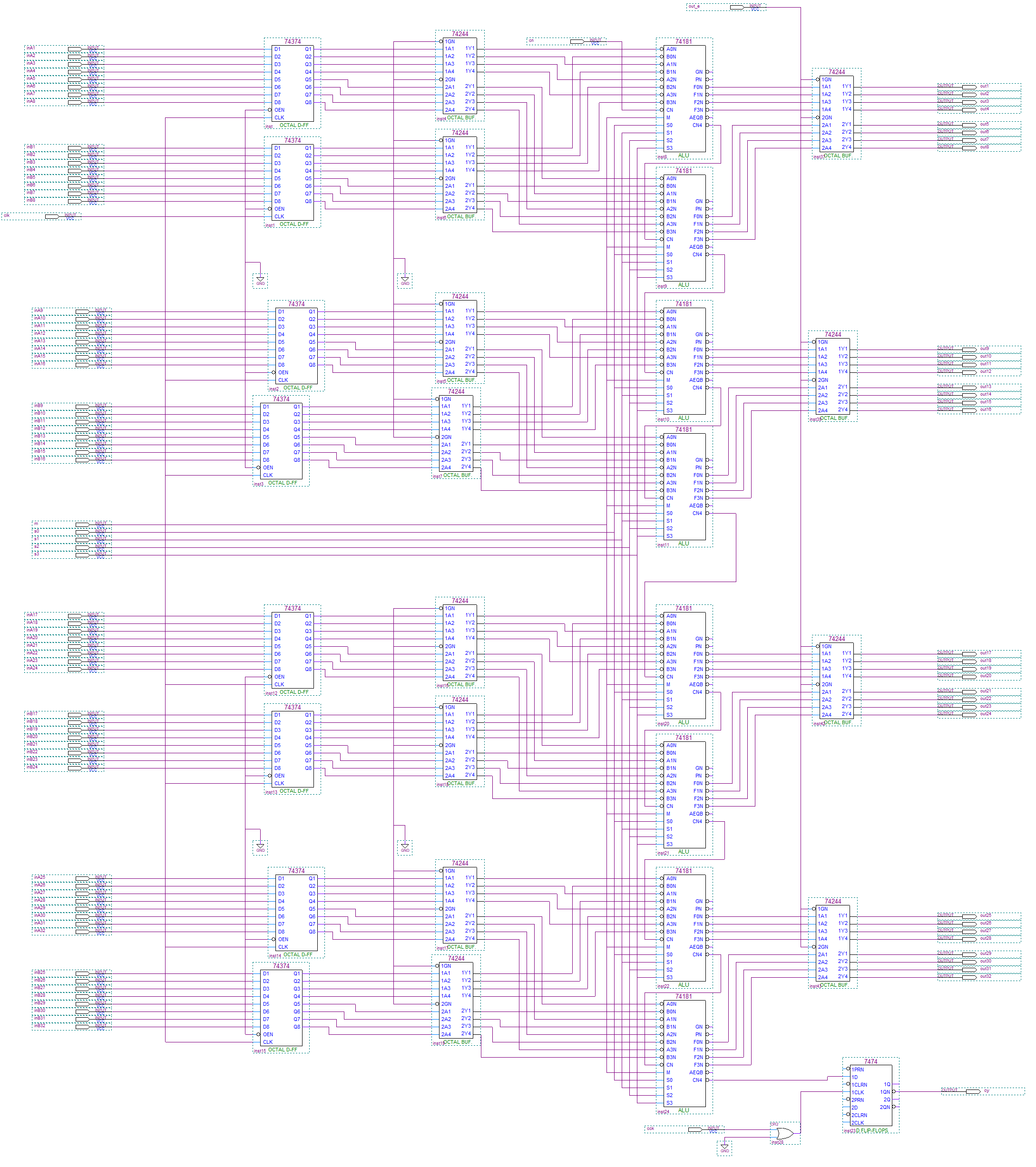

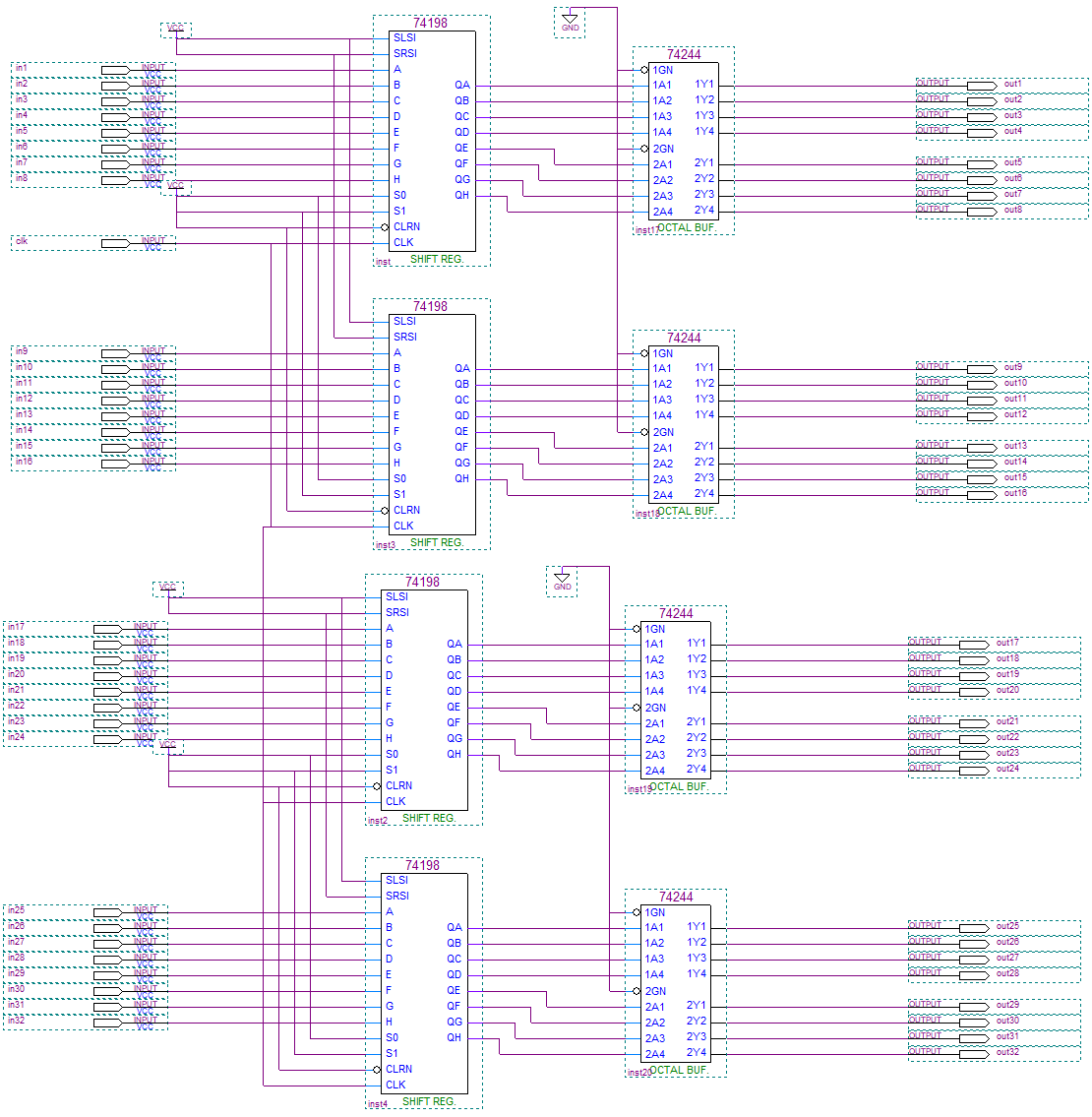

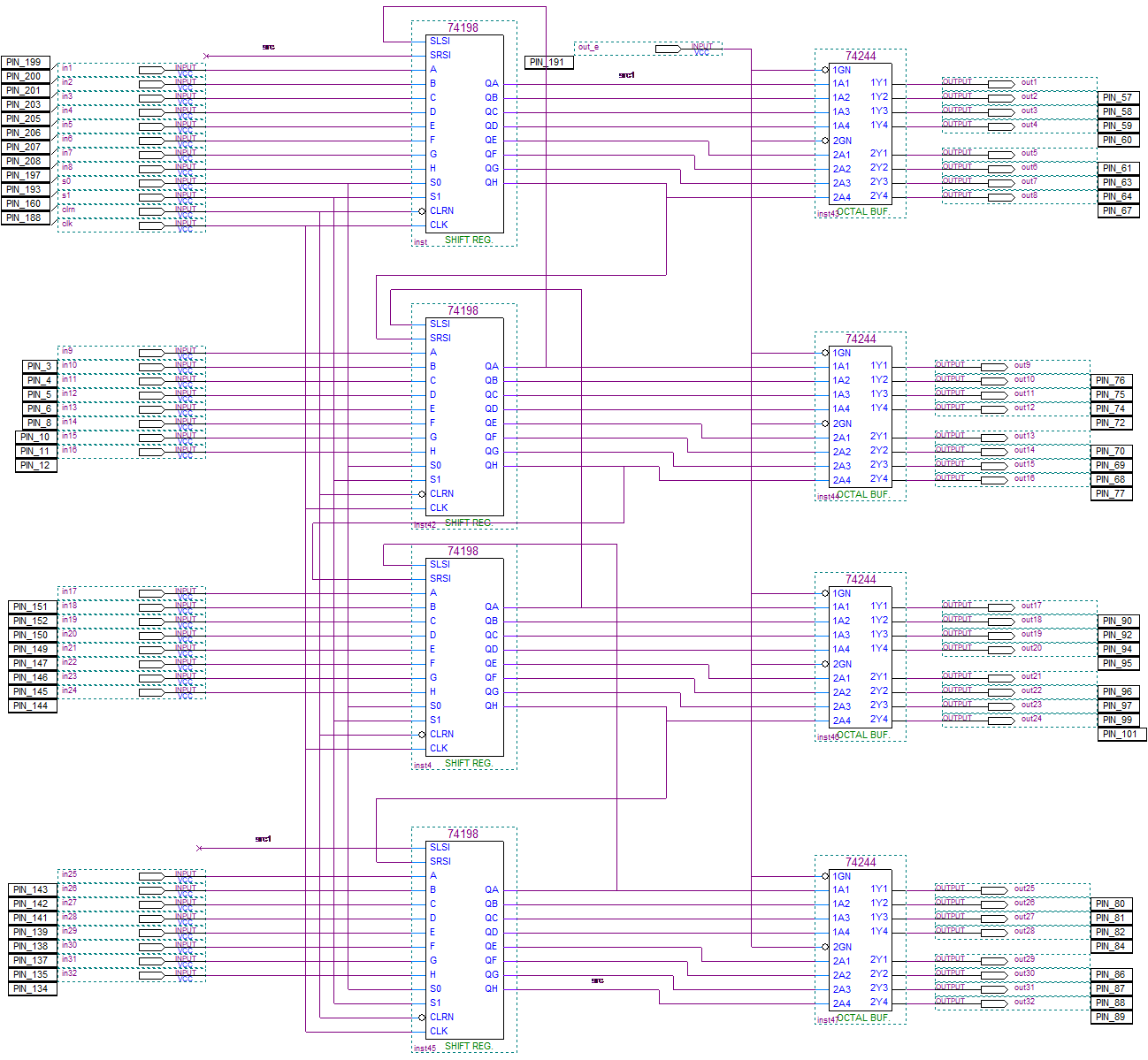

1、寄存器实验构成:

通用寄存器由4片74LS198构成32位字长的寄存器单元。四个8芯插座作为数据输入端,可通过8芯数据电缆,把数据输入端连接到二进制开关总线上。

数据输出由4片74LS244(输出缓冲器)来控制。用32个FPGA IO作为数据输出端,通过32根数据线连接到微指令的LED灯上。

2、通用寄存器单元的工作原理

通用寄存器单元的核心部件为4片74LS198,它具有锁存、左移、右移、保存等功能。各个功能都由X1、X2信号和工作脉冲CLK来决定。X0=1、X1=1,CLK有上升沿时,把总线上的数据打入通用寄存器。可通过设置X0、X1来指定通用寄存器工作方式。

输出缓冲器采用74LS244,把通用寄存器内容输出到总线。

3、控制信号说明

| 信号名称 | 作 用 | 有效电平 |

| CLK | 通用寄存器工作脉冲 | 上升沿有效 |

四、实验步骤

将右板中间的计算机组成原理连线板拔下,换成8位/16位/32位计算机组成原理与系统结构 扩展板。

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188,用数据线与左板二进制开关单元PLS1连接,对应74LS198CLK时钟控制信号。

将FPGA扩展板接口IO193,用数据线与扩展板H57连接。

本实验增加了数码管显示输入输出寄存器功能,若要数码管与二进制LED灯同时显示,请进行如下连接:

将将FPGA扩展板接口IO5与扩展板J9相连,IO6与J6相连,IO13与J7相连,IO14与J8相连。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入A[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入A[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入A[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入A[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| IO5(输入数码管数据) | J9 |

| IO6(输出数码管扫描选通) | J6 |

| IO13(输出数码管数据) | J7 |

| IO14(输入数码管扫描选通) | J8 |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO193(数码管复位) | H57 |

把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验4 数据输入通用寄存器文件夹中的regist32.sof程序下载到CPLD。

二进制开关作为数据输入通道,置42424242H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿,把42424242H打入通用寄存器,此时微指令总线上的指示灯应该显示为42424242H。

实验五 寄存器内容无进位位左移实验

一、通用寄存器单元的工作原理:

通用寄存器单元的核心部件为4片74LS198,它具有锁存、左移、右移、保存等功能。各个功能都由X1、X2信号和工作脉冲CLK来决定。X0=1、X1=1,CLK有上升沿时,把总线上的数据打入通用寄存器。可通过设置X0、X1来指定通用寄存器工作方式。

输出缓冲器采用74LS244,,把通用寄存器内容输出到总线。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188,用数据线与右板二进制开关单元PLS1连接,对应74LS198CLK时钟控制信号。

将FPGA扩展板接口IO191,用数据线与右板二进制开关单元H3连接,对应74LS198输出控制信号。

将FPGA扩展板接口IO193,用数据线与右板二进制开关单元H2连接,对应74LS198X1控制信号。

将FPGA扩展板接口IO197,用数据线与右板二进制开关单元H1连接,对应74LS198X0控制信号。

将FPGA扩展板接口IO160,用数据线与左板二进制开关单元H0连接,对应74LS198CLR清0控制信号。

将FPGA扩展板接口IO162,用数据线与H57连接,对应74LS198CLK时钟控制信号。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| I0188(寄存器工作脉冲) | 时序单元PLS1 |

| I0191(OUT) | H3(二进制开关) |

| I0193(X1) | H2(二进制开关) |

| I0197(X0) | H1(二进制开关) |

| I0160(CLR) | H0(二进制开关) |

| IO162(nRST) | H57 |

把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验5 寄存器内容无进位位左移文件夹中的regist32.sof程序下载到FPGA。

二进制开关作为数据输入通道,置42424242H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

置各控制信号如下:

| H3 | H2 | H1 | H0 |

| OUT | X1 | X0 | CLREN |

| 0 | 1 | 1 | 1 |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿,把42424242H打入通用寄存器,此时微指令总线上的指示灯应该显示为42424242H,

再改变各控制信号如下:

| H3 | H2 | H1 | H0 |

| OUT | X1 | X0 | CLREN |

| 0 | 0 | 1 | 1 |

按脉冲单元中的PLS1脉冲按键,此时总线上的LED指示灯应该显示84848484H。

再按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值左移,此时总线上的LED指示灯应该显示为09090909H。若一直按PLS1,在总线上将看见数据循环左移的现象。

实验六 寄存器内容无进位位右移实验

一、通用寄存器单元的工作原理:

通用寄存器单元的核心部件为4片74LS198,它具有锁存、左移、右移、保存等功能。各个功能都由X1、X2信号和工作脉冲CLK来决定。X0=1、X1=1,CLK有上升沿时,把总线上的数据打入通用寄存器。可通过设置X0、X1来指定通用寄存器工作方式。

输出缓冲器采用74LS244,,把通用寄存器内容输出到总线。

控制信号说明

| 信号名称 | 作 用 | 有效电平 |

| X0、X1 | 通用寄存器的工作模式 | 见附表 |

| OUT | 16位输出控制信号 | 低电平 |

| CLK | 通用寄存器工作脉冲 | 上升延有效 |

二、实验步骤

将右板中间的计算机组成原理连线板拔下,换成8位/16位/32位计算机组成原理与系统结构 扩展板。

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188,用数据线与右板二进制开关单元PLS1连接,对应74LS198CLK时钟控制信号。

将FPGA扩展板接口IO191,用数据线与右板二进制开关单元H3连接,对应74LS198输出控制信号。

将FPGA扩展板接口IO193,用数据线与右板二进制开关单元H2连接,对应74LS198X1控制信号。

将FPGA扩展板接口IO197,用数据线与右板二进制开关单元H1连接,对应74LS198X0控制信号。

将FPGA扩展板接口IO160,用数据线与左板二进制开关单元H0连接,对应74LS198CLR清0控制信号。

将FPGA扩展板接口IO162,用数据线与H57连接,对应74LS198CLK时钟控制信号。实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出[31:24]位) | J3(扩展板L17-L24) |

| I08(输出[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出[7:0]位) | M04(母板L1-L8) |

| I0188(寄存器工作脉冲) | 时序单元PLS1 |

| I0191(OUT) | H3(二进制开关) |

| I0193(X1) | H2(二进制开关) |

| I0197(X0) | H1(二进制开关) |

| I0160(CLR) | H0(二进制开关) |

| IO162(nRST) | H57 |

把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验6 寄存器内容无进位位右移文件夹中的regist32.sof程序下载到FPGA。

二进制开关作为数据输入,置42424242H(对应开关如下表)。

| S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | 数据总线值 |

| A31 | A30 | A29 | A28 | A27 | A26 | A25 | A24 | A[31:24]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | 数据总线值 |

| A23 | A22 | A21 | A20 | A19 | A18 | A17 | A16 | A[23:16]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 | 数据总线值 |

| A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A[15:8]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

| S40 | S41 | S42 | S43 | S44 | S45 | S46 | S47 | 数据总线值 |

| A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | A[7:0]位数据 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 42H |

置各控制信号如下:

| H3 | H2 | H1 | H0 |

| OUT | X1 | X0 | CLREN |

| 0 | 1 | 1 | 1 |

按脉冲单元中的PLS1脉冲按键,在CLK上产生一个上升沿,把42424242H打入通用寄存器,此时微指令总线上的指示灯应该显示为42424242H,

再改变各控制信号如下:

| H3 | H2 | H1 | H0 |

| OUT | X1 | X0 | CLREN |

| 0 | 1 | 0 | 1 |

按脉冲单元中的PLS1脉冲按键,此时总线上的LED指示灯应该显示为21212121H。

按脉冲单元中的PLS1脉冲按键,使通用寄存器中的值右移,此时总线上的LED指示灯应该显示为90909090H。若一直按PLS1,在总线上将看见数据循环右移的现象。

附:通用寄存器的逻辑

通用寄存器(8位并入并出移位寄存器)

| CLR | X1 X0 | CLK | SL SR | QA~AH |

| 0 | X X | X | X X | 全 0 |

| 1 | X X | 0 | X X | 保持不变 |

| 1 | 1 1 | 上升沿 | X X | 并行接数A~H |

| 1 | 0 1 | 上升沿 | X 0 | 右移 移入0 |

| 1 | 0 1 | 上升沿 | X 1 | 右移 移入1 |

| 1 | 1 0 | 上升沿 | 0 X | 左移 移入0 |

| 1 | 1 0 | 上升沿 | 1 X | 左移 移入1 |

实验七 32位ALU实验

一、实验要求

用扩展实验板上的开关做为输入,二进制开关及八段数码管做为输出。用VHDL语言编写程序下载到EP2C5Q08中实现32位模型机的ALU功能。

了解32位模型机中算术逻辑运算单元ALU的工作原理和实现方法。学习用VHDL语言描述硬件逻辑,学习使用EDA开发环境。

二、实验目的

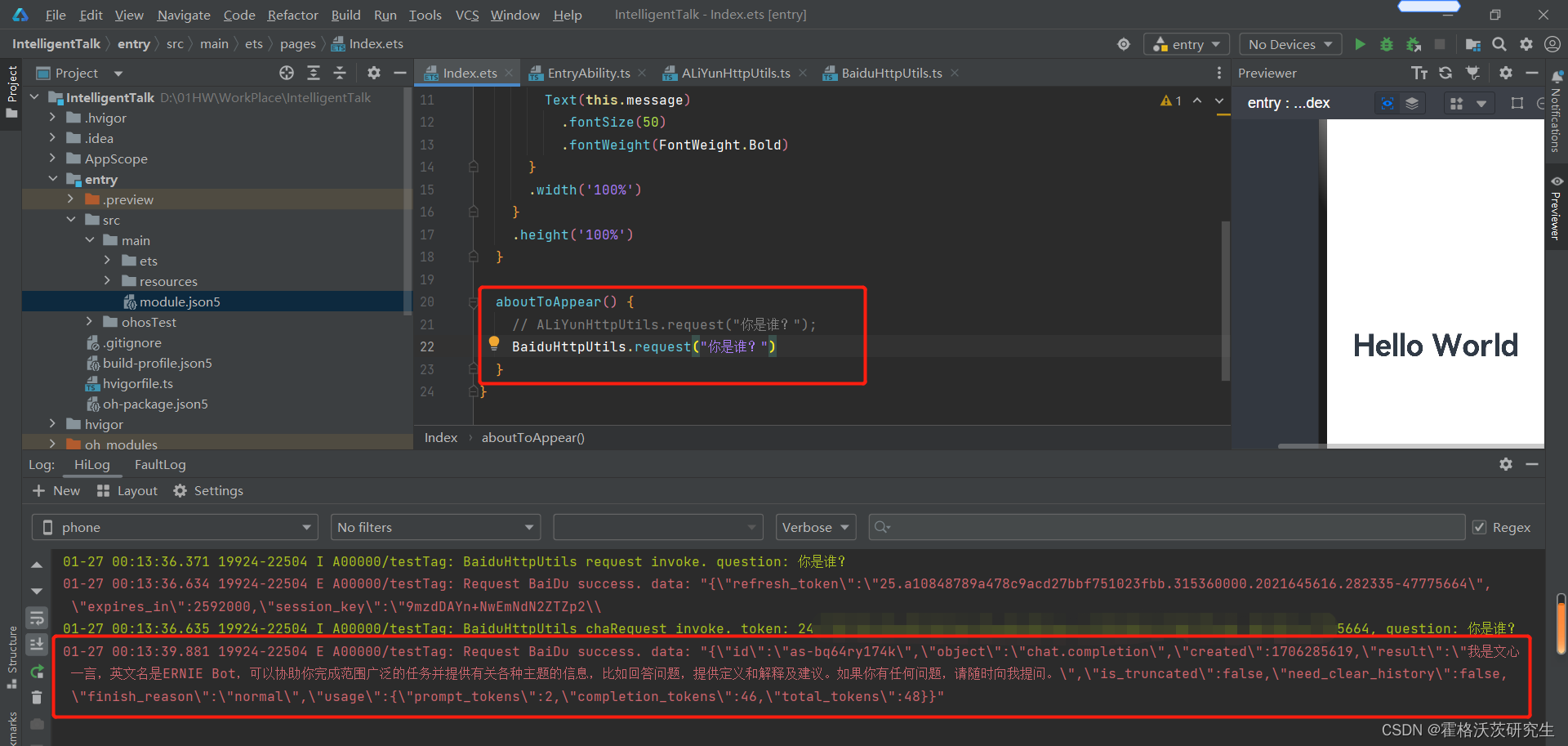

32位ALU的VHDL:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY alu32 IS

PORT (

A : IN STD_LOGIC_VECTOR(32 DOWNTO 1);

W : IN STD_LOGIC_VECTOR(32 DOWNTO 1);

S0 : IN STD_LOGIC;

S1 : IN STD_LOGIC;

S2 : IN STD_LOGIC;

D : OUT STD_LOGIC_VECTOR(32 DOWNTO 1);

CIn : IN STD_LOGIC;

COut : OUT STD_LOGIC

);

END alu32;

ARCHITECTURE behv OF alu32 IS

SIGNAL T: STD_LOGIC_VECTOR(33 DOWNTO 1);

BEGIN

T <= ('0' & A) + ('0' & W) WHEN S2 = '0' AND S1 = '0' AND S0 = '0' ELSE

('0' & A) - ('0' & W) WHEN S2 = '0' AND S1 = '0' AND S0 = '1' ELSE

('0' & A) OR ('0' & W) WHEN S2 = '0' AND S1 = '1' AND S0 = '0' ELSE

('0' & A) AND ('0' & W) WHEN S2 = '0' AND S1 = '1' AND S0 = '1' ELSE

('0' & A) + ('0' & W) + CIn WHEN S2 = '1' AND S1 = '0' AND S0 = '0' ELSE

('0' & A) - ('0' & W) - CIn WHEN S2 = '1' AND S1 = '0' AND S0 = '1' ELSE

NOT ('0' & A) WHEN S2 = '1' AND S1 = '1' AND S0 = '0' ELSE

('0' & A);

D <= T(32 DOWNTO 1);

COut <= T(33);

END behv;

在上面程序中A为累加器,W为工作寄存器,均为32位寄存器。W的值由扩展板上J1,J13,J14及母板上J01对应的四组开关共32位输入,显示在对应的二进制LED灯上。A的值由扩展板J2,J4,J5,J10对应的四组二进制开关输入。S0 S1 S2为运算控制位,根据S0 S1 S2 的不同,ALU实现的功能参见下表。D为运算结果输出显示在扩展板J3,J11,J12及母板M04开关组对应的32位二进制LED上, CIn为进位输入, COut为进位输出。

| S2 | S1 | S0 | ALU实现的功能 |

| 0 | 0 | 0 | 运算结果为A加W |

| 0 | 0 | 1 | 运算结果为A减W |

| 0 | 1 | 0 | 运算结果为A逻辑或W |

| 0 | 1 | 1 | 运算结果为A逻辑与W |

| 1 | 0 | 0 | 运算结果为A加W加进位 |

| 1 | 0 | 1 | 运算结果为A减W减进位 |

| 1 | 1 | 0 | 运算结果为A取反 |

| 1 | 1 | 1 | 运算结果为A(A直接输出) |

四、实验步骤

1 连线

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入通道1)。

把IO5(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J1插座相连(对应二进制开关S1~S8);把IO6(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J13插座相连(对应二进制开关S33~S48);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J14插座相连(对应二进制开关S49~S56);把IO14(8芯的盒型插座,FPGA扩展实验区)与母板上的二进制开关单元中J01插座相连(对应二进制开关H16~H23)。(S1~S8,S33~S48,S49~S56,H16~H23为32位数据输入通道2)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

把IO191(S2)用连线连到二进制单元的H7上。把IO193(S1)用连线连到二进制单元的H6上。把IO197(S0)用连线连到二进制单元的H5上。

把IO168(CIn)用连线连到母板二进制单元的H4上。

把IO164(Cout)用连线连到母板微指令单元的M7上。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入A[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入A[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入A[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入A[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I05(输入W[31:24]位) | J1(扩展板二进制开关S1-S8) |

| I06(输入W[23:16]位) | J13(扩展板二进制开关S33-S48) |

| IO13(输入W[15:8]位) | J14(扩展板二进制开关S49-S56) |

| IO14(输入W[7:0]位) | J01(母板二进制开关H16-H23) |

| I07(输出D[31:24]位) | J3(扩展板L17-L24) |

| I08(输出D[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出D[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出D[7:0]位) | M04(母板L1-L8) |

| IO191(S2), IO193(S1), IO197(S0) | 母板二进制开关H7,H6,H5 |

| IO168(进位输入CIn) | 母板二进制开关H4 |

| IO164(进位输出COut) | 母板母板微指令单元M7 |

2.充分理解alu32.VHD。了解模型机中ALU的实现原理。

3.把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验7 32位ALU实验文件夹中的alu32.sof程序下载到FPGA。

4.拨动W对应开关量(扩展板S1-S8,S33-S48,S49-S56,母板H16-H23),输入W值。拨动A对应开关量(扩展板S9-S32, S40-S47),输入A值。拨动H7,H6,H5对应开关,设置运算方式。拨动开关H4,设置进位。观察输入A及W值,观察微指令单元二进制LED指示结果(运算结果)。观察发光二极管L17是否有进位输出。

实验八 32位寄存器实验

一、实验要求

用计算机组成原理与系统结构扩展实验板上的开关做为输入,发光二极光及八段数码管做为输出。用VHDL语言编写程序下载到EP2C5Q208中实现32位模型机的寄存器输入输出功能。

二、实验目的

了解32位模型机中寄存器的工作原理和实现方法。学习用VHDL语言描述硬件逻辑。学习使用EDA开发环境。

三、实验说明

32位寄存器的VHDL:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY reg32_1 IS

PORT (

D : IN STD_LOGIC_VECTOR(32 DOWNTO 1);

R : OUT STD_LOGIC_VECTOR(32 DOWNTO 1);

EN : IN STD_LOGIC;

nRST: IN STD_LOGIC;

CLK: IN STD_LOGIC

);

END reg32_1;

ARCHITECTURE behv OF reg32_1 IS

BEGIN

PROCESS(CLK, nRST, EN)

BEGIN

IF nRST = '0' THEN

R <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (EN = '0') THEN

R <= D;

END IF;

END IF;

END PROCESS;

END behv;

在上面程序中D为输入数据,R为寄存器,均为32位。D的值由扩展板上J2,J4,J5,J10对应的四组开关共32位提供输入,同时显示在DIS9-DIS16八个数码管上。R为内部寄存器,显示在J3,J11,J12,M04对应的二进制LED灯上,同时显示在DIS1-DIS8八个数码管上。EN为寄存器选通信号,RST为复位信号上,CLK为时钟脉冲。

四、实验步骤

1 连线

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入数据)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188(CLK),用数据线与母板二进制开关单元PLS1连接。

将FPGA扩展板接口IO191(EN),用数据线与母板二进制开关单元H7连接。

将FPGA扩展板接口IO193(nRST),用数据线与H57连接。

本实验增加了数码管显示输入输出寄存器功能,若要数码管与二进制LED灯同时显示,请进行如下连接:

将FPGA扩展板接口IO5与扩展板J9相连,IO6与J6相连,IO13与J7相连,IO14与J8相连。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入D[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入D[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入D[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入D[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出R[31:24]位) | J3(扩展板L17-L24) |

| I08(输出R[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出R[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出R[7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(EN) | H7 |

| IO193(nRST) | H57 |

| IO5(输入D数码管数据) | J9 |

| IO6(输出R数码管扫描选通) | J6 |

| IO13(输出R数码管数据) | J7 |

| IO14(输入D数码管扫描选通) | J8 |

2.充分理解reg3_1.VHD。了解模型机中REG的实现原理。

3.把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验8 32位寄存器实验 文件夹中的reg32_1.sof程序下载到FPGA。

4.按下SB1键,输出“复位”信号,观察八位八段管 (R寄存器的输出显示)是否清零;松开SB1。拨动S9-S32,S40-S47(输入数据 D的值),观察八位八段管DIS9-DIS16 (显示D值)的变化。拨动H7正下方对应开关,设置寄存器选通信号“EN”为有效状态(“0”有效),按PLS1键,产生一个时钟信号,观察J3,J11,J12,M04对应的二进制LED灯及DIS1-DIS8八个数码管,看看是否将D的值存入寄存器R中并显示出来。拨动开关组J2,J4,J5,J10改变D的值,再将“EN”置于无效状态(“1”位置),按PLS1键,产生一个时钟信号,观察J3,J11,J12,M04对应的二进制LED灯及DIS1-DIS8八个数码管是否会随着改变。

实验九 32位寄存器组实验

一、实验要求

用计算机组成原理与系统结构扩展实验板上的开关做为输入,发光二极光及八段数码管做为输出。用VHDL语言编写程序下载到EP2C5Q208中实现32位模型机的多个寄存器输入输出功能。

二、实验目的

了解32位模型机中寄存器组的工作原理和实现方法。学习用VHDL语言描述硬件逻辑。学习使用EDA开发环境。

三、实验说明

32位寄存器组的VHDL:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY regs32 IS

PORT (

D : IN STD_LOGIC_VECTOR(32 DOWNTO 1);

R : OUT STD_LOGIC_VECTOR(32 DOWNTO 1);

SA : IN STD_LOGIC;

SB : IN STD_LOGIC;

RD : IN STD_LOGIC;

WR : IN STD_LOGIC;

nRST: IN STD_LOGIC;

CLK: IN STD_LOGIC

);

END regs32;

ARCHITECTURE behv OF regs32 IS

SIGNAL R0, R1, R2, R3: STD_LOGIC_VECTOR(32 DOWNTO 1);

BEGIN

--WIRTE R0、R1、R2、R3

-- R0

PROCESS(CLK,nRST,WR,SA,SB)

BEGIN

IF nRST = '0' THEN

R0 <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (WR = '0') AND (SB = '0') AND (SA = '0') THEN

R0 <= D;

END IF;

END IF;

END PROCESS;

-- R1

PROCESS(CLK,nRST,WR,SA,SB)

BEGIN

IF nRST = '0' THEN

R1 <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (WR = '0') AND (SB = '0') AND (SA = '1') THEN

R1 <= D;

END IF;

END IF;

END PROCESS;

-- R2

PROCESS(CLK,nRST,WR,SA,SB)

BEGIN

IF nRST = '0' THEN

R2 <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (WR = '0') AND (SB = '1') AND (SA = '0') THEN

R2 <= D;

END IF;

END IF;

END PROCESS;

-- R3

PROCESS(CLK,nRST,WR,SA,SB)

BEGIN

IF nRST = '0' THEN

R3 <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (WR = '0') AND (SB = '1') AND (SA = '1') THEN

R3 <= D;

END IF;

END IF;

END PROCESS;

--READ R0、R1、R2、R3

R <= R0 WHEN (SB = '0') AND (SA = '0') AND (RD = '0') ELSE

R1 WHEN (SB = '0') AND (SA = '1') AND (RD = '0') ELSE

R2 WHEN (SB = '1') AND (SA = '0') AND (RD = '0') ELSE

R3 WHEN (SB = '1') AND (SA = '1') AND (RD = '0') ELSE

(OTHERS=>'0');

END behv;

在上面程序中,D为输入32位数据寄存器。D的值由扩展板上J2,J4,J5,J10对应的四组开关共32位提供输入,同时显示在DIS9-DIS16八个数码管上。R0..R3为内部寄存器,R用做内部寄存器显示输出,显示在J3,J11,J12,M04对应的二进制LED灯上,同时显示在DIS1-DIS8八个数码管上。SA、SB为寄存器选择控制信号,RD为寄存器读信号,WR为寄存器写信号,nRST为复位信号,CLK为时钟脉冲。

四、实验步骤

1.连线

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入)。

把IO5(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J9插座相连(对应LED灯,L17-L24);把IO6(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J6插座相连(对应LED灯L42-L57);把IO13(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J7插座相连(对应LED灯,L58-L65),把IO14(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元J8插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188(CLK),用数据线与右板二进制开关单元PLS1连接,对应CLK。

将FPGA扩展板接口IO193(nRST),用数据线与扩展板按键开关H57连接。

将FPGA扩展板接口IO197(SA),用数据线与母板二进制开关单元H7连接。

将FPGA扩展板接口IO168(SB),用数据线与母板二进制开关单元H6连接。

将FPGA扩展板接口IO164(RD),用数据线与母板二进制开关单元H5连接。

将FPGA扩展板接口IO162(WR),用数据线与母板二进制开关单元H4连接。

将将FPGA扩展板接口IO7与扩展板J3相连,IO8与J11相连,IO15与J12相连,IO16与M04相连。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入D[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入D[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入D[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入D[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出R[31:24]位) | J3(扩展板L17-L24) |

| I08(输出R[23:16]位) | J11(扩展板L42-L57) |

| IO15(输出R[15:8]位) | J12(扩展板L58-L65) |

| IO16(输出R[7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO193(nRST) | H57 |

| IO197(SA) | H7 |

| IO168(SB) | H6 |

| IO164(RD) | H5 |

| IO162(WR) | H4 |

| IO5(输入数码管数据) | J9 |

| IO6(输出数码管扫描选通) | J6 |

| IO13(输出数码管数据) | J7 |

| IO14(输入数码管扫描选通) | J8 |

2.充分理解regs32.VHD。了解模型机中REGS的实现原理。

3.把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验9 32位寄存器组实验 文件夹中的regs32.sof程序下载到FPGA。

4.按下SB1键,输出复位信号,观察32位LED显示及八位八段管 (R寄存器的输出显示)是否清零;松开SB1。然后将H5(RD信号)、H4(WR信号)位置成“1”状态,使读写信号都处于无效状态。

5.寄存器组写实验:拨动S9-S32,S40-S47,输入D的值,拨动H7,H6,设成“00”,选择寄存器R0。拨动H4,设置寄存器写信号“WR”为有效状态(0有效),按PLS1键,产生一个时钟信号,将D写入寄存器R0中。拨动S9-S32,S40-S47开关,改变D值,再改变H7,H6,设成01,选择寄存器R1,按PLS1键,产生一个时钟信号,将D存入寄存器R1中。如此将不同的32位数据分别存R0..R3寄存器中;

6.寄存器组读实验:将H4“WR”信号设成“1”,使其无效。将H7,H6拨成“00”,选择寄存器R0。再将H5(“RD”信号)设成“0”,读出R0中的数据并输出到J3,J11,J12,M04对应的发光二极管和八段管DIS1-DIS8上显示。改变H7,H6,选择寄存器R1,读出R1的值并显示出来。如此读出寄存器R2、R3的值,并观察与写入的数据是否相同。

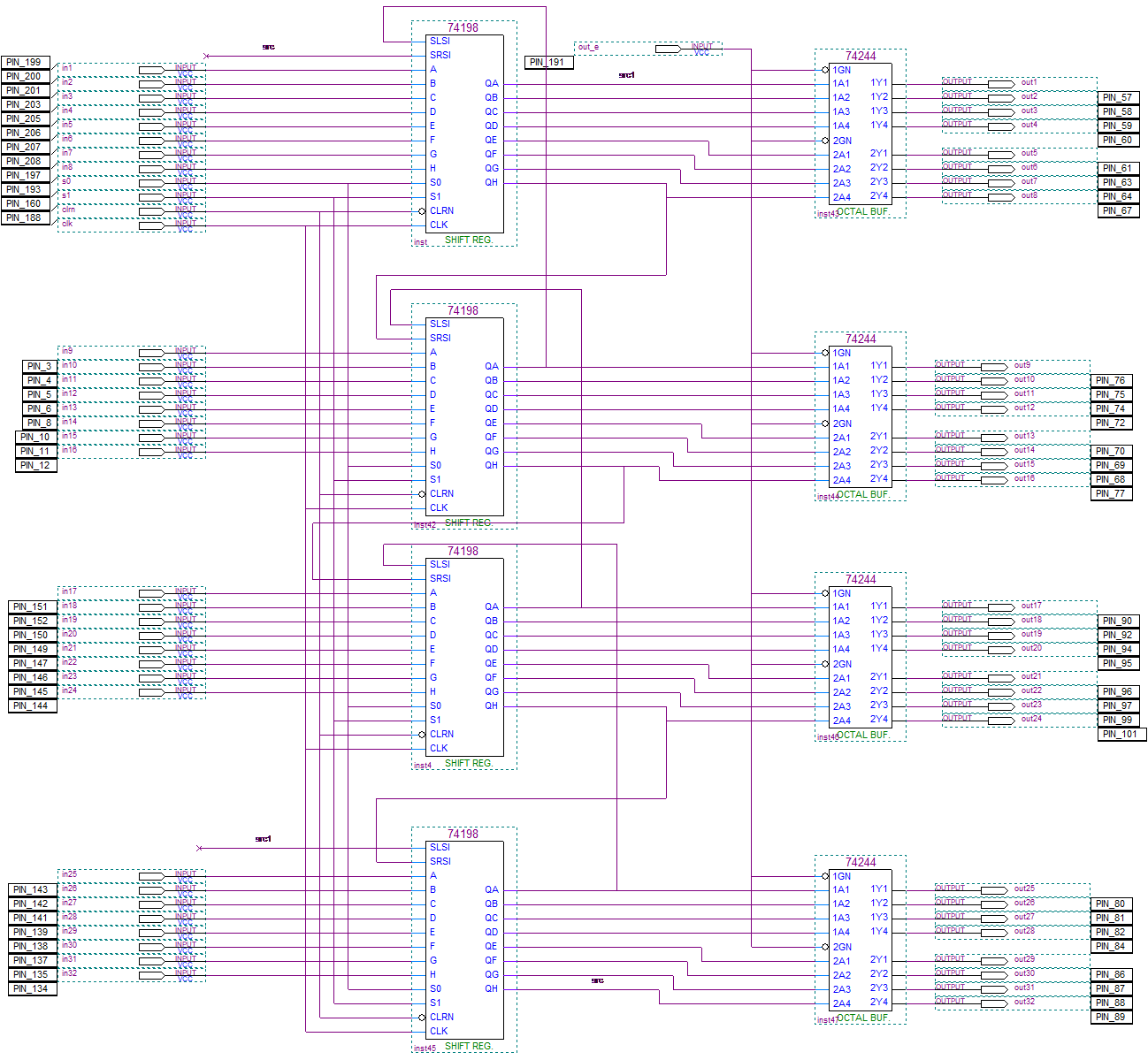

实验十 32位程序计数器 PC实验

一、实验要求

用计算机组成原理与系统结构扩展实验板上的开关做为输入,发光二极光及八段数码管做为输出。用VHDL语言编写程序下载到EP2C5Q208中实现32位模型机的程序计数器功能。

二、实验目的

了解32位模型机中程序计数器PC的工作原理和实现方法。学习用VHDL语言描述硬件逻辑。学习使用EDA开发环境。

三、实验说明

32位程序计数器PC的VHDL:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY pccnt IS

PORT (

D : IN STD_LOGIC_VECTOR(32 DOWNTO 1);

PC : OUT STD_LOGIC_VECTOR(32 DOWNTO 1);

C : IN STD_LOGIC;

Z : IN STD_LOGIC;

ELP : IN STD_LOGIC;

PC_1: IN STD_LOGIC;

IR2 : IN STD_LOGIC;

IR3 : IN STD_LOGIC;

nRST : IN STD_LOGIC;

CLK : IN STD_LOGIC

);

END pccnt;

ARCHITECTURE behv OF pccnt IS

SIGNAL RPC: STD_LOGIC_VECTOR(32 DOWNTO 1);

BEGIN

PC <= RPC;

PROCESS(CLK, nRST, IR3, IR2, C, Z, ELP)

VARIABLE LDPC: STD_LOGIC; -- 转移控制

BEGIN

IF nRST = '1' THEN

RPC <= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK = '1' THEN

IF (ELP = '0') AND (

( (IR3 = '0') AND (IR2 = '0') AND (C = '1') ) OR

( (IR3 = '0') AND (IR2 = '1') AND (Z = '1') ) OR

(IR3 = '1')

) THEN LDPC := '0'; ELSE LDPC := '1';

END IF;

IF LDPC = '0' THEN

RPC <= D;

ELSIF (PC_1 = '1') THEN

RPC <= RPC + 1;

END IF;

END IF;

END PROCESS;

END behv;

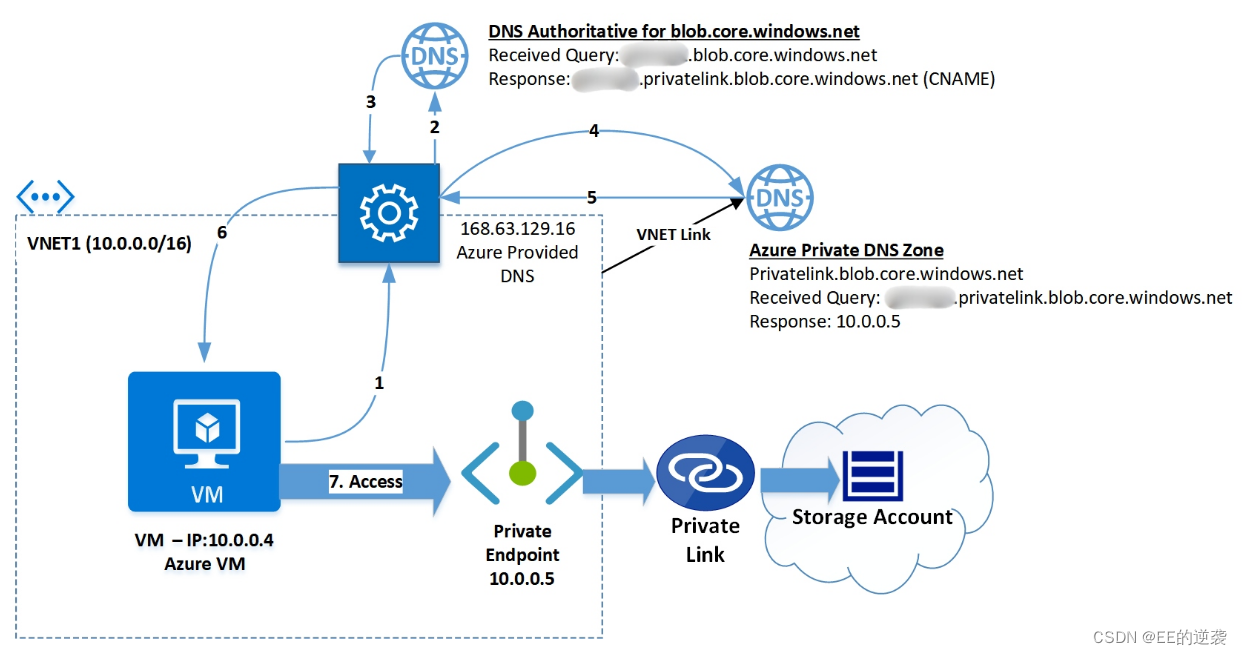

在上面程序中,D为32位输入数据,用于表示跳转条件满足时跳转的目标地址。D的值由扩展板上J2,J4,J5,J10对应的四组开关共32位提供输入,同时显示在DIS9-DIS16八个数码管上。PC为程序计数器,PC显示在J3,J11,J12,M04对应的二进制LED灯上,同时显示在DIS1-DIS8八个数码管上。 C、Z用于模拟模型机中的进位标志和零标志信号。ELP为程序跳转控制信号,为“1”时不允许预置PC;为“0”时根据指令码的第3、2位和C、Z状态来控制程序是否跳转,见下表说明。PC_1表示PC加1控制信号。IR2、IR3表示程序指令的第2位和第3位,在本模型机实验中这两个用于控制程序的跳转。nRST为复位信号,CLK为时钟脉冲。

| ELP() | IR3() | IR2() | C() | Z() | LDPC |

| 1 | x | x | x | x | 1 |

| 0 | 0 | 0 | 1 | x | 0 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | x | 0 | 0 |

| 0 | 0 | 1 | x | x | 1 |

| 0 | 1 | x | x | x | 0 |

上表中LDPC为内部信号,用于控制PC是否能被预置:

当ELP=1时,LDPC=1,不允许PC被预置;

当ELP=0时,LDPC由IR3、IR2、C、Z确定;

当IR3、IR2=1X时,LDPC=0,D的值在CLK上升沿锁存PC,实现程序的JMP直接跳转功能;

当IR3、IR2=00时,LDPC=C取反,当C=1时,D的值在CLK上升沿锁存PC,实现程序的JC有进位跳转功能;

当IR3、IR2=01时,LDPC=Z取反,当Z=1时,D的值在CLK上升沿锁存PC,实现程序的JZ累加器为零跳转功能;

本实验中nRST=0时,程序计数器PC被清0,当LDPC=0时,在CLK上升沿,D的值锁存PC。当PC_1=1 时,在CLK上升沿PC加1。

四、实验步骤

1.连线

把IO1(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J2插座相连(对应二进制开关S9~S16);把IO2(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J4插座相连(对应二进制开关S17~S24);把IO9(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J5插座相连(对应二进制开关S25~S32);把IO10(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的二进制开关单元中J10插座相连(对应二进制开关S40~S47)。(S9~S16,S17~S24,S25~S32,S40~S47为32位数据输入)。

把IO7(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J3插座相连(对应LED灯,L17-L24);把IO8(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上J11插座相连(对应LED灯L42-L57);把IO15(8芯的盒型插座,FPGA扩展实验区)与计算机组成原理与系统结构扩展板上的J12插座相连(对应LED灯,L58-L65),把IO16(8芯的盒型插座,FPGA扩展实验区)与母板上微指令单元M04插座相连(对应微指令LED灯L1-L8),扩展板上L17-L24,L42-L57,L58-L65及母板上L1-L16,为32位数据输出。

将FPGA扩展板接口IO188(CLK),用数据线与右板二进制开关单元PLS1连接,对应CLK。

将FPGA扩展板接口IO191(nRST),用数据线与扩展板H57连接。

将FPGA扩展板接口IO193(ELP),用数据线与母板二进制开关单元H7连接。

将FPGA扩展板接口IO197(PC_1),用数据线与母板二进制开关单元H6连接。

将FPGA扩展板接口IO168(IR2),用数据线与母板二进制开关单元H5连接。

将FPGA扩展板接口IO164(IR3),用数据线与母板二进制开关单元H4连接。

将FPGA扩展板接口IO162(C),用数据线与母板二进制开关单元H3连接。

将FPGA扩展板接口IO160(Z),用数据线与母板二进制开关单元H2连接。

将将FPGA扩展板接口IO5与扩展板J9相连,IO6与J6相连,IO13与J7相连,IO14与J8相连。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| I01(输入D[31:24]位) | J2(扩展板二进制开关S9-S16) |

| I02(输入D[23:16]位) | J4(扩展板二进制开关S17-S24) |

| IO9(输入D[15:8]位) | J5(扩展板二进制开关S25-S32) |

| IO10(输入D[7:0]位) | J10(扩展板二进制开关S40-S47) |

| I07(输出PC[31:24]位) | J3(扩展板L17-L24) |

| I08(输出PC [23:16]位) | J11(扩展板L42-L57) |

| IO15(输出PC [15:8]位) | J12(扩展板L58-L65) |

| IO16(输出PC [7:0]位) | M04(母板L1-L8) |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(nRST) | H57 |

| IO193(ELP) | H7 |

| IO197(PC_1) | H6 |

| IO168(IR2) | H5 |

| IO164(IR3) | H4 |

| IO162(C) | H3 |

| IO160(Z) | H2 |

| IO5(输入数码管数据) | J9 |

| IO6(输出数码管扫描选通) | J6 |

| IO13(输出数码管数据) | J7 |

| IO14(输入数码管扫描选通) | J8 |

2.充分理解pccnt.VHD。了解模型机中中断的实现原理。

3.把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验10 32位指令计数器PC实验 文件夹中的pccnt.sof程序下载到FPGA。

4.按下SB1键,输出复位信号,观察32位LED显示及八位八段管 (PC计数器的输出显示)是否清零;松开SB1。

5.PC+1实验:将H7(ELP信号)、H6(PC_1信号)置成“1”状态,使跳转控制信号处于PC+1状态,控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 1 | 1 | 0 | 0 | 0 | 0 |

按PLS1键,产生一个时钟信号,观察J1,J13,J14,J01输出的32位LED及八段管DIS1-DIS8的显示,看看PC是否加1。再按PLS1键,观察PC是否再次加1。

6.直接跳转实验: 拨动S9-S32,S40-S47,输入D的值,设置跳转的目标地址为02020202H。拨动H7位设成“0”, 使ELP信号为低。拨动H4将其设成“1”,使IR3为高,将跳转控制设成直接跳转方式。控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 0 | 1 | 0 | 1 | 0 | 0 |

按PLS1键,产生一个时钟信号,观察输出显示的PC值(LED灯扩展板JL17-L24, L42-L65,母板L1-L8及数码管DIS1-DIS8),是否转到目标地址02020202H。

7.条件跳转实验1:拨动S9-S32,S40-S47,输入D的值,设置跳转的目标地址为81818181H。拨动H5,H4使IR2、IR3置成“00”,将跳转控制设置成判进位跳转方式。将H3(C)设置成“1”,表示有进位,控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 0 | 1 | 0 | 0 | 1 | 0 |

按PLS1键,产生一个时钟信号,观察输出显示,看看PC是否转到D所指定的目标地址81818181H。再将H3(C)拨成“0”,表示无进位。控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 0 | 1 | 0 | 0 | 0 | 0 |

按PLS1键,观察八段管输出显示,看看PC是否加1。

8.条件跳转实验2:拨动H5,H4使IR3、IR2置成“01”,将跳转控制设置成判零跳转方式。将H2(Z)设置成“1”,表示累加器为零,控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 0 | 1 | 1 | 0 | 0 | 1 |

按PLS1键,产生一个时钟信号,观察输出LED及数码管的显示,看看输出显示的PC值(数码管DIS1-DIS8)是否转到D所指定的目标地址(即数码管DIS1-DIS8显示值与DIS9-DIS16显示值相同)。再将H2(Z)拨成“0”,表示累加器不为零,控制信号如下表:

| H7 | H6 | H5 | H4 | H3 | H2 |

| ELP | PC_1 | IR2 | IR3 | C | Z |

| 0 | 1 | 1 | 0 | 0 | 0 |

按PLS1键,产生一个时钟信号,观察输出LED及数码管的显示,看看PC是否加1。

实验十一 中断控制实验

一、实验要求

用计算机组成原理与系统结构扩展实验板上的开关做为输入,发光二极光及八段数码管做为输出。用VHDL语言编写程序下载到EP2C5Q208中实现32位模型机中断控制功能。

二、实验目的

了解32位模型机中中断控制的工作原理和实现方法。学习用VHDL语言描述硬件逻辑。学习使用EDA开发环境。

三、实验说明

32位模型机中断控制的VHDL:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY int32 IS

PORT (

IREN : IN STD_LOGIC;

EINT : IN STD_LOGIC;

ICEN : OUT STD_LOGIC;

ACK : OUT STD_LOGIC;

REQ : OUT STD_LOGIC;

nRST : IN STD_LOGIC;

I_REQ: IN STD_LOGIC;

CLK : IN STD_LOGIC

);

END int32;

ARCHITECTURE behv OF int32 IS

SIGNAL R_REQ, R_ACK: STD_LOGIC;

SIGNAL FATCH_INT: STD_LOGIC;

BEGIN

REQ <= R_REQ;

ACK <= R_ACK;

ICEN <= FATCH_INT;

PROCESS(I_REQ, nRST, EINT)

BEGIN

IF (EINT = '0') OR (nRST = '0') THEN

R_REQ <= '0';

ELSIF I_REQ'EVENT AND I_REQ = '1' THEN

R_REQ <= '1';

END IF;

END PROCESS;

PROCESS(CLK, nRST, EINT, IREN, R_REQ, R_ACK, FATCH_INT)

BEGIN

IF (IREN = '0') AND (R_REQ = '1') AND (R_ACK = '0') THEN

FATCH_INT <= '0';

ELSE

FATCH_INT <= '1';

END IF;

IF (EINT = '0') OR (nRST = '0') THEN

R_ACK <= '0';

ELSIF CLK'EVENT AND CLK = '1' THEN

IF FATCH_INT = '0' THEN

R_ACK <= R_REQ;

END IF;

END IF;

END PROCESS;

END behv;

在上面程序中,IREN表示程序执行过程中的取指令操作。中断请求信号只有在此信号有效时(取指令时)才会被响应。IENT用于在中断返回时,清除中断请求寄存器和中断响应寄存器。ICEN为输出信号,此信号用于控制读中断指令。ACK为中断响应信号,REQ为中断请求信号。nRST为复位信号。I_REQ为中断申请输入信号。CLK为时钟脉冲。

四、实验步骤

1.连线

将FPGA扩展板接口IO188(CLK),用数据线与母板时序单元PLS1连接,对应CLK。

将FPGA扩展板接口IO191(nRST),用数据线与扩展板H57连接。

将FPGA扩展板接口IO193(IREN),用数据线与母板二进制开关单元H7连接。

将FPGA扩展板接口IO197(EINT),用数据线与母板二进制开关单元H6连接。

将FPGA扩展板接口IO168(ICEN),用数据线与母板微指令单元M7连接。

将FPGA扩展板接口IO164(ACK),用数据线与母板微指令单元M6连接。

将FPGA扩展板接口IO162(REQ),用数据线与母板微指令单元M5连接。

将FPGA扩展板接口IO160(I_REQ),用数据线与母板时序单元PLS4连接。

实验连线表如下:

| FPGA扩展板接口 | 左侧板接口 |

| IO188(输入寄存器时钟CLK) | 时序单元PLS1 |

| IO191(nRST) | H57 |

| IO193(IREN) | H7 |

| IO197(EINT) | H6 |

| IO168(ICEN) | M7 |

| IO164(ACK) | M6 |

| IO162(REQ) | M5 |

| IO160(I_REQ) | 时序单元PLS4 |

2.充分理解int32.VHD。了解模型机中中断的实现原理。

3.把ALTERA下载器一端连到微机的并口,一端连接到FPGA扩展区的JTAG口,打开实验系统电源,把计算机组成原理32位\实验11 32位指令计数器PC实验 文件夹中的int32.sof程序下载到FPGA。

4.按下SB1键,输出复位信号。将H7,H6拨到“1”的位置,使IREN和EINT都处于无效状态(低电平有效),将内部的中断请求寄存器、中断响应寄存器都清零使其能响应中断, 控制信号如下表:

| H7 | H6 |

| IREN | EINT |

| 1 | 1 |

5.中断申请:按PLS4键产生中断请求信号申请中断,扩展板上M5对应的发光二极管变亮,表示有中断申请。

6.中断响应:将H7拨成“0”,也就使IREN有效表示取指令操作,控制信号如下表:

| H7 | H6 |

| IREN | EINT |

| 0 | 1 |

扩展板上的M7对应的发光二极管灭(ICEN低电平有效,将中断地址送给PC),表示已经响应中断。

7.中断处理:按PLS1键产生一个时钟信号,扩展板上M7,M6对应的发光二极管亮,表示取指操作取出中断处理指令来执行。

8.中断退出:将H7拨成“1”,IREN置无效。将H6拨成“0”,将EINT置成有效。控制信号如下表:

| H7 | H6 |

| IREN | EINT |

| 1 | 0 |

M7对应的发光二极管亮,M6,M5对应发光管灭,中断请求寄存器和中断响应寄存器清零,表示可以接受下一次中断申请。

📝总结

计算机组成原理领域就像一片广袤而未被完全探索的技术海洋,邀请你勇敢踏足数字世界和计算机组成原理的神秘领域。这是一场结合创造力和技术挑战的学习之旅,从基础概念到硬件实现,逐步揭示更深层次的计算机结构、指令集架构和系统设计的奥秘。渴望挑战计算机组成原理的学习路径和掌握计算机硬件的技能?不妨点击下方链接,一同探讨更多数字技术的奇迹吧。我们推出了引领趋势的💻 计算机组成原理专栏:《机组 | 模块单元实验》,旨在深度探索计算机系统技术的实际应用和创新。🌐💡