在RTL设计中,仿真时查看异常情况,异常出现时,断言会报警,断言占整个设计的比例应不少于30%

assertion作用:

- 检查特定条件或事件序列的出现情况

- 提供功能覆盖

断言失败的严重程度:$fatal(中止仿真)>$error>$warning(仍然仿真)>$info

assertion的种类

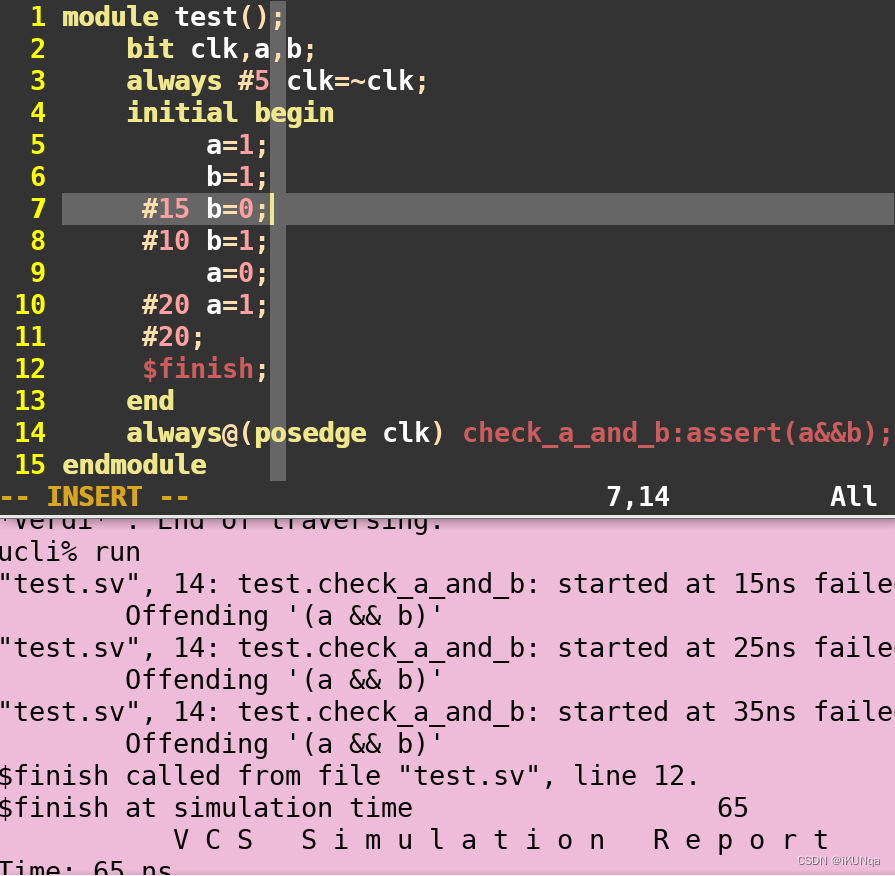

立即断言

检查当前仿真时间的条件,检查某一个时间点,采样变化后的值

需放在过程块中,相当于if else

断言名:assert (判断条件)

(执行语句;)

(else 执行语句;)

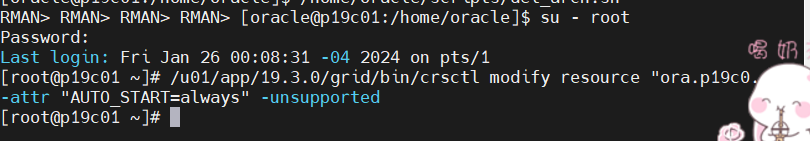

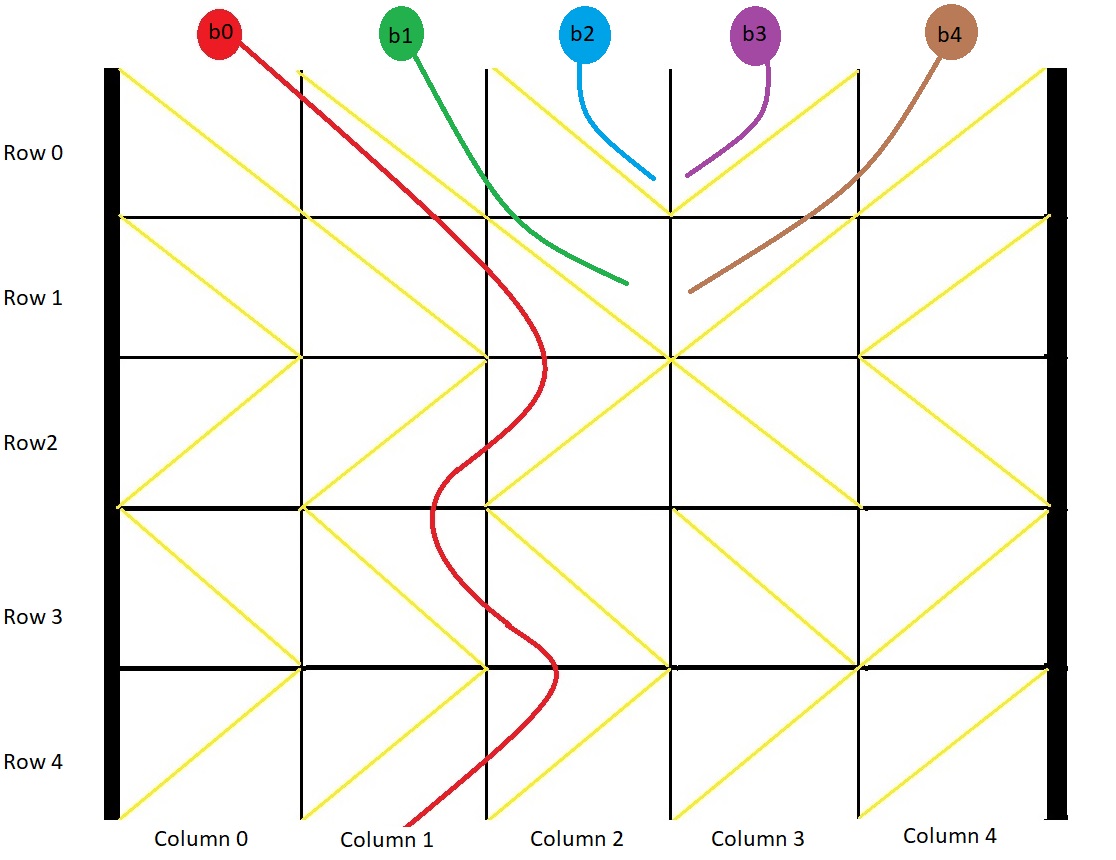

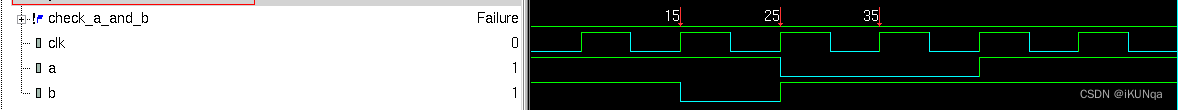

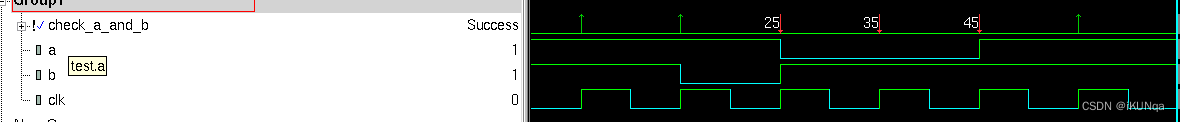

simv -gui

绿色上箭头成功,红色下箭头失败

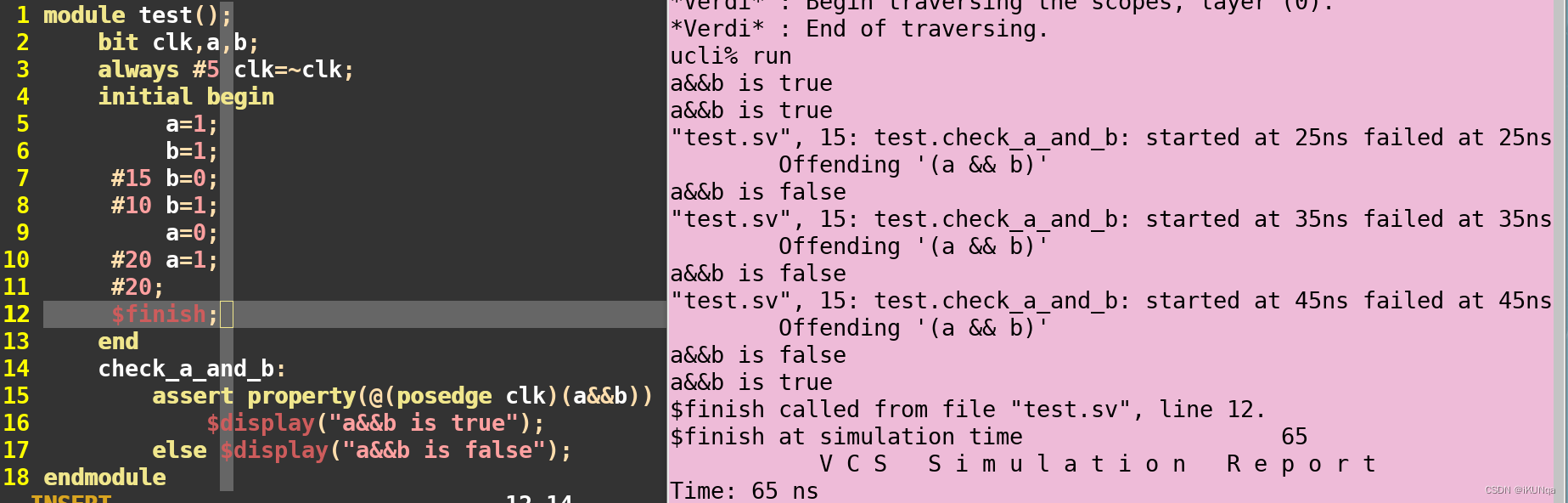

并发断言

连续运行的模块,为整个仿真过程检查信号→需指定一个采样时钟,采样变化前的值

可放在过程块,module,interface,program中

与立即断言的区别:property关键字

断言名:assert property(判断条件)

(执行语句;)

(else 执行语句;)

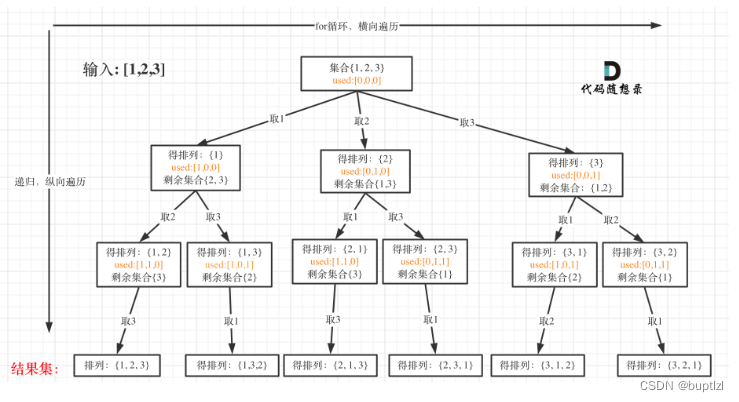

assertion的层次结构

SVA中可存在内建的单元,包括:

- 布尔表达式

- Sequence序列

- Property属性

sequence特性

- 可带参数

- 可在property中调用

- 可使用局部变量

- 可定义时钟周期

带参数的sequence

sequence name_sequence(a,b);

@(posedge clk) a&&b;

……

endsequence

check:assert property (name_sequence(a,b))

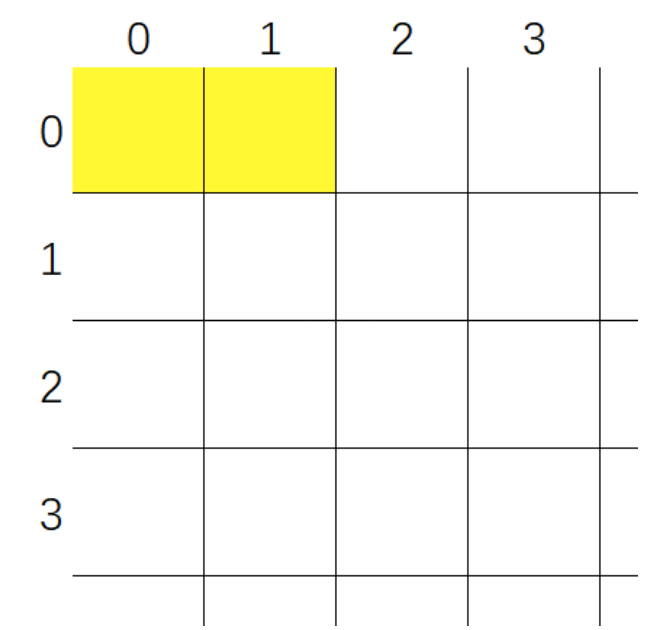

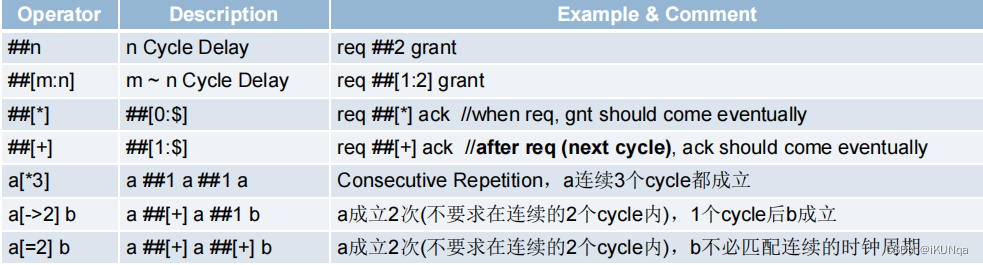

带时序关系的sequence

#2;//两个时间单位

a ##2 b;//两个时间周期

property属性

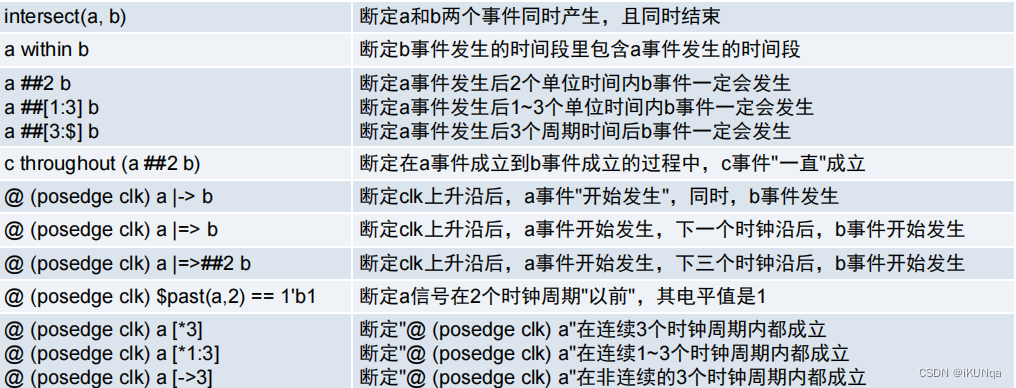

比sequence更高一层的单元,可在property中使用蕴含操作符

a|->b 同时检查

a|=>b 延迟一个时钟周期检查

property需用cover/assert/assume等关键字进行实例化,而sequence直接调用即可

assertion的触发判断

$rose(a);//信号上升,包括x→1,z→1

$fell(a);//信号下降

$stable(a);//两个周期内的信号值是否变化

$changed(a);

总线的断言函数

$onehot(BUS) //BUS中有且仅有1 bit是高,其他是低。

$onehot0(BUS) //BUS中有不超过1 bit是高,也允许全0。

$isunknown(BUS) //BUS中存在高阻态或未知态。

$countones(BUS) == n //BUS中有且仅有n bits是高,其他是低。

$past(signal, cycle_num, 1) //(信号,n个周期前,信号的值)