文章目录

- 3. 时序电路的设计

- 3.1 触发器

- 3.1.1 最简单的D触发器

- 3.1.2 带复位端的D触发器

- 3.1.3 复杂功能的D触发器(没有太大必要)

- 3.1.4 T触发器

- 3.2 计数器

- 3.2.1 二进制计数器

- 3.2.2 (重要)任意进制计数器

- 3.3 移位寄存器

- 3.4 序列信号发生器

- 3.4.1 例:产生10011序列的信号发生器

- (总结)序列信号发生器

- 3.4.2 伪随机码发生器

3. 时序电路的设计

-

所有的是时序逻辑电路都可以拆成组合逻辑电路+存储

(关于组合逻辑电路的理解可以参考我数电的博客https://blog.csdn.net/y_u_yu_yu_/article/details/127592466)

-

可以分成两个部分,组合逻辑电路和存储电路。组合逻辑电路的输入一个是x信号一个是当前的状态,这两个信号决定了组合电路的输出结果

-

组合电路的输出有两个,一个是对外输出信号,还有一个是对下一个状态的激励

-

三大方程:输出方程,驱动方程和状态转移方程

-

时序电路的设计过程:在对时序逻辑电路描述的时候,我们说把这三个方程描述清楚,电路就出来了

-

时序电路设计的方式:

-

时序逻辑电路的设计多样性和方法多样性举例

-

例:用VerilogHDL 设计一个“111”序列检测器,当输入三个或三个以上的“1”时,电路输出为1,否则为 0。

-

第一种:状态转移图描述方式

(1)首先确定电路的输入变量和输出变量。该电路仅有一个输入端和一个输出端,设输入变量为 X,代表输入序列;输出变量为 Z,表示检测结果

(2)因此需要定义四种电路状态

s0一初始状态,表示电路还未收到一个有效的 1

s1一表示电路收到了一个 1

s2一表示电路收到了连续的两个 1

s3一表示电路收到了连续的二个 1

(3)根据状态转移图,编写代码

-

综合的电路:

-

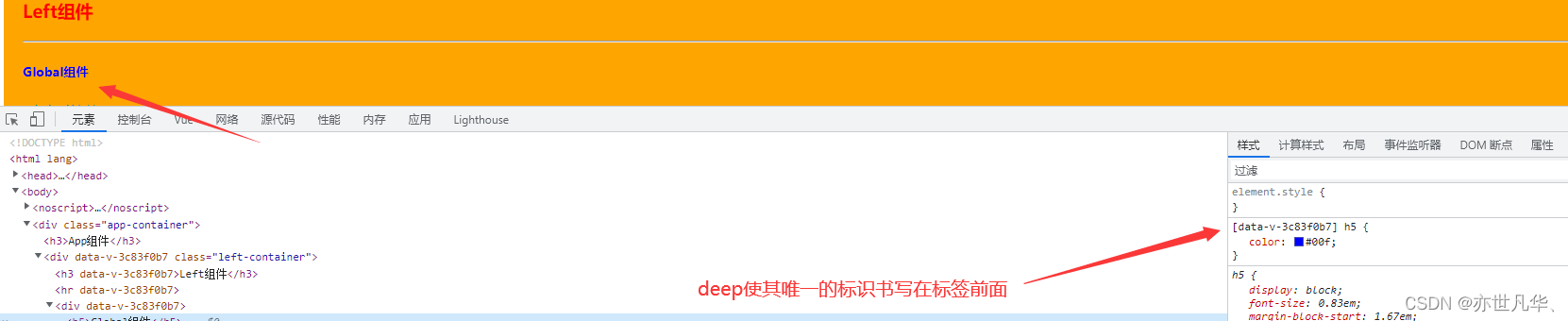

第二种:基于状态化简的结构性描述方式

(1)对图 4.3-3 所的状态转移图进行化简,仅剩三个状态,需要用两位二进制数表示,即需要两个D触发器储存状态。设Q1表示高位寄存器的输出,Qo表示低位寄存器的输出。将状态的跳转以及输出Z 用卡诺图的形式示出,

(2)由卡诺图得出带你路有的输出方程和状态方程

(3)根据简化方程编写代码

-

综合的电路:

-

第三种:Verilog HDL抽象描述方式

-

在 Verilog HDL中还可以对电路进行抽象描述。实现序列“111”的检测,可以使用1个三位的移位寄存器,将输入X作为移位寄存器的输入,当寄存器中为111时,输出Z为1。

-

代码

-

综合的电路

3.1 触发器

- 触发器是时序逻辑电路的最基本电路单元,主要有 D触发器、JK 触发器、T触发器和RS 触发器等。根据功能要求的不同,触发器还具有置位、复位、使能、选择等功能

- !!RS触发器分为普通RS触发器和中控RS触发器,是最早期的触发器类型,性能不是很稳定,只是由一个SET和RESET两个端,这种电路在时序电路设计中很少使用

- !!JK触发器有两个端子,早期的电路希望有两个而不是一个信号进行控制触发器

- !!!!D触发器是目前时序电路中用的最广泛的触发器,基本上都是D触发器(重点是D触发器)

3.1.1 最简单的D触发器

- 还有两个SET和CLR,SET是置位可能是置一置零,CLR是清零的信号

- 用HDL描述:

3.1.2 带复位端的D触发器

- 在D触发器的实际使用中,有时需要一个复位端(也称清零端)。

- 电路上电时,电路的逻辑处于不定状态,复位脉冲的到来将电路初始化为 Q=0 的状态随后,在时钟的控制下,输入端D的数据在每个时钟上升沿被置到输出端Q

- HDL描述:

(1)同步清零:

(2)异步清零:

3.1.3 复杂功能的D触发器(没有太大必要)

- 前面介绍了最简单的 D触发器和带有同步清 0、异步清0的D触发器。这里给出同步清0置1和异步清0置1共同在一个触发器上的复杂 D触发器例子

- Verilog代码:

3.1.4 T触发器

- 其逻辑功能为:当时钟的有效边沿到来时,如果 T=1,则触发器翻转;如果T=0,则触发器的状态保持不变。reset 为复位端,异步复位,低电平有效。

- 带有异步清零的T触发器代码:

3.2 计数器

- 计数器是应用最广泛的逻辑部件之一。计数器可以统计输入脉冲的个数,具有计时计数、分频、定时、产生节拍脉冲等功能

- 计数器的种类繁多,根据计数器中触发器时钟端的链接方式分为同步计数器和异步计数器:根据计数方式分为二进制计数器、十进制计数器和任意进制(也称为 M 进制)计数器根据计数器中的状态变化规律分为加法计数器、减法计数器和加/减计数器

- !!在面试中,经常会考,会让你设计一个二分频电路,三分频电路或者n分频电路,但是目的其实就是让你设计一个计数器

3.2.1 二进制计数器

- HDL描述

3.2.2 (重要)任意进制计数器

- 需要注意两个事情:位宽和奇数方式

- 计数方式有两种实现方法:反馈清零法(从0开始,来一个加一个,加到一定清零)和反馈置数法(从置数开始,来一个减一个,减到0回到置数)。

- 位宽:对于M 进制的计数器,第一步需要确定计数器所需要触发器的个数。N个触发器对应了2的N次方个状态,应有2的N次方>M。任意进制计数器选取满足条件的最小N为计数器中触发器的个数。

- 以十一进制计数器为例,最少需要 4 个触发器。采用反馈清零法设计的十一进制计数器的 VerilogHDL程序代码如下:

3.3 移位寄存器

- 移位寄存器可以用来实现数据的串并转换,也可以构成移位行计数器,进行计数、分频,还可以构成序列码发生器、序列码检测器等,它也是数字系统中应用非常广泛的时序逻辑部件之一

- 环形移位寄存器

- 该例中,将每个寄存器的输出作为下一位寄存器的输入,并将高位寄存器的输出作为循环的输入。Verilog代码如下:

- !!!!移位寄存器有一个特殊的用法:移位操作符由于在触发器和触发器直接没有组合电路,所以移位寄存器这种电路的速度特别快,在数字电路里面,可以说是最快的电路,所以用移位寄存器可以做很多高速电路的设计

3.4 序列信号发生器

- 序列信号是数字电路系统中常用的功能单元,其种类很多,如按照序列循环长度 M 与触发器数目 n的关系,一般可分为三种:

(1)最大循环长度序列码,M = 2n。

(2)最长线性序列码(m序列码),M = 2n-1。(少了全0的状态)

(3)任意循环长度序列码,M < 2n。

3.4.1 例:产生10011序列的信号发生器

(1)方法1:用移位寄存器构成

- 采用循环移位寄存器,在电路工作前,将所需的序列码置入移位寄存器中,然后循环移位,就可以不断地产生需要的序列。

- 由于移位寄存器输入和输出信号之间没有组合电路,不需要进行组合逻辑的反馈运算,因此这种序loadclk列产生电路的工作频率很高。

- 缺点是移位寄存Dm-i器长度取决于序列长度,因此所占用电路的面积很大

- Verilog代码:

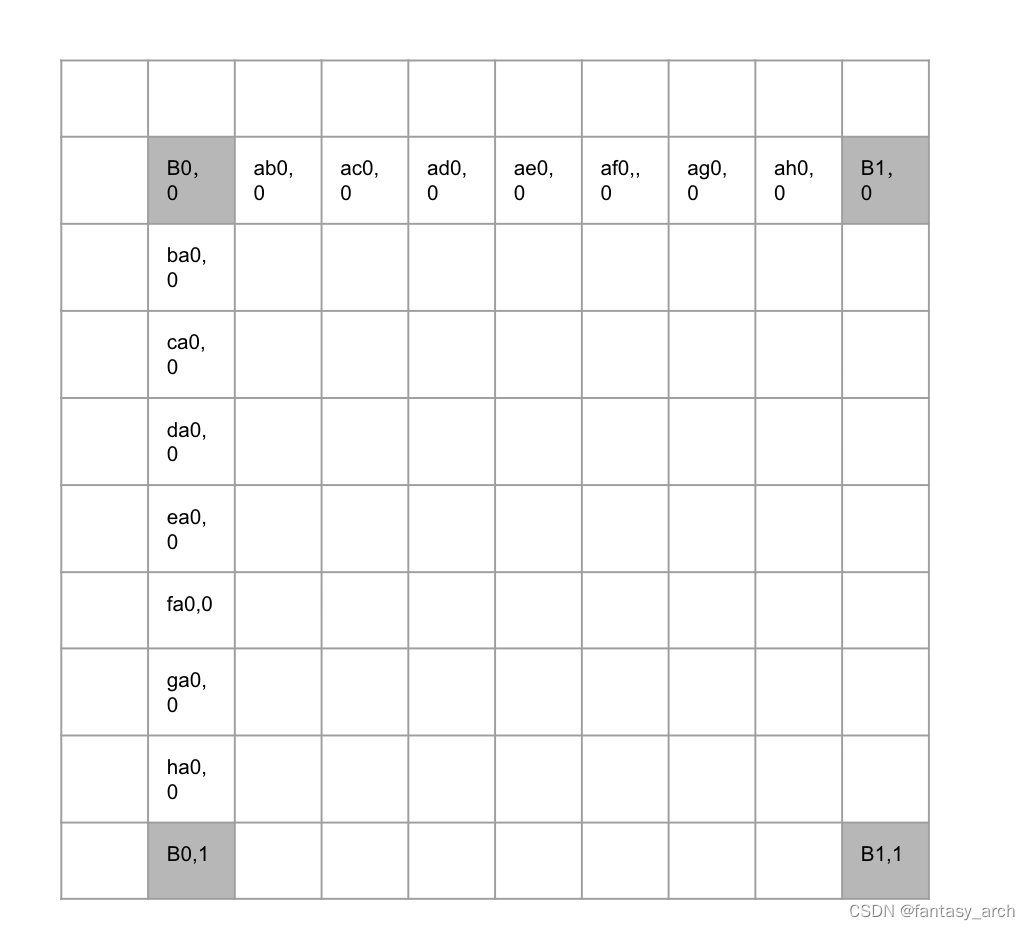

(2)方法2:用移位寄存器和组合逻辑电路构成(数电教材中的方法) - 反馈移位寄存器型序列信号发生器的结构框图如图 4.3-14 所示,它由移位寄存器和组合反馈网络组成,从移位寄存器的某一输出端可以得到周期性的序列码。

- 设计步骤:

1.根据给定的序列信号的循环周期M,确定移位寄存器位数n,2n-1 < M ≤ 2n

2.确定移位寄存器的M个独立状态。将给定的序列码按照移位规律每n位一组划分为 M 个状态。若M个状态中出现重复现象,则应增加移位寄存器位数。用n+1位再重复上述过程,直至划分为 M 个独立状态

3.根据 M个不同的状态列出移位存器的态序表和反馈数表,求出馈函数 F的表达式

4.检查自启动性能

- Verilog代码:

- 状态转移图,三大方程,结构体描述,这三种描述都可以设计这个东西

- 得到反馈函数之后实际上用的还是移位寄存器,只不过以为寄存器的最低端是反馈函数,函数化简逻辑代数表达式的形式可以得到这个值,然后连接在一起

(3)方法3:由计数器构成 - 计数型序列信号发生器和反馈型序列信号发生器大体相同,都由时序电路和组合电路两部分构成。不同之处在于,反馈型序列信号发生器的时序状态由移位寄存器产生,输出取寄存器的最高位;而在计数型序列信号发生器中,采用计数器代替移位寄存器产生时序状态,输出由组合电路产生。

- 计数型序列信号发生器的优点在于,计数器的状态设置与输出序列没有直接关系,不需要根据输出确定状态,只需要将反馈网络设计好就可以了。因此计数结构对于输出序列的更改比较方便,而且只要连接到不同的反馈网络,就可以同时产生多组序列码。

- 实际上就是一个译码电路

- 分为两步

1.根据序列码的长度 M 设计 M 进制计数器,状态可以自定

2.按计数器的状态转移关系和序列码的要求设计组合输出网络 - 对于“100111”序列的信号发生器,序列信号的 M 值为6,因为需选用模6计数器计数器的状态选择从000到101

- 其中,译码电路也可以用case语句进行设计

(总结)序列信号发生器

- 实际上序列信号发生器产生的过程是一个特别典型的数字电路设计的过程

- 讲了三种设计方式(实际上也有有限状态机,状态转移图等方式,但是现在只看这三种电路设计方式),即3.4开头说的

- !!!!第一种方式采用移位寄存器的设计方式,这种电路方式特别快,所以对于信号来讲是非常好的设计方式,但是耗费了六个寄存器(如果描述1024长度的信号,这时候就需要1024个寄存器),这个的问题就是用面积换速度

- !!!!第二种方式从存储位宽的角度讲,因为只存储当前的状态,所以存储3-4个bit就可以(6位的信号)这样的话,如果是一个1024位的信号,那么存10个或者11个bit就可以了,位宽就减少了。但是有一个问题,它的反馈网络有一个反馈信号输入端,当信号发生扰动的时候(组合电路出现状况),如果反馈信号一旦发生错误,电路功能就不对了,所以这个电路需要一段时间以后才能自愈合甚至不能自愈合

- !!!!第三种电路分为组合电路和计数器电路 ,组合电路没有对计数器进行反馈。组合电路的输出结果是由当前输入决定,也就是当组合电路发生错误的时候,只要保证输入正确,这个错误就不会带到下一个信号,所以误差不会传播。当计数器产生错误时,可以通过设计保护电路,让它在异常状态下可以回到其实状态,如果进入计数器的六个状态,一段时间后,他就能自愈合回到起始状态,所以电路的可靠性就比较高

- !!所以,电路设计和方法与电路的可靠性和性能是密切相关的

3.4.2 伪随机码发生器

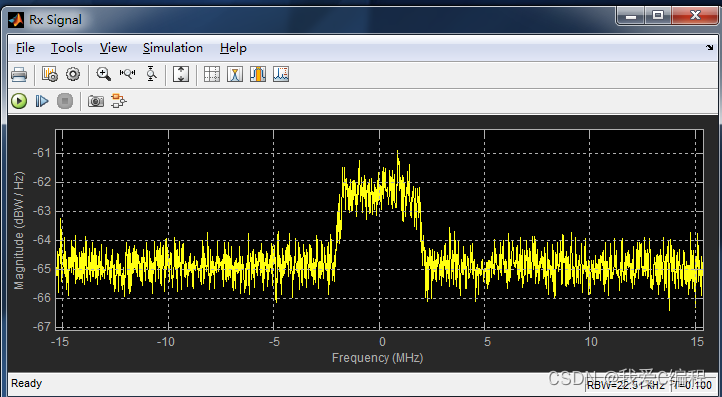

- 伪随机码是一种变化规律与随机码类似的二进制代码,可以作为数字通信中的一个信号源,通过信道发送到接收机,用于检测数字通信系统错码的概率,即误码率。

- 在传统的数字电路设计中,伪随机序列信号发生器是用移位寄存器型计数器来实现的,见图 4.3-14(上面讲的方式2,想到小m序列产生的时候,我们一定要知道他就是这种反馈的组合逻辑网络来实现的)。反馈网络输入信号从移位寄存器的部分输出端(Qn1~Qo)中取出,它的输出端F反馈到移位寄存器的串行输入端

- 数学家提供了一种N-F表,N代表抽头的数量,F代表产生异或的输出端信号的位置。简单来说,电路就是方式2的图,对于组合反馈网络来讲就是一个异或的电路,F就是对图中Q的对应位置的几位异或反馈到输入端就可以了

- 主要问题:怎么确定反馈系数?数学家就提供了N-F表。N代表小m序列的存储位宽(要设计1023的小m序列,需要10bit),F就是反馈的抽头系数

- 小m和大M相比少了一个状态(全0状态),下面以N=4 为例。在 15 位最长线性序列移位寄存器型计数器中,有一个由“0000构成的死循环,为了打破死循环,可以修改式为

- Verilog代码如下:

![[附源码]java毕业设计流浪动物领养系统](https://img-blog.csdnimg.cn/972a4a69e134405bb5fc491f8d1dd54c.png)

![[附源码]java毕业设计流浪动物救助网站](https://img-blog.csdnimg.cn/074451d7e2ff4b81af29443fc72638e7.png)