同步状态机的结构以及Mealy和Moore状态机的区别

- 1,介绍Mealy型状态机和Moore型状态机的两种结构

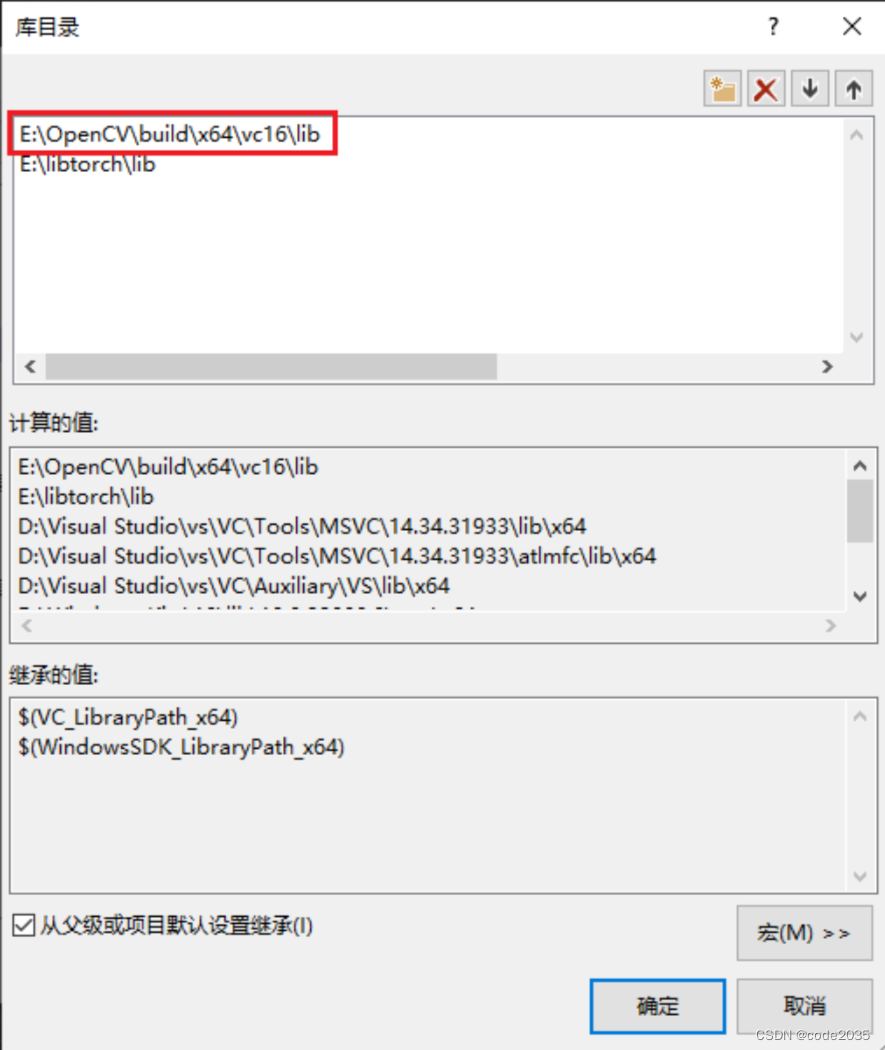

- 2,设计高速电路的方法

由于寄存器传输级(RTL)描述的是以时序逻辑抽象所得到的有限状态机为依据,因此,把一个时序逻辑抽象成一个同步有限状态机是设计可综合风格的Verilog HDL模块的关键。

在本章节中,在了解状态机结构的基础上通过各种实例,由浅入深地介绍各种可综合风格的Verilog HDL模块,并把重点放在时序逻辑的可综合有限状态机的Verilog设计要点上。

1,介绍Mealy型状态机和Moore型状态机的两种结构

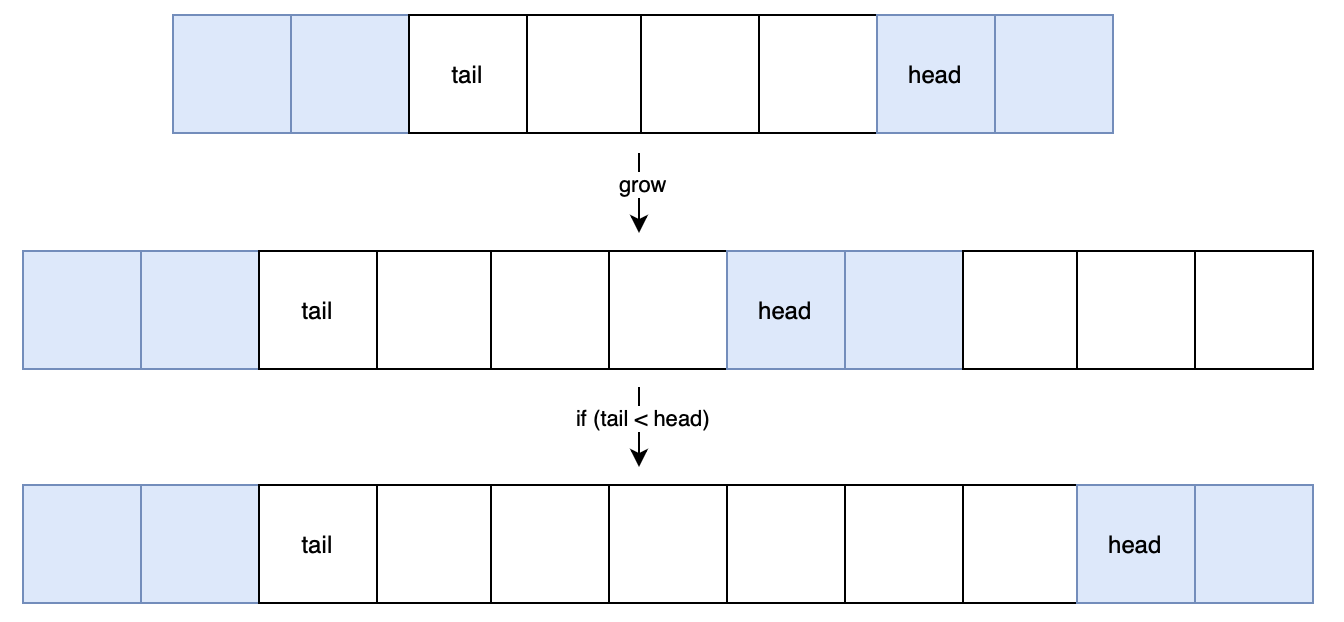

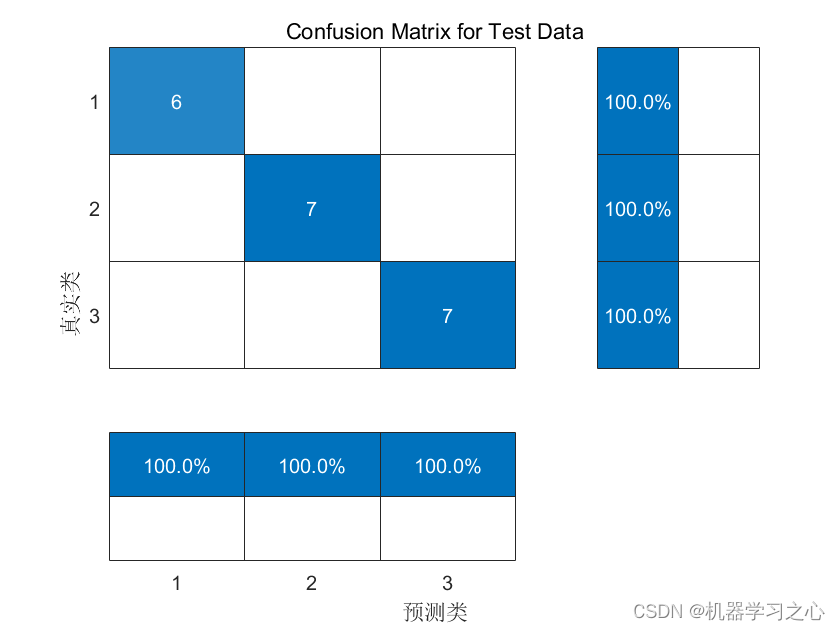

Mealy型状态机和Moore型状态机的区别:

1,Mealy型状态机的输出,与当前状态和输入函数有关;

2,Moore型状态机的输出,只与当前状态有关;

这两种电路结构除了在输出电路部分有些不同外,其他地方都是相同的。在实际设计工作中,其实大部分状态机都属于Mealy状态机,因为状态机的输出中或多或少有几个属于Mealy型输出,输出不但与当前状态有关还与输入有关;还有几个输出属于Moore型状态机,即只与当前状态有关。

2,设计高速电路的方法

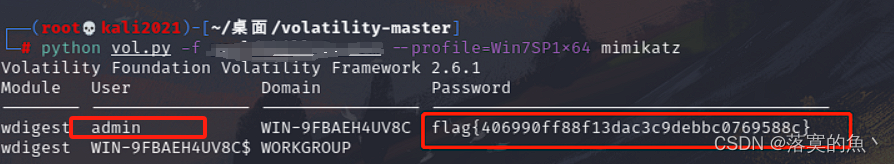

在设计高速电路时,常常有必要使状态机的输出与时钟几乎完全同步。

1,有一个办法是把状态变量直接用作输出,为此在指定状态编码时需要多费一些脑力,也可能会多用几个寄存器。

这种设计思路,在高速状态机电路时常常使用,这称为输出编码的状态指定。

这种状态机属于图2的Moore型状态机

2,另一个办法,是如图3所示,在输出逻辑G后面再加一组与时钟同步的寄存器输出流水线寄存器,让G所有的输出信号在下一个时钟跳变沿同时存入寄存器组,即完全同步地输出,把这种输出称为流水线化的输出。

其实,在这几种状态机之间,只要做一些改变,便可以从一种形式转变为另一种形式。比如可以将图3所示的状态机中产生流水输出的寄存器省去,把这些寄存器用在状态记忆上,就可以很容易地得到一个把状态机变量用作输出信号的Moore型状态机。

状态机的分类不重要,重要的是设计者如何把握输出的结构能满足设计的整体目标,包括定时的准确性和灵活性。