常用寄存器

PRIMASK寄存器

PRIMASK寄存器为1位宽的中断屏蔽寄存器。在置位时,它会阻止不可屏蔽中断(NMI)和HardFault异常之外的所有异常(包括中断)。实际上,它是将当前异常优先级提升为0,这就是可编程异常/中断的最高优先级。

FAULTMASK寄存器

FAULTMASK与PRIMASK相类似,但同时它能屏蔽HardFault异常,它实际上是将异常优先级提升到了-1。

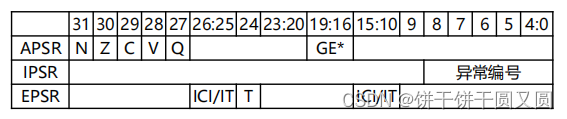

程序状态寄存器(xPSR)

xPSR包含:

- 应用PSR(APSR)

- 执行PSR(EPSR)

- 中断PSR(IPSR)

GE在Cortex-M4等ARMv7E-M处理器中存在,在Cortex-M3处理器中则不可用。

- N:负标志

- Z:零标志

- C:进位标志

- V:溢出标志

- Q:饱和标志(ARMv6-M中不存在)

- GE[3:0]:大于或等于标志

- ICI/IT:中断继续指令位

- T:Thumb状态,总是1,清除此位会引起错误异常

- 异常编号:表示处理器正在处理的异常

中断向量表

Cortex-M系列处理器的中断向量表位于0x00000000,但Cortex-M3/4系列提供了Vector table offset register(SCB_VTOR),所以,中断向量表的位置位于0x00000000 + SCB_VTOR。

异常相关指令

- CPSIE I:使能中断(清除PRIMASK)

- CPSID I:禁止中断(设置PRIMASK),NMI和HardFault不受影响

- CPSIE F:使能中断(清除FAULTMASK)

- CPSID F:禁止中断(设置FAULTMASK),NMI不受影响

移植过程

在嵌入式领域有多种不同CPU架构,例如Cortex-M、ARM920T、MIPS32、RISC-V等等。

为了使RT-Thread能够在不同CPU架构的芯片上运行,RT-Thread提供了一个libcpu抽象层来适配不同的CPU架构。

libcpu层向上对内核提供统一的接口,包括全局中断的开关,线程栈的初始化,上下文切换等。

RT-Thread的libcpu抽象层向下提供了一套统一的CPU架构移植接口,这部分接口包含了全局中断开关函数、线程上下文切换函数、时钟节拍的配置和中断函数、Cache等等内容。

![【C++入门到精通】智能指针 [ C++入门 ]](https://img-blog.csdnimg.cn/direct/108d10fb122e41ad9888d25090dcca19.png#pic_center)

![恢复 iPhone 和 iPad 数据的 10 个好工具 - [苹果数据恢复]](https://img-blog.csdnimg.cn/img_convert/3505f6ca09ea34fe48be77e73043e18d.png)