题型一、第二章的画图

给一个逻辑表达式,画出晶体管级别的电路图

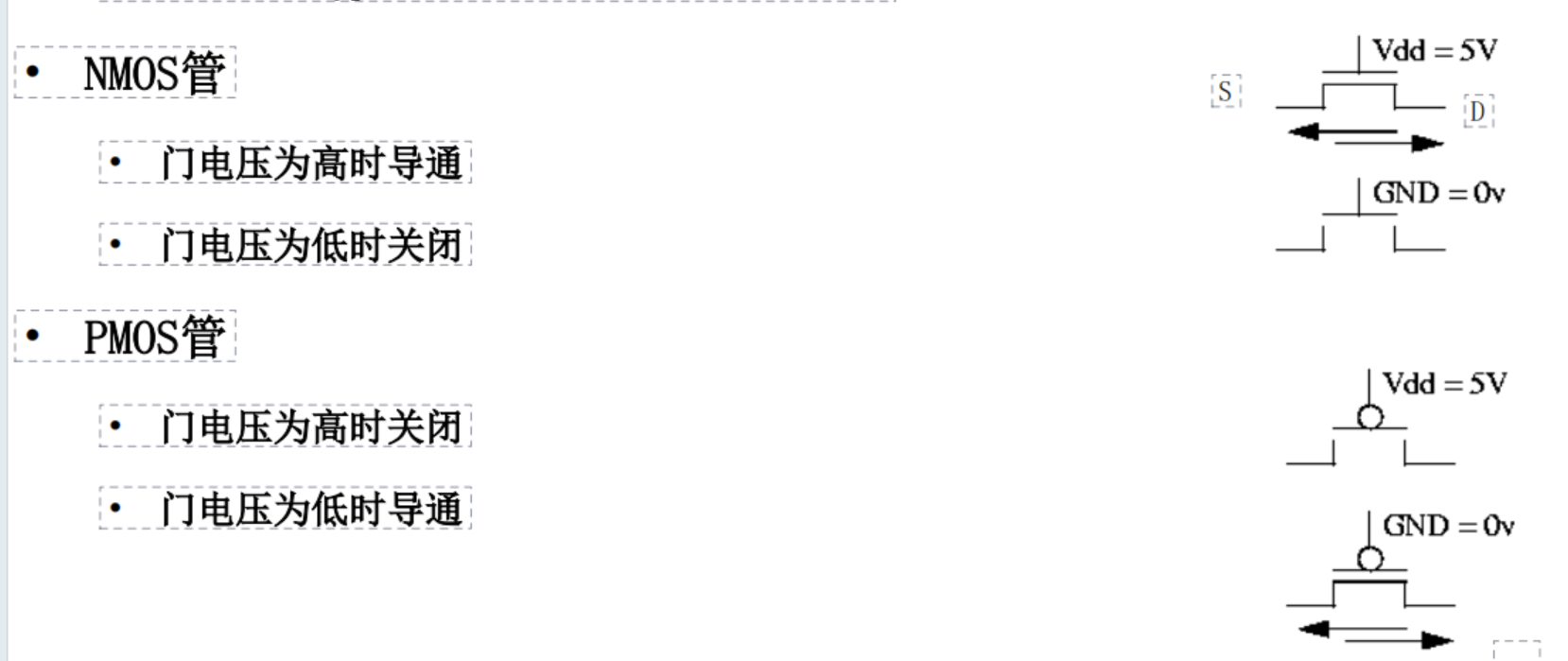

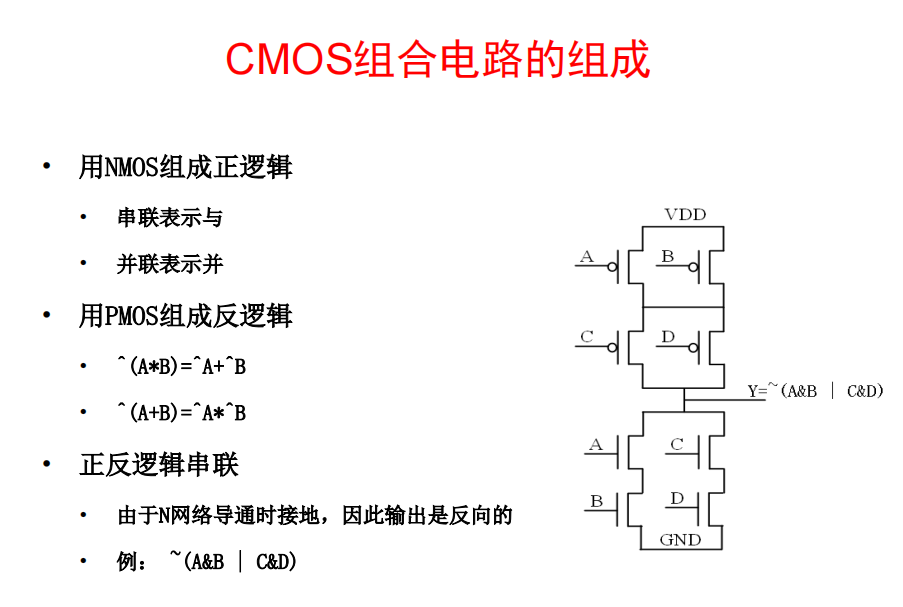

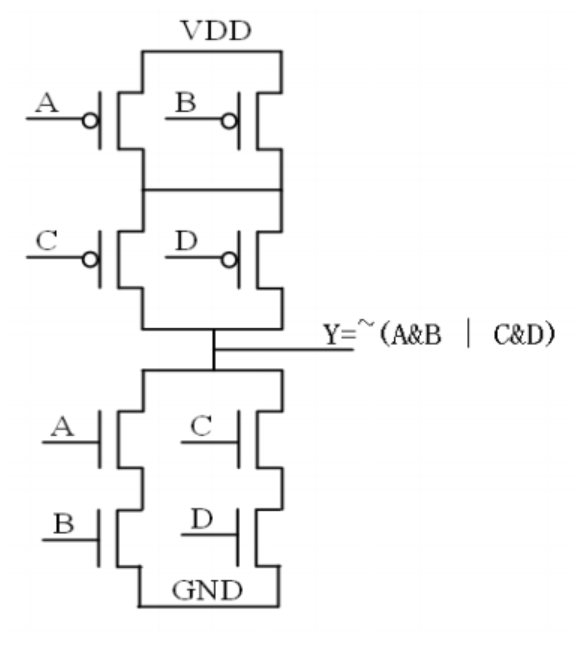

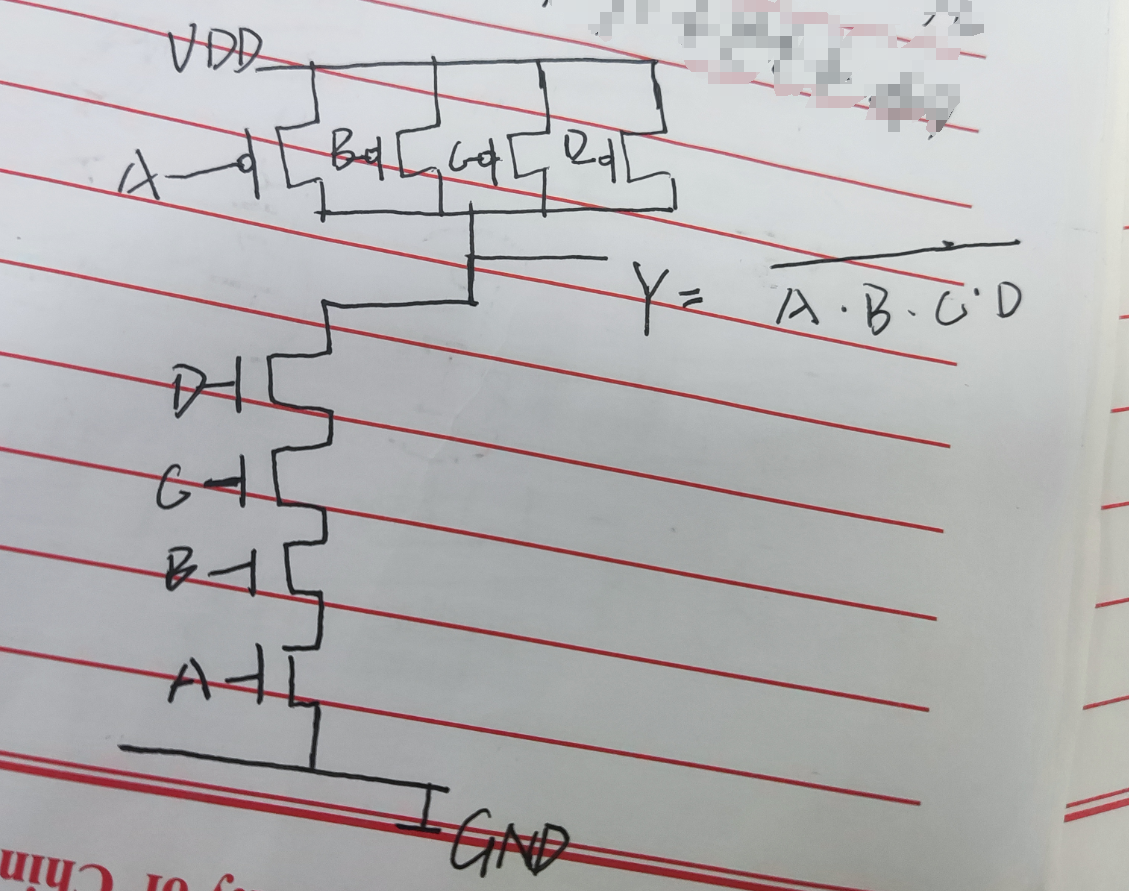

cmos电路的基本电路:

与非门的功能是对多个输入信号进行逻辑与操作,然后对结果进行取反。

或非门的功能是对多个输入信号进行逻辑或操作,然后对结果进行取反。

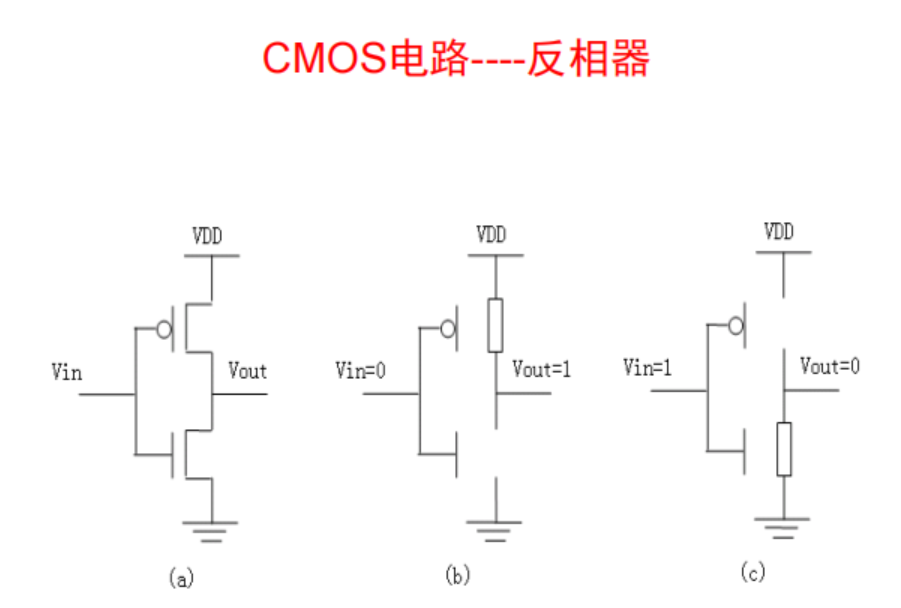

非门(NOT gate),也称为反相器(inverter)

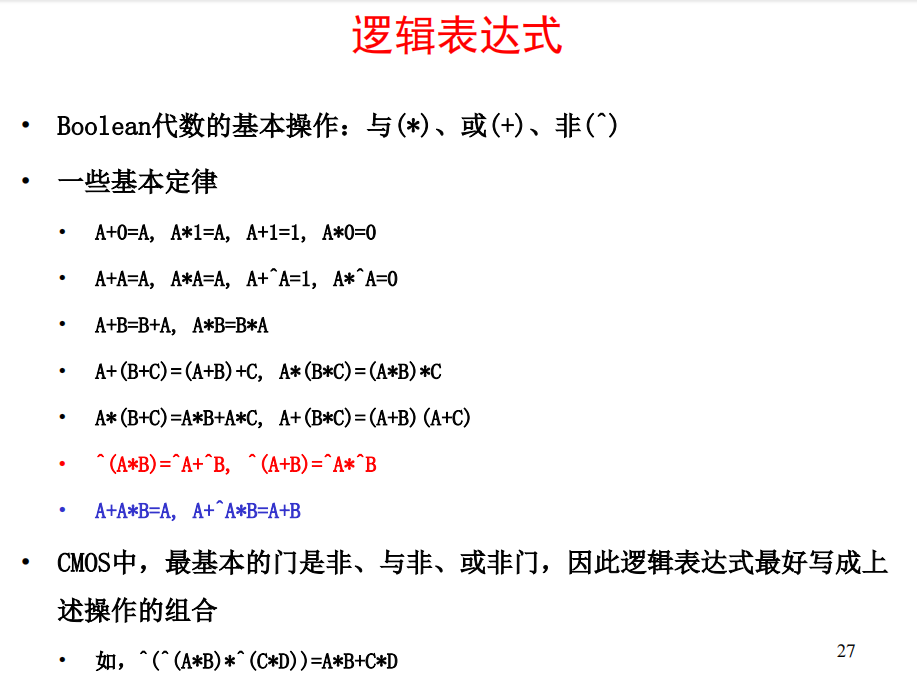

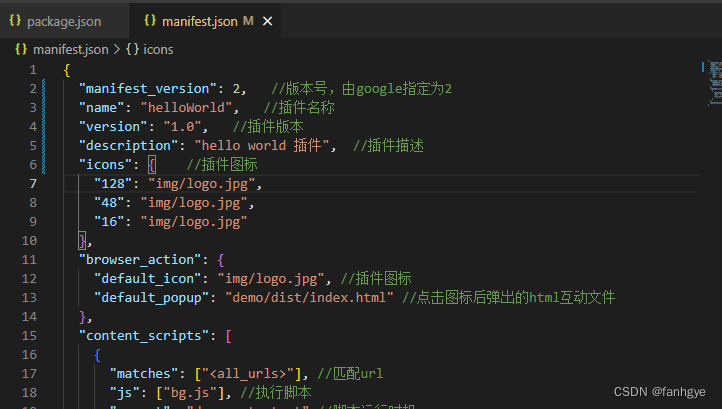

将表达式用CMOS支持的门表示

所以与门有两级延迟,因为

与门需要用与非门和非门串联实现

或门需要用或非门和非门串联实现

上图中重要的这一条,AB的与的非等于AB分别取非然后或,相当于非 把括号里面的东西都非了一遍

AB的或的非,等于AB分别非的与

怎么画

难道这样表示

如果是反向n管变成p管,串联变成并联,接地GND变成接入VDD,

都是N管接地,P管接电

正反逻辑串联等于整个表达式的非

如上图,下面一半是N管的表达,上面一半是P管的表达,正反逻辑串联起来,得到表达式的非

两级与非表达与或

例子

这个用了8个晶体管,因为

是这个与非门的电路图

题型二、 第二章触发器相关计算(较难,可能不考)给出一个触发器,然后给出延迟

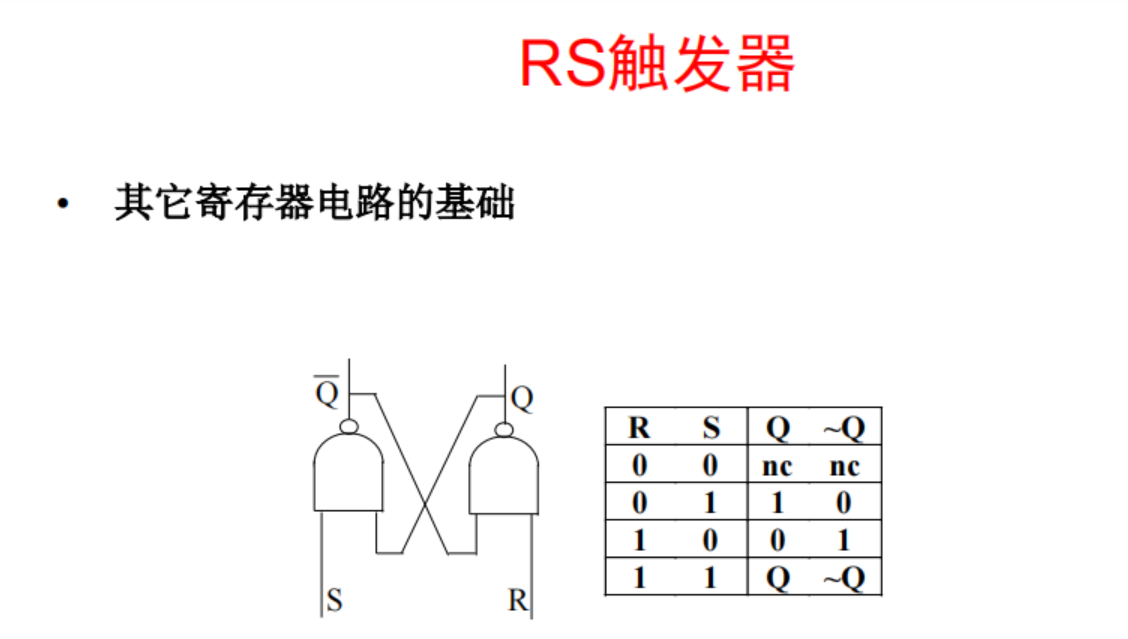

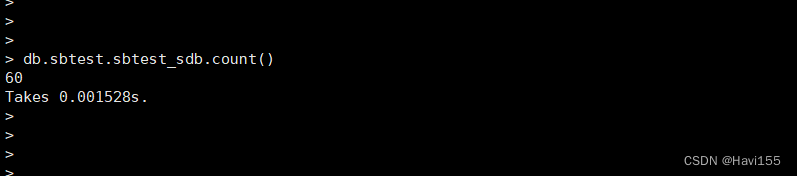

2.1 RS触发器

nc表示not care 不关心状态

R表示reset,S表示Setup

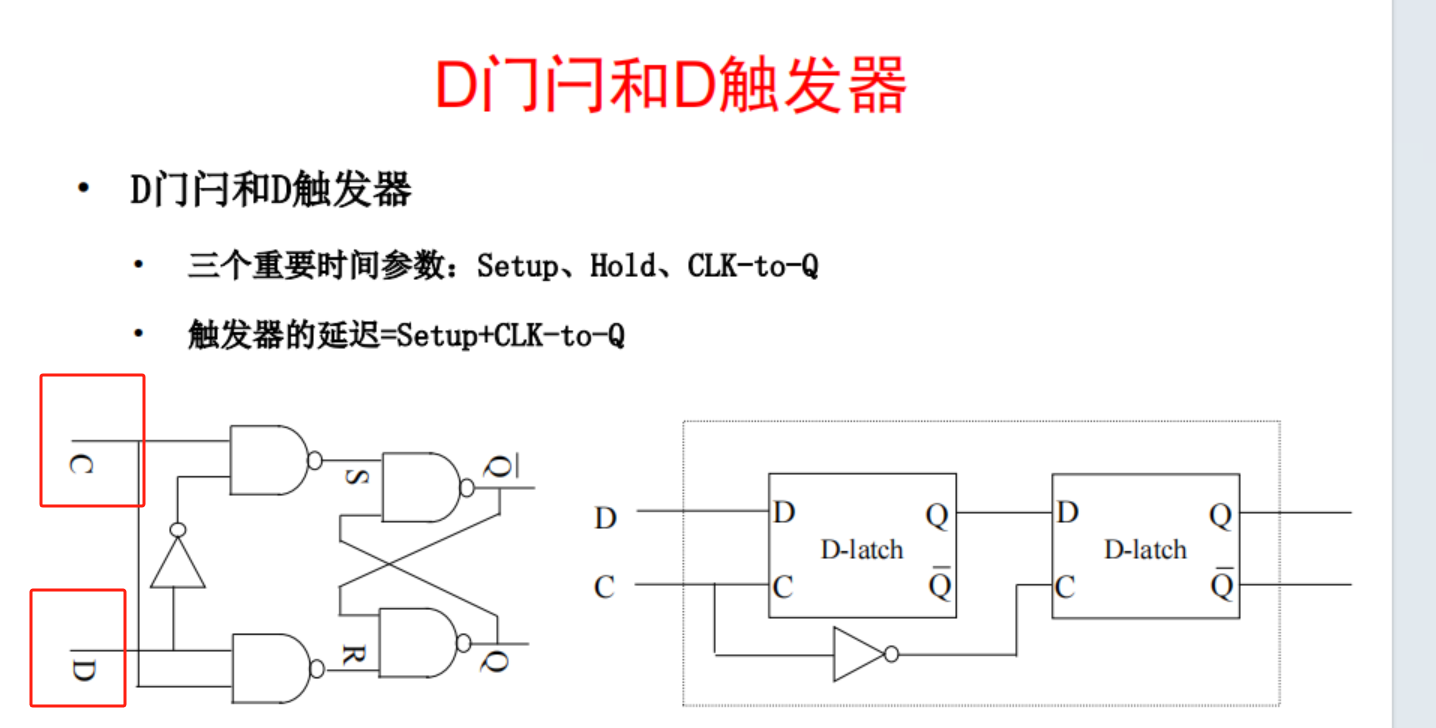

RS触发器组合形成D触发器

C为时钟,D是数据,个人感觉C的意思更像是Control,控制

意思是,在C等于1的时候,D能把值传递给Q,如果C=0,S和R一直等于1,原来的值不变

这是一个非门,不是二极管!!

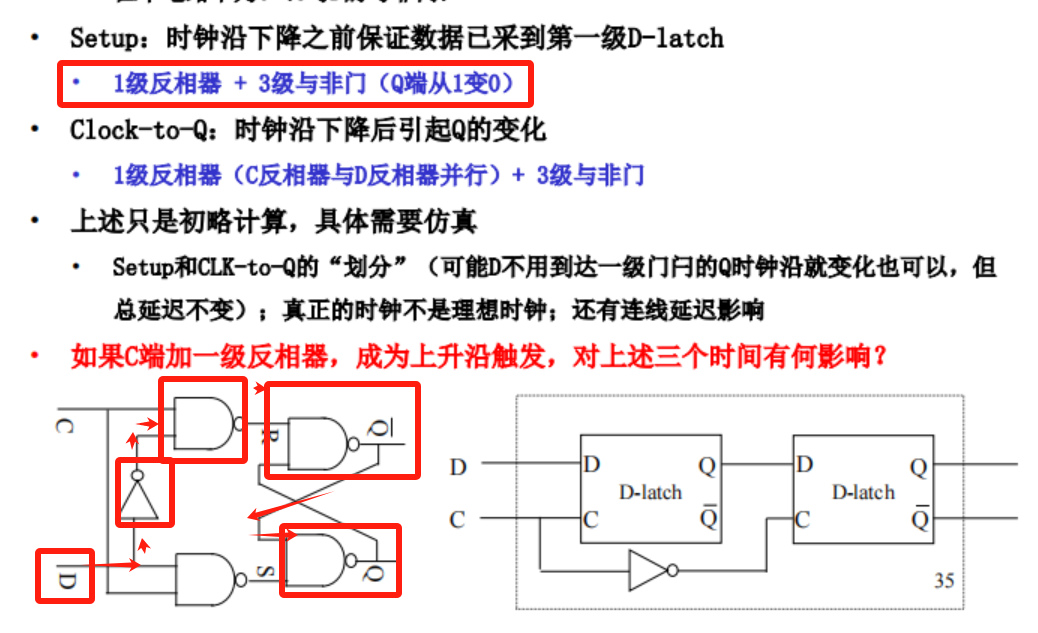

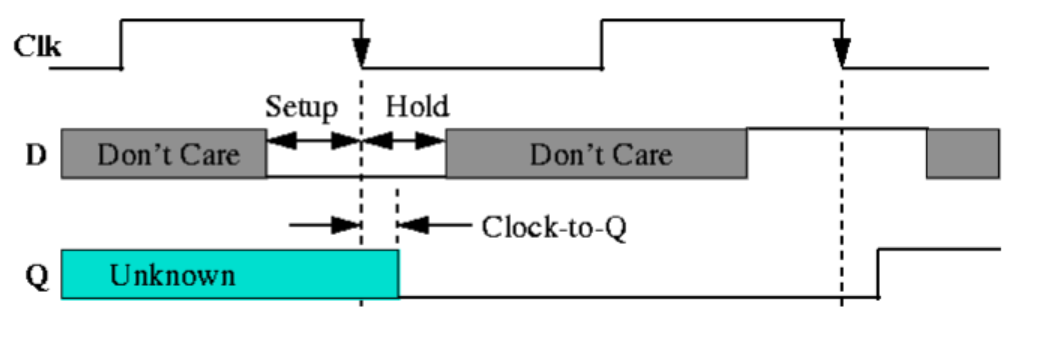

相关参数理解和计算

之前写verilog在FPGA上仿真就碰到过这个情况,上升沿来了,但是值没有存好,今天正好看看

setup time:

里面(这样下一回合时钟过来从1变零的时候,触发锁存锁的就是正确的值),因为后面C变成0之后,就不能再存数据了。D的值在被采集采集完毕之前,需要setup坚挺的时间,我的理解是需要的采集到第一个Q的需要的时间。

hold time:

想要稳定采集到D之前的值,那么在时钟的下降沿(因为图中的C端没有接反相器,是下降沿触发储存D的数据)之后的一段时间内,D不能变化,因为控制信号沿着下图所示路径到达与或们需要时间,如果是下降沿触发,C端还需要一个反相器,延迟就从0变成一个反相器的延迟,两个门的延迟

clock to q:

是在下图

触发器的延迟等于setuptime + clock to q,但是也要保持住hold time

给C增加一个反相器,hold time 加一级, setup 就可以减一级,clock to q 增加一级

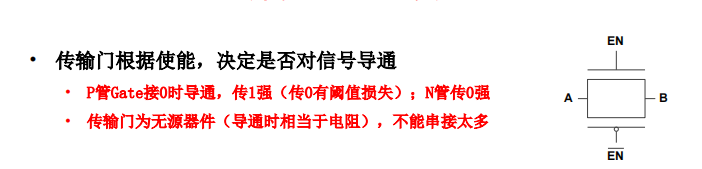

这个传输门算是一个二极管,不过选择的是高低电平是否能通过

Tlh,time from low to high 时间从低到高

题型三、使用LL/SC的同步原语

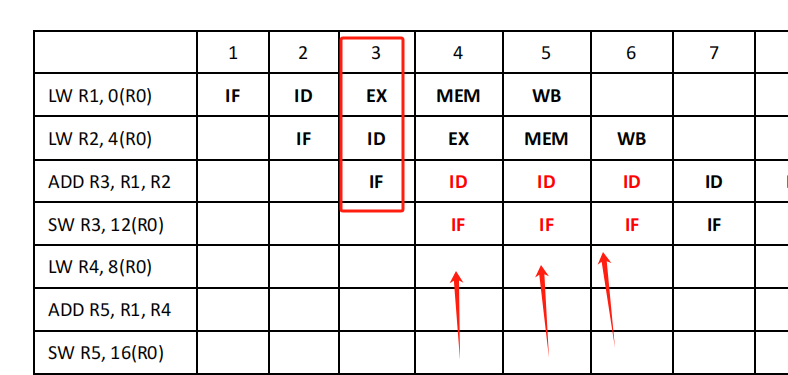

题型四、静态流水线时空图和代码流水线优化

1、一般的指令,执行了之后就能前递给另一条指令的EX执行级

2、load 指令会是要在MEM 级才能拿到值,然后用于前递的。

3、黑色字体的一般是和别的一起组合,红色字体未必??,优先顺成一个流水线??

不对,有三个空格都可以写ID,那么就写在能写的最右边。

4、加法指令只能WB写回之后 前递到ID级吗?

无旁路,那就只能WB写回,然后传给需要的那一级的ID译码阶段

有旁路,就能直接传递到执行级

改一下,无旁路,WB写回传递给EX

有旁路,LD指令MEM级传递写回给加法指令,别的在EX执行级就可以写回给加法指令

5、单发射就是如果有两条指令都可以执行了,但是上一条指令还没执行完,下一条的执行只能等待它执行完毕才能执行,表现在时空图上就是——红字的ID和IF很多

疑问

期末考试复习题的静态流水线第三题,R0是个什么东西,先背着,看看最后一节课的视频下来恶了,能不能知道为什么

会不会有这么一种可能,不添加声明的寄存器的值,默认为零

加法指令难道一定只能前递到译码级,需要知道两个加法数的值吗?

对于加法指令,在译码阶段(Instruction Decode)只需要知道操作数的寄存器标识符(例如R1和R2),而不需要实际的操作数值。译码阶段的主要任务是解析指令并准备执行所需的操作。

为什么第一题,第一个加法指令的R2写回了,传递给的是译码ID级,第二个加法指令,前递给的是执行级呢?

猜测,WB只能给到ID,但是MEM可以前递到执行级

第二题:同一周期内寄存器的读和写能进行旁路,意味着从ID译码级就可以传递数据出去

not taken 就是预测不正确,在转移指令到了执行级,也就是 BNEZ等跳转指令 ,猜测不需要跳转到Loop,那么就会直接执行Nop指令, 等跳转指令到了EX级发现错了,再重新对正确的指令取指IF

题型五、动态流水线+循环展开

循环的延迟级大头是LD然后计算,然后写回,

得出技巧:

1、把下一级的LD一起放到前面

2、把SW偏移一下(在上面+了偏移,下面存回去的时候一定要记得修正正确,是第几第几个循环),然后放到末尾

3、循环体计算下标的指令,往计算部分塞

4、分支判断指令一定是倒数第二条,然后考虑用SW指令替代延迟槽

5、根据舒服的方法,判断是taken还是not taken

6、如果排了两个循环发现还是有问题,那就再加一个循环进去

![[足式机器人]Part2 Dr. CAN学习笔记-Advanced控制理论 Ch04-5稳定性stability-李雅普诺夫Lyapunov](https://img-blog.csdnimg.cn/direct/65aa33ac3c73453fa8e3336d3057237d.png#pic_center)

![Unity报错:[SteamVR] Not Initialized (109)的解决方法](https://img-blog.csdnimg.cn/direct/2b6f9f608eb24c6d8a1cfb60206cc9ae.png)