目录

采样保持工作原理

概念

时域响应-采保信号

采样网络的KT/C噪声

采样电容大小的选取

采样抖动(jitter)

jitter对SNR的影响

法一

法二

采样开关的种类

单MOS管

实践:Nmos导通电阻

传输门

栅压自举开关

采样技术

上极板采样

下极板采样

采样保持的电荷转移

跟踪阶段

采样时刻

保持阶段

输出

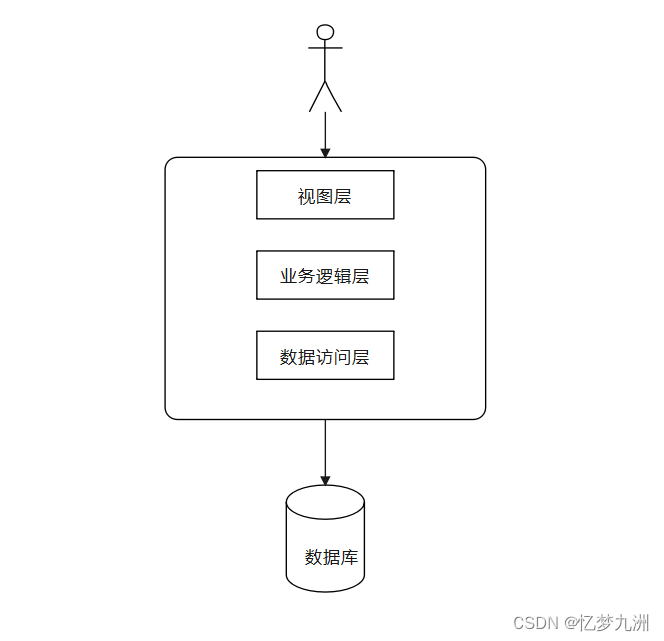

采样保持工作原理

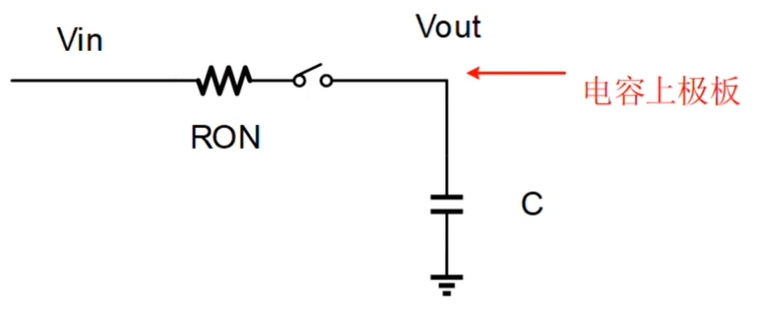

概念

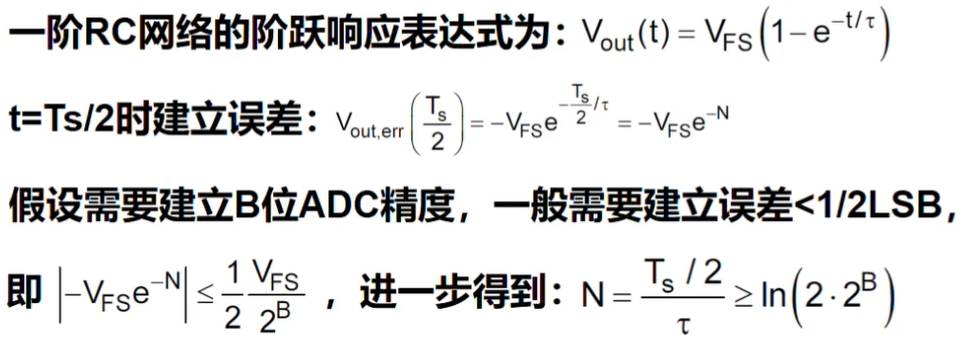

采样保持电路作用:时域离散化

跟踪阶段:开关闭合,Vout=Vin。

保持阶段:开关断开,保持电压。

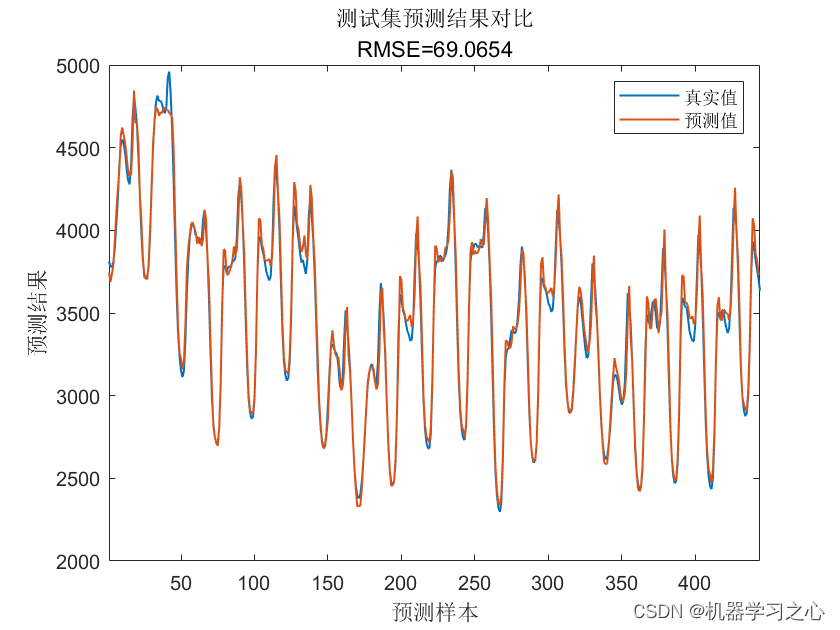

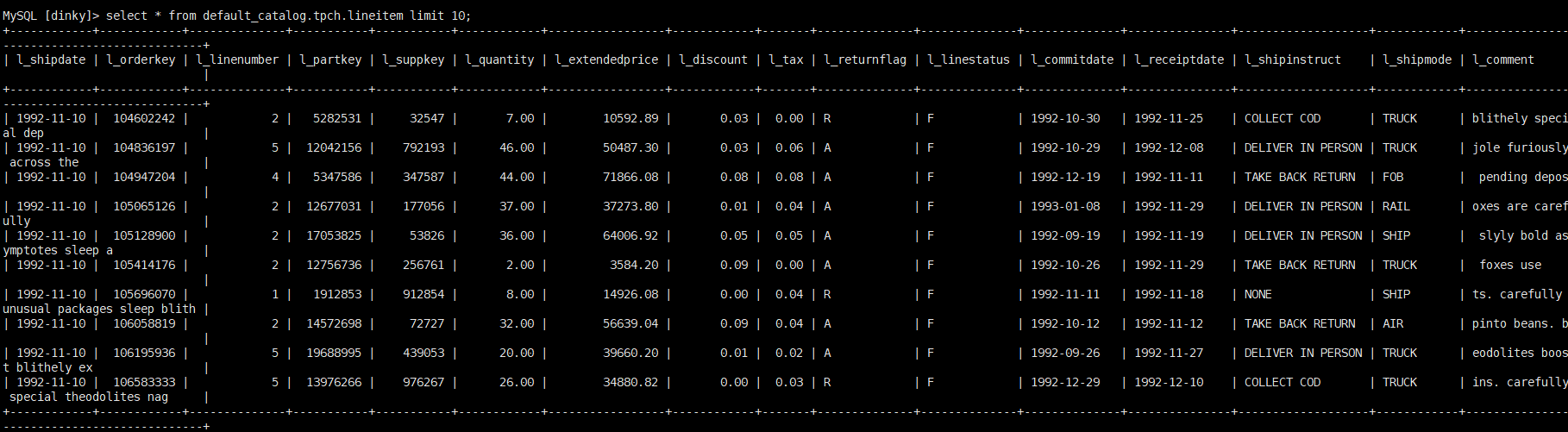

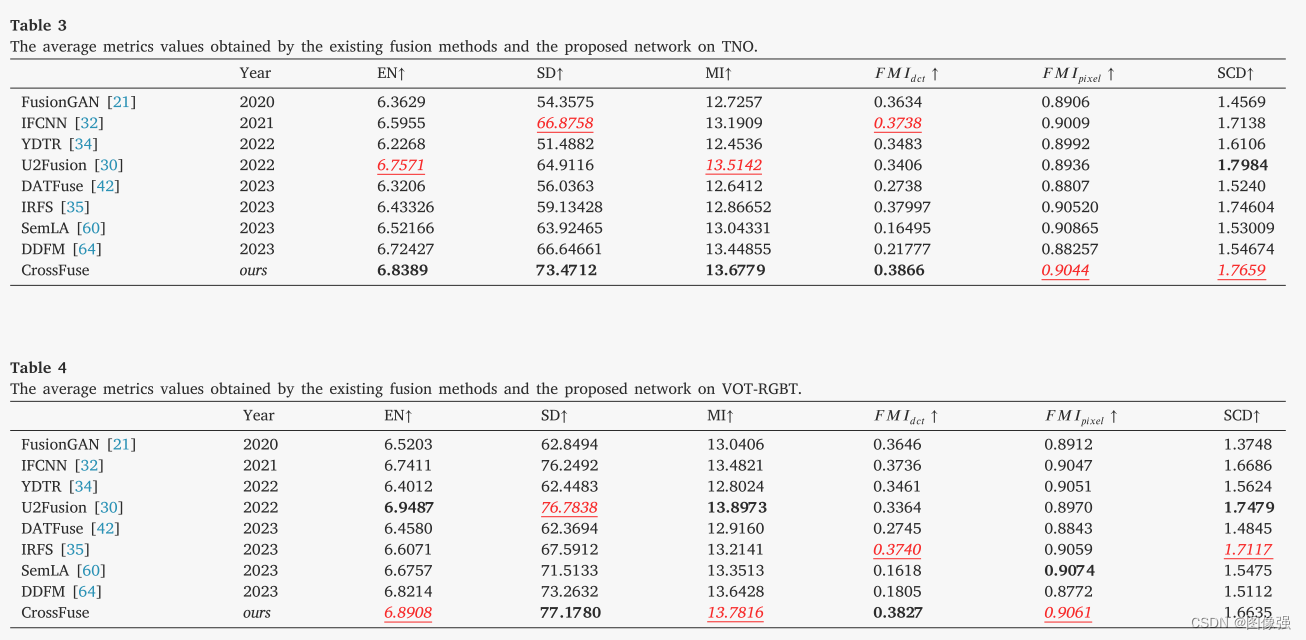

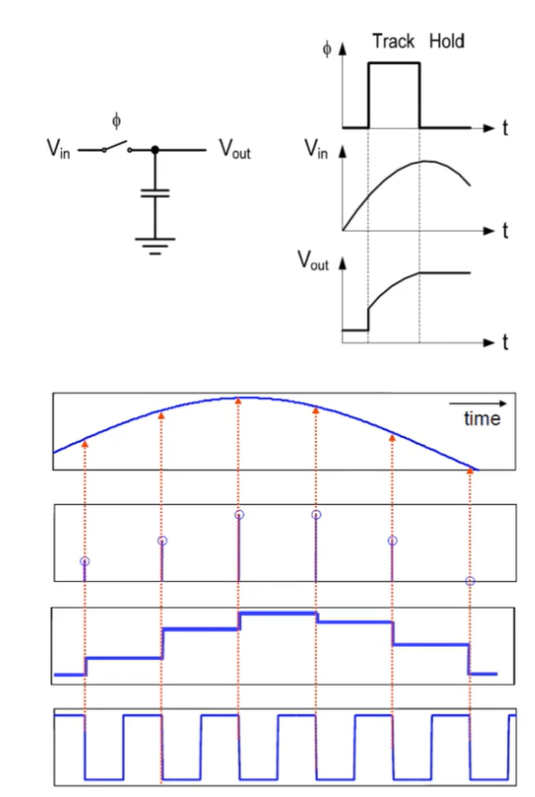

时域响应-采保信号

输入信号在采样阶段不变。

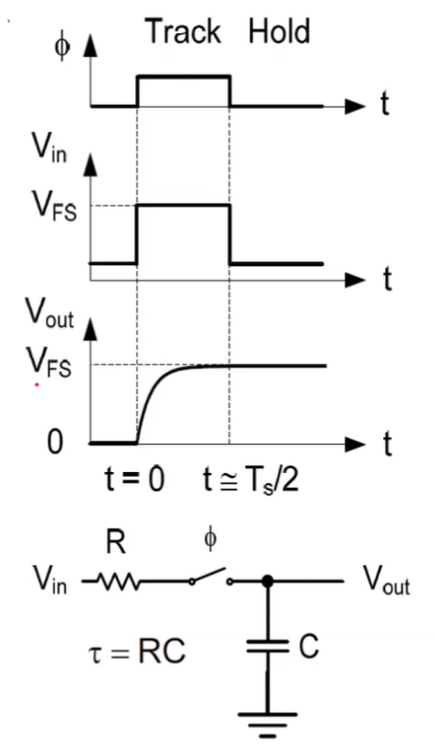

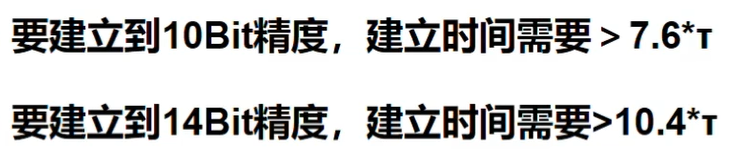

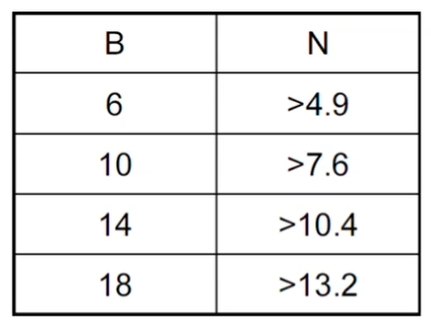

ADC精度和建立时间之间的关系:

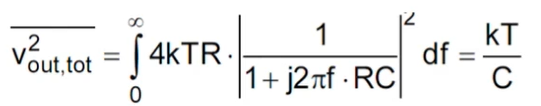

采样网络的KT/C噪声

电容不会产生噪声,电阻会产生噪声。

一阶RC网络的噪声与电阻无关,只与电容有关。

R越大,电阻噪声谱密度4KTR越大,但是一阶RC的3dB带宽1/RC也更低。所以总的积分噪声与R无关。反之亦然。

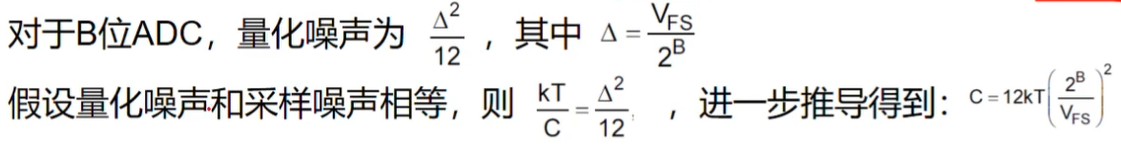

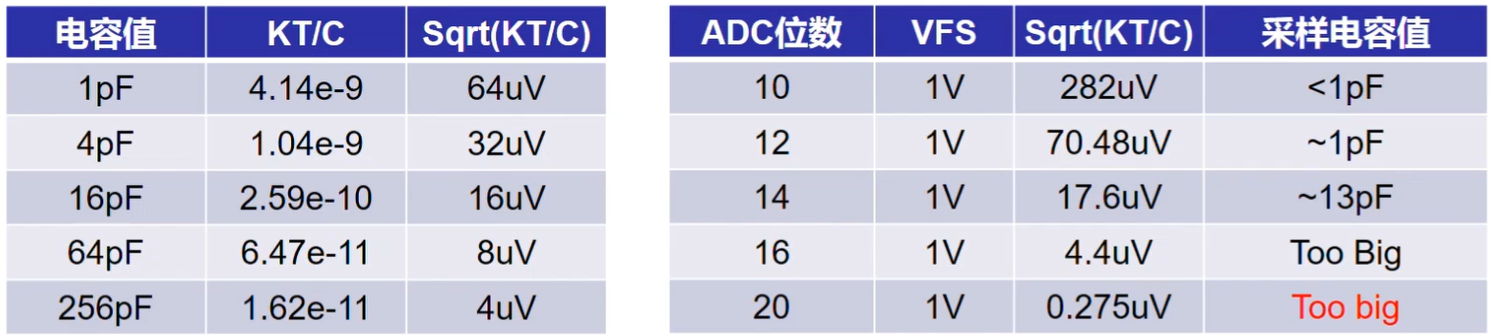

采样电容大小的选取

如何选择采样电容的大小?

ADC设计中,一般遵循以下规则:噪声不能大于量化噪声。

根据ADC位数选择采样电容值的大小:

电容每增加四倍,根号下KT/C减小一半。

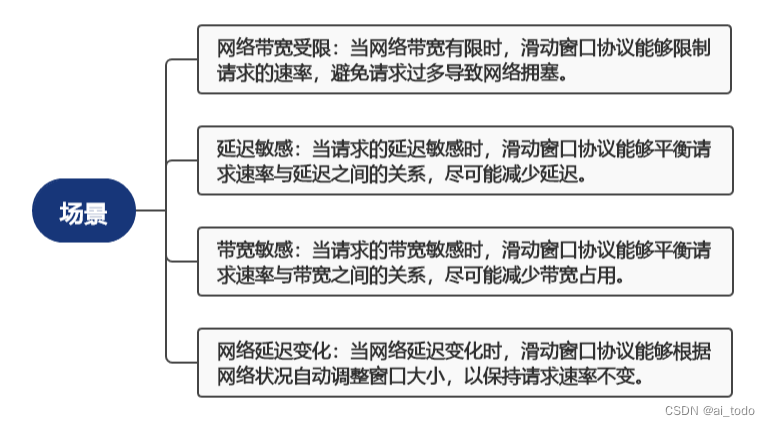

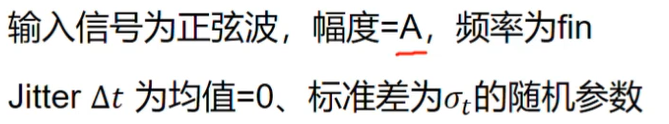

采样抖动(jitter)

时钟抖动:不存在理想的采样时钟,真是的clock的上升沿和下降沿有一定范围的不确定性,

ADC的噪声源:量化噪声、热噪声、采样时钟jitter带来的采样误差。

jitter对SNR的影响

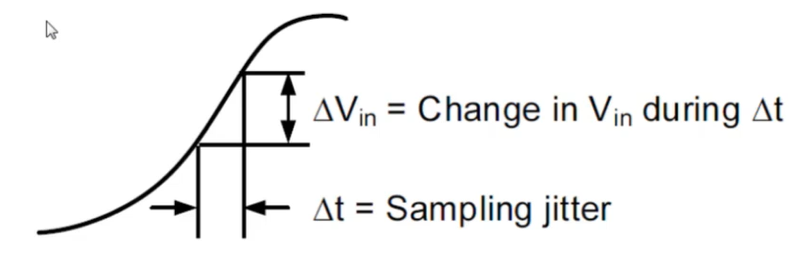

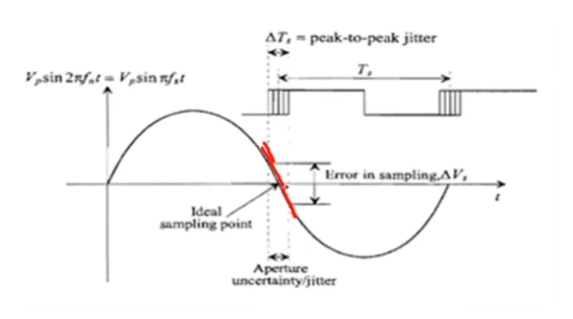

法一

仅仅考虑jitter的影响,对输入信号求导再乘时间就是采样电压误差,对其求功率就是误差功率。

SNR=信号功率/噪声功率

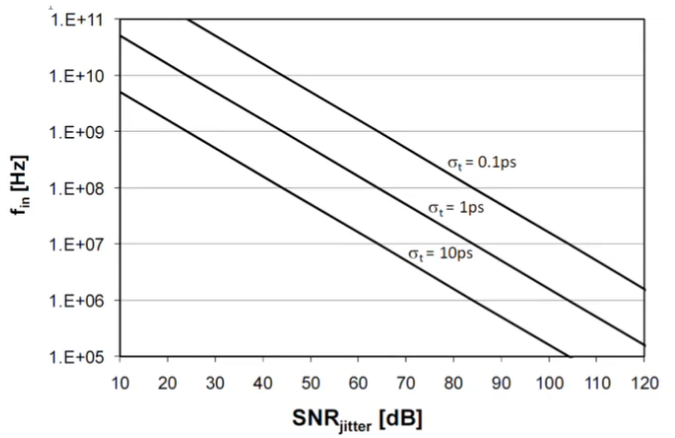

jitter和SNR的关系:

在jitter一定的情况下,信号频率越高,SNR越低

在信号频率一定的情况下,jitter越大,SNR越低。

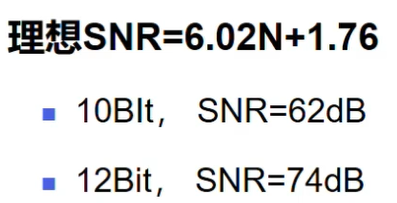

理想ADC信噪比SNR与位数的关系:

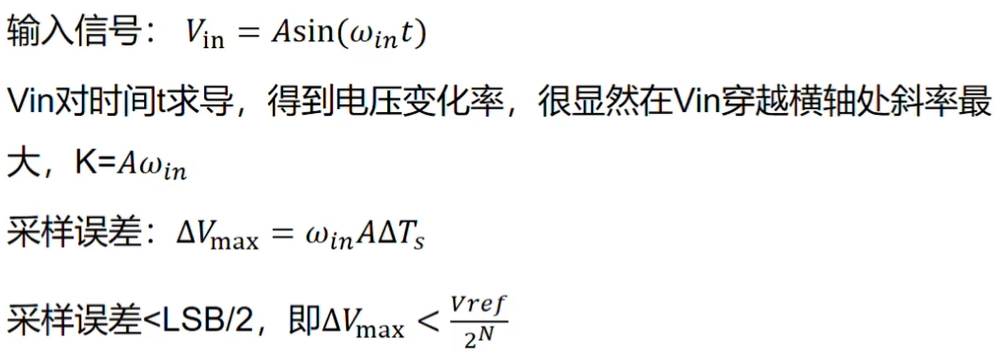

法二

使采样jitter引入的误差小于1/2 LSB。该法较为严格

对输入信号求导,考虑极端情况,得到电压变化率最大的时候的值,使该值小于LSB/2。

采样开关的种类

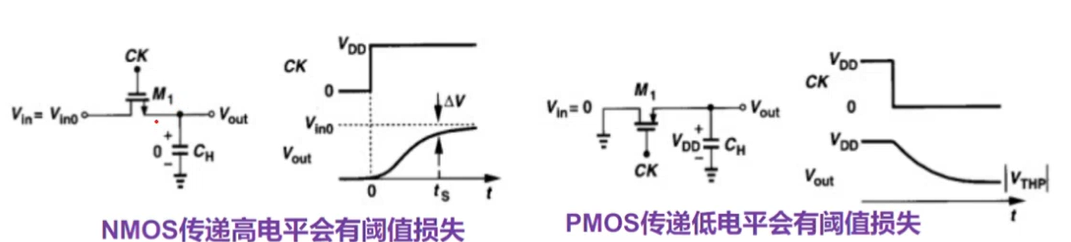

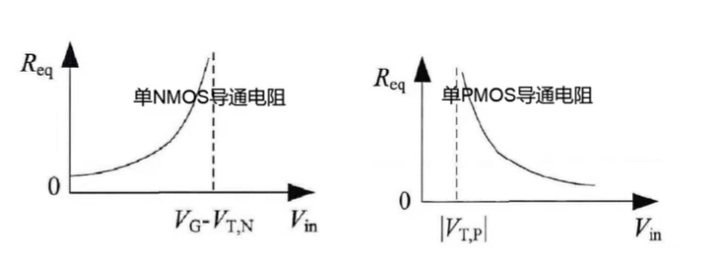

单MOS管

全摆幅范围内线性度较差

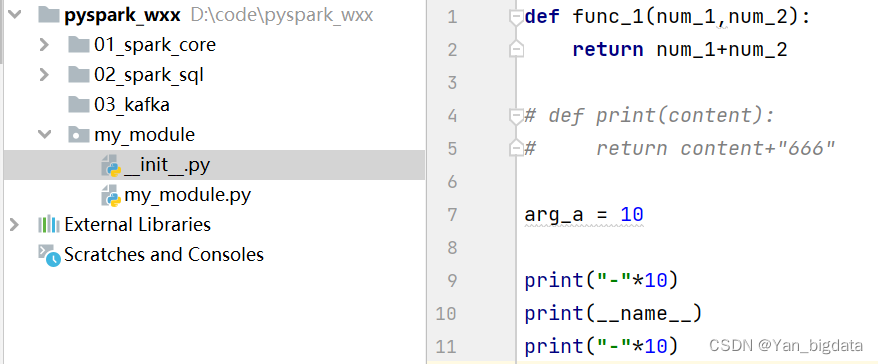

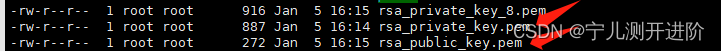

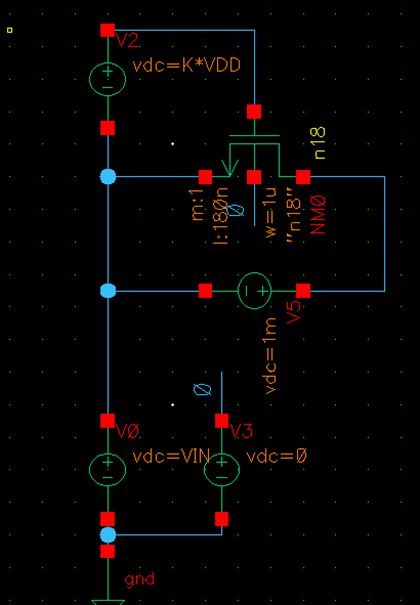

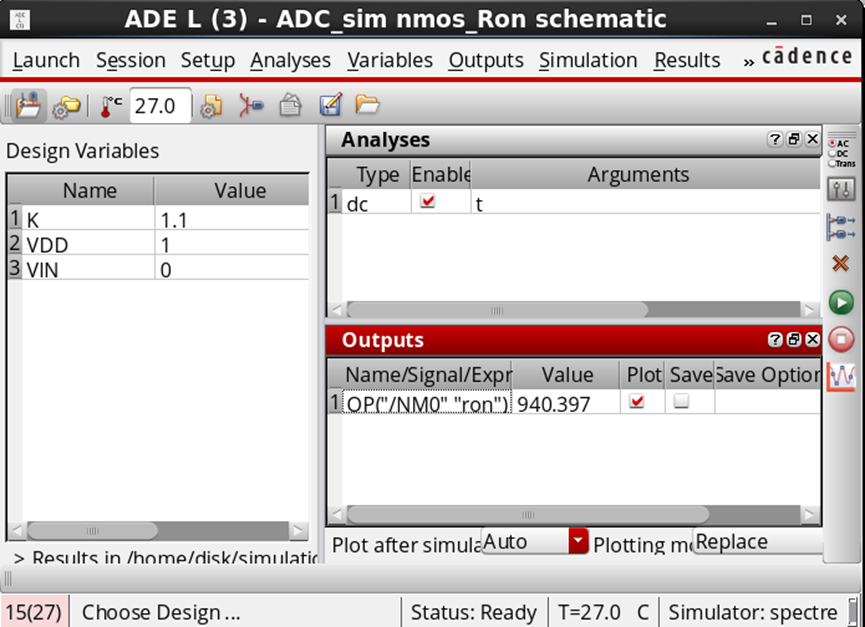

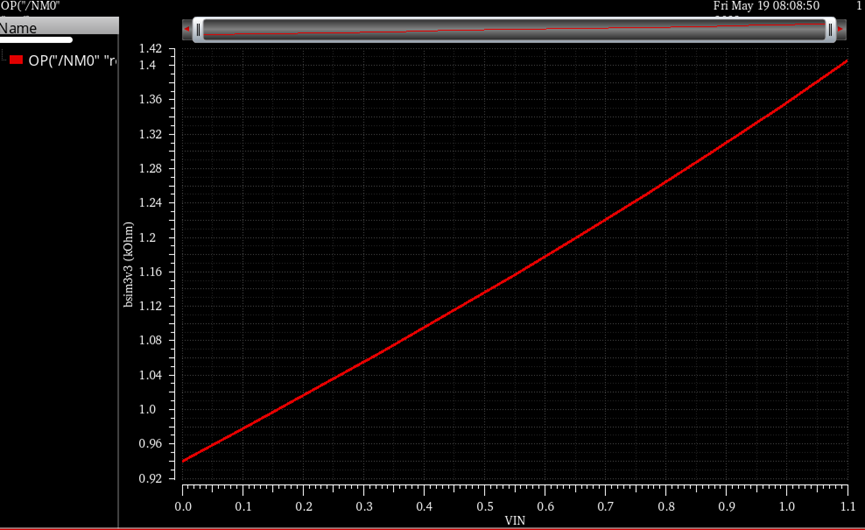

实践:Nmos导通电阻

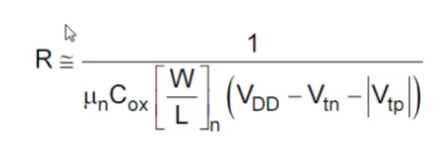

可以看到输入为0的时候,即不考虑衬底偏置效应的时候,导通电阻为940.397

对VIN做参数扫描,可以看到考虑衬底偏置效应后的导通电阻的变化情况在VIN=1.1时,衬底偏置效应最大为1.4kΩ,Vth变大,导致导通电阻变大。

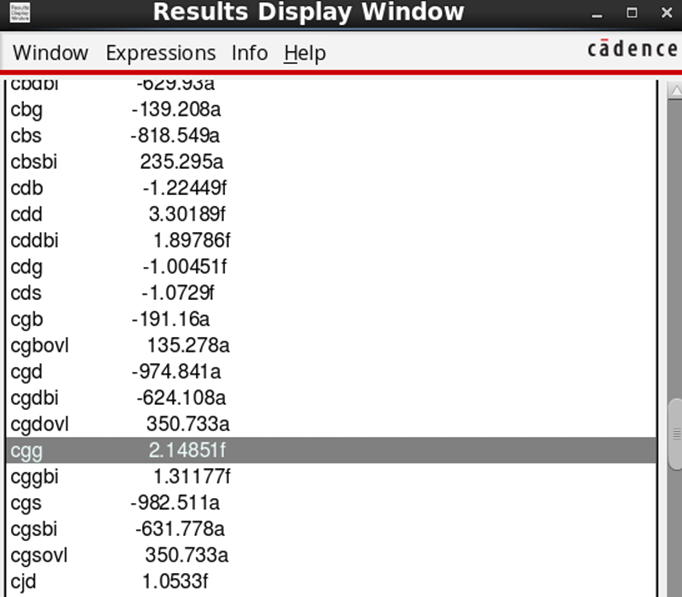

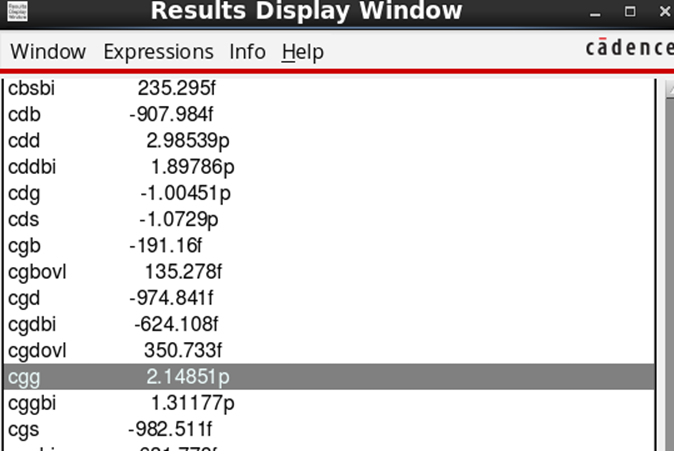

打印静态工作点可以看到cgg(gate电容),gate电容为2.14f,电容太小是因为MOS管尺寸太小。

增大MOS管尺寸,m=10,finger=100,得到cgg,用cgg/面积,就得到

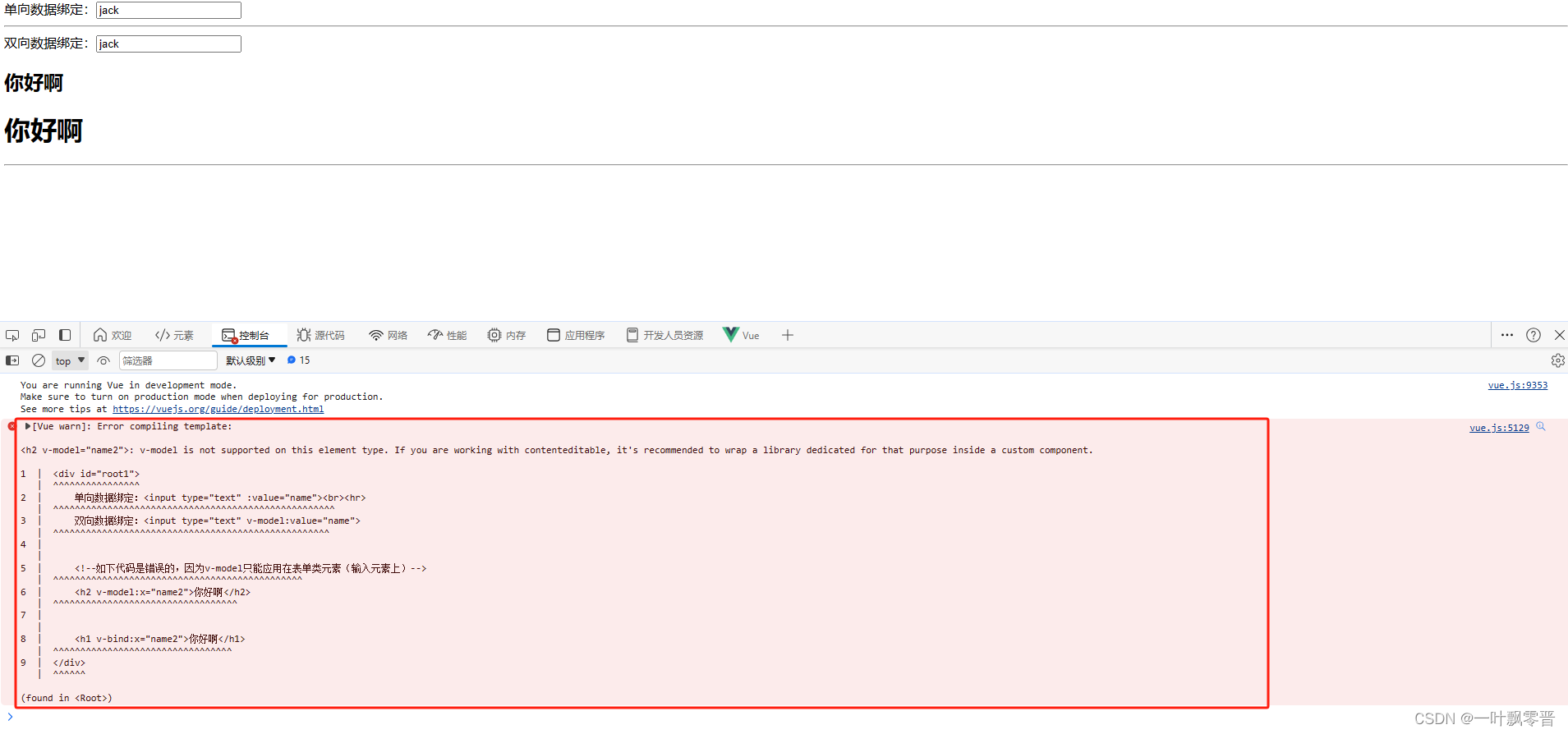

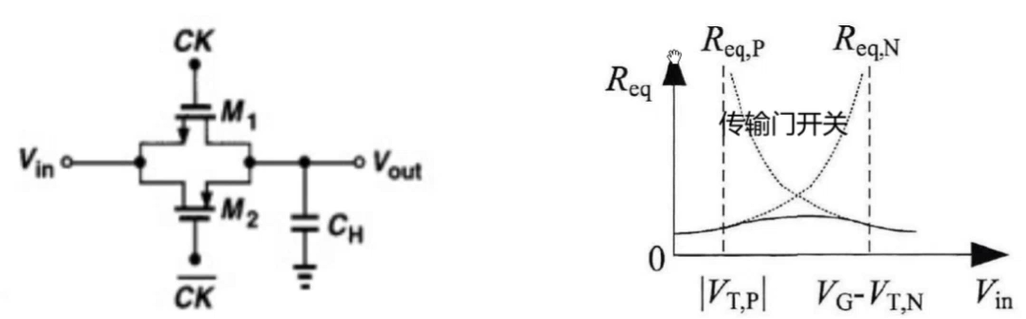

传输门

PMOS:NMOS宽长比=4:1时,才能保持马鞍形阻抗。但是,在先进低电压工艺下,NMOS和PMOS在中间电平附近的时候不导通,导致导通阻抗很大。

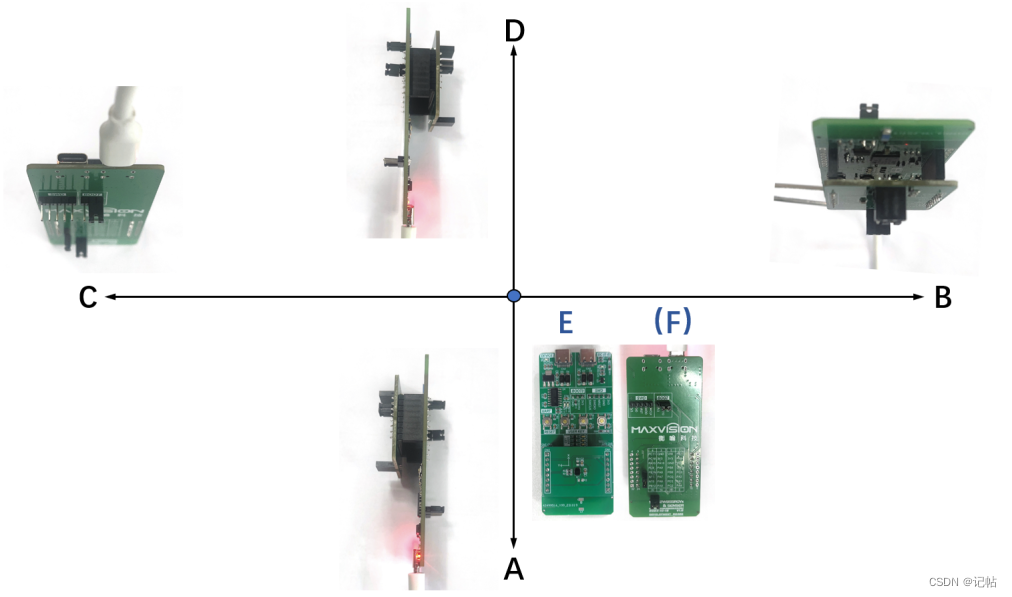

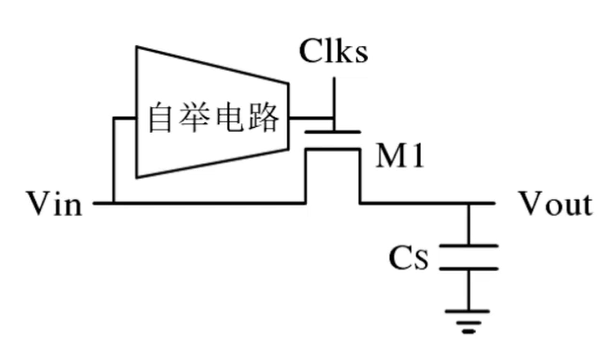

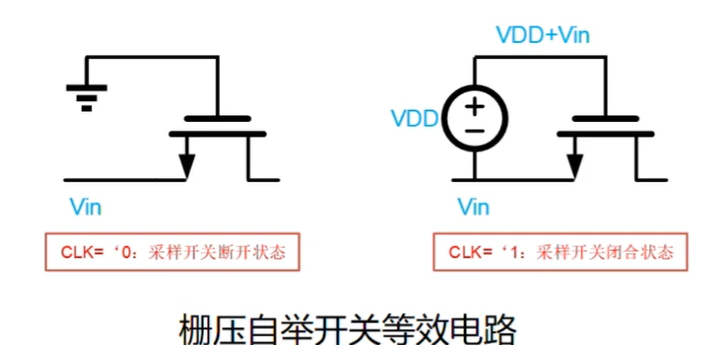

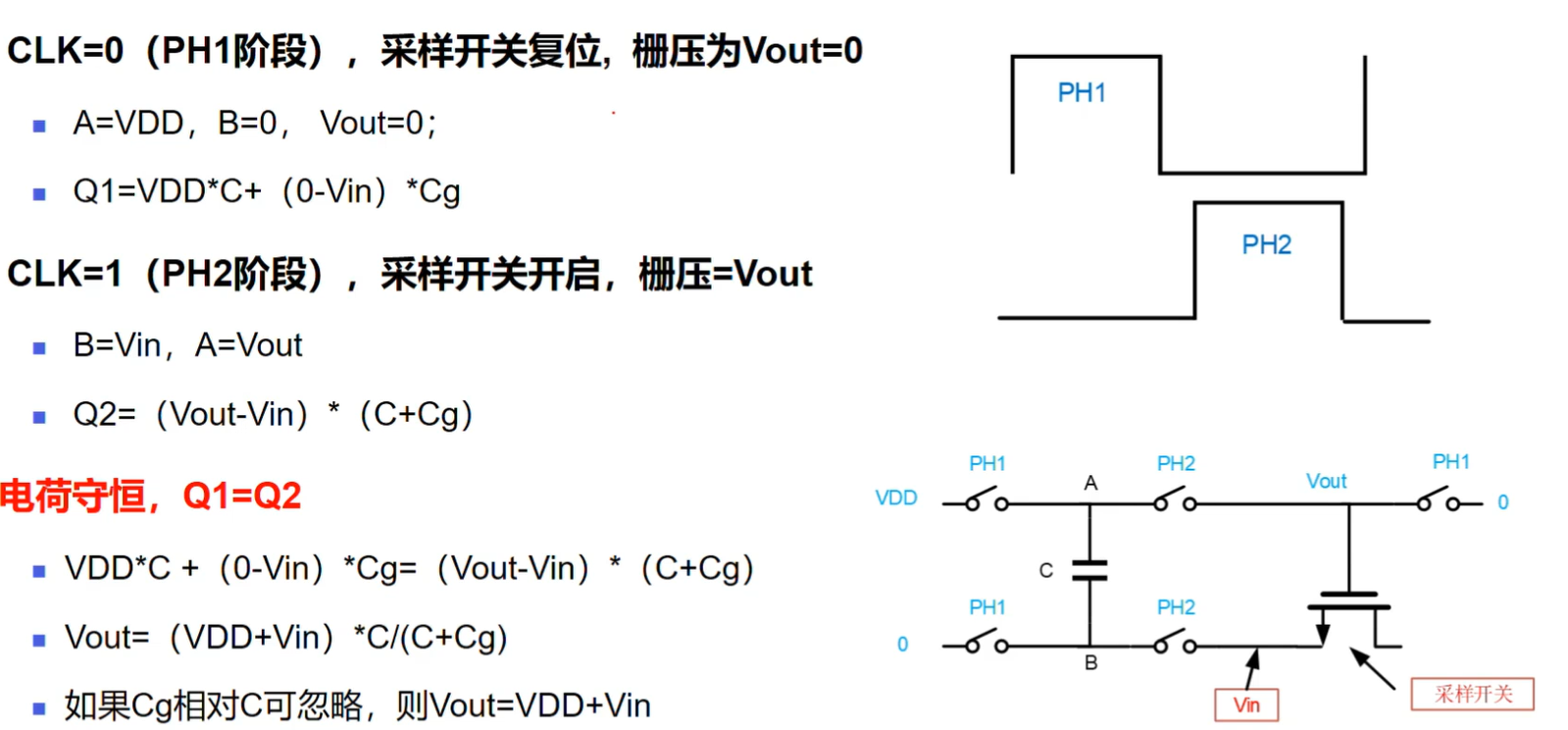

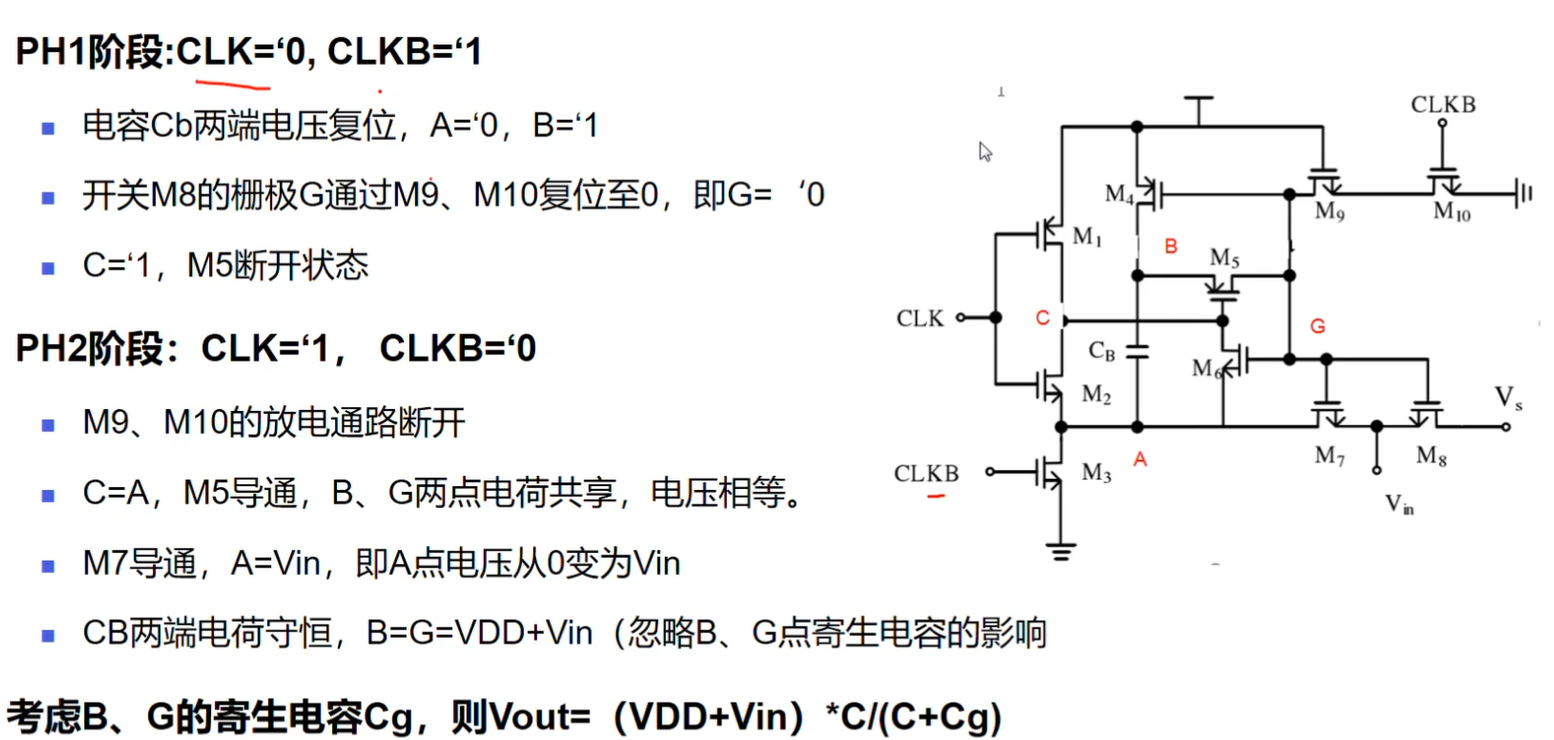

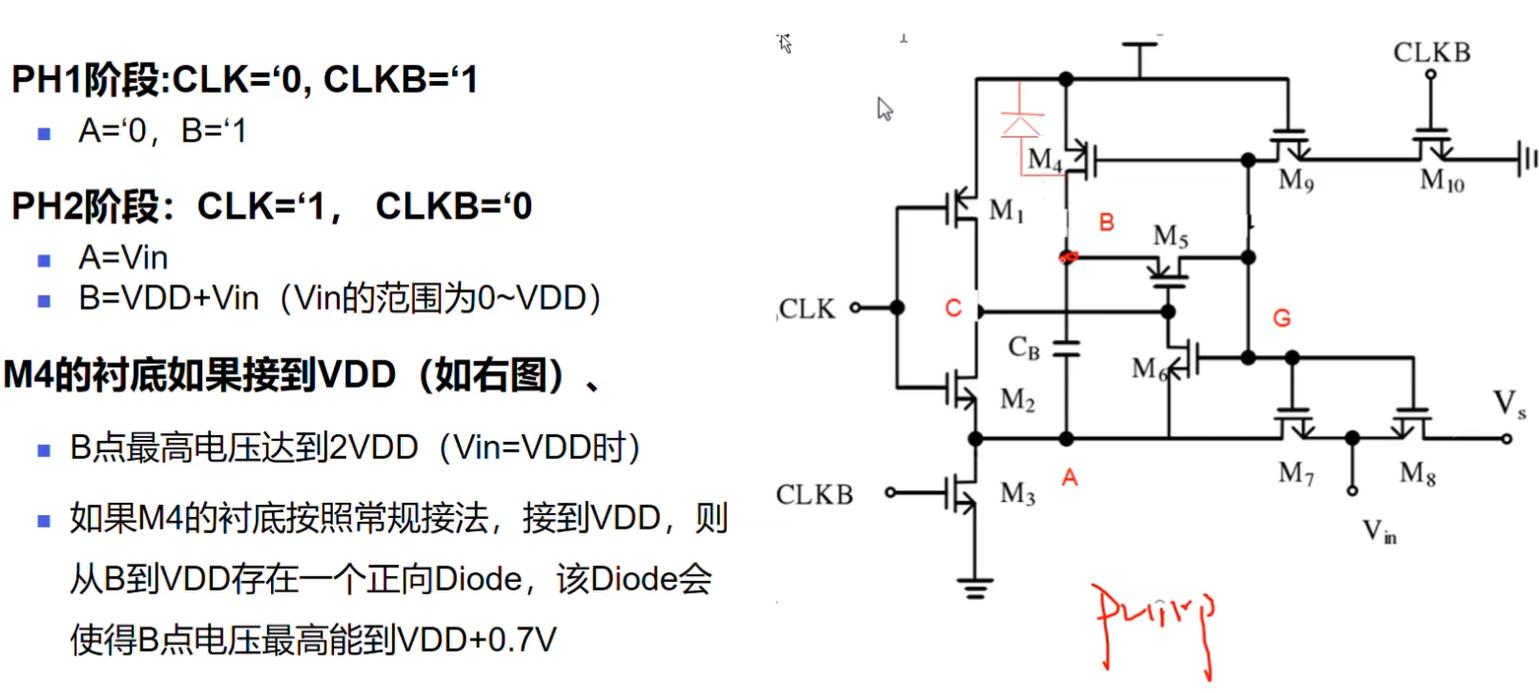

栅压自举开关

目的:将MOS管的Vgs保持为一个恒定值。

理论原理

电路实现

栅极自举开关,需要将M4和M5管的衬底与B点短接(接电路最高电位,该电路最高电位是B点而不是VDD),保证B点能够到大2VDD。

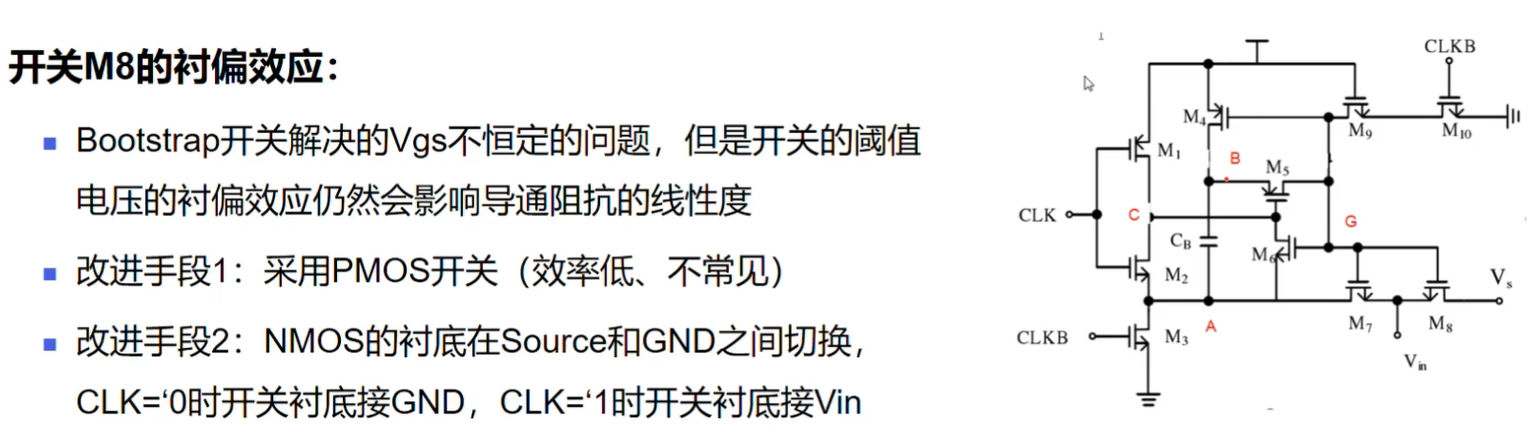

M8连接输入和输出,其衬偏效应会影响导通阻抗的线性度,因此需要改进

可以用PMOS开关

也可以使NMOS衬底在source和GND之间切换

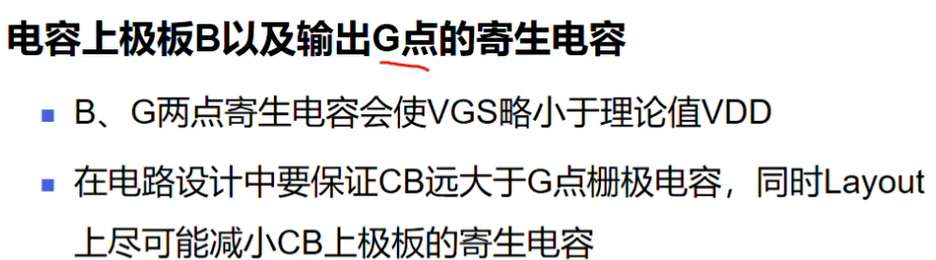

首先确定M7和M8的寄生电容,CB取寄生电容的几十倍。

采样技术

上极板采样

非理想特性:开关断开瞬间的沟道电荷、时钟馈通、上极板技术采样精度限制在10位左右。

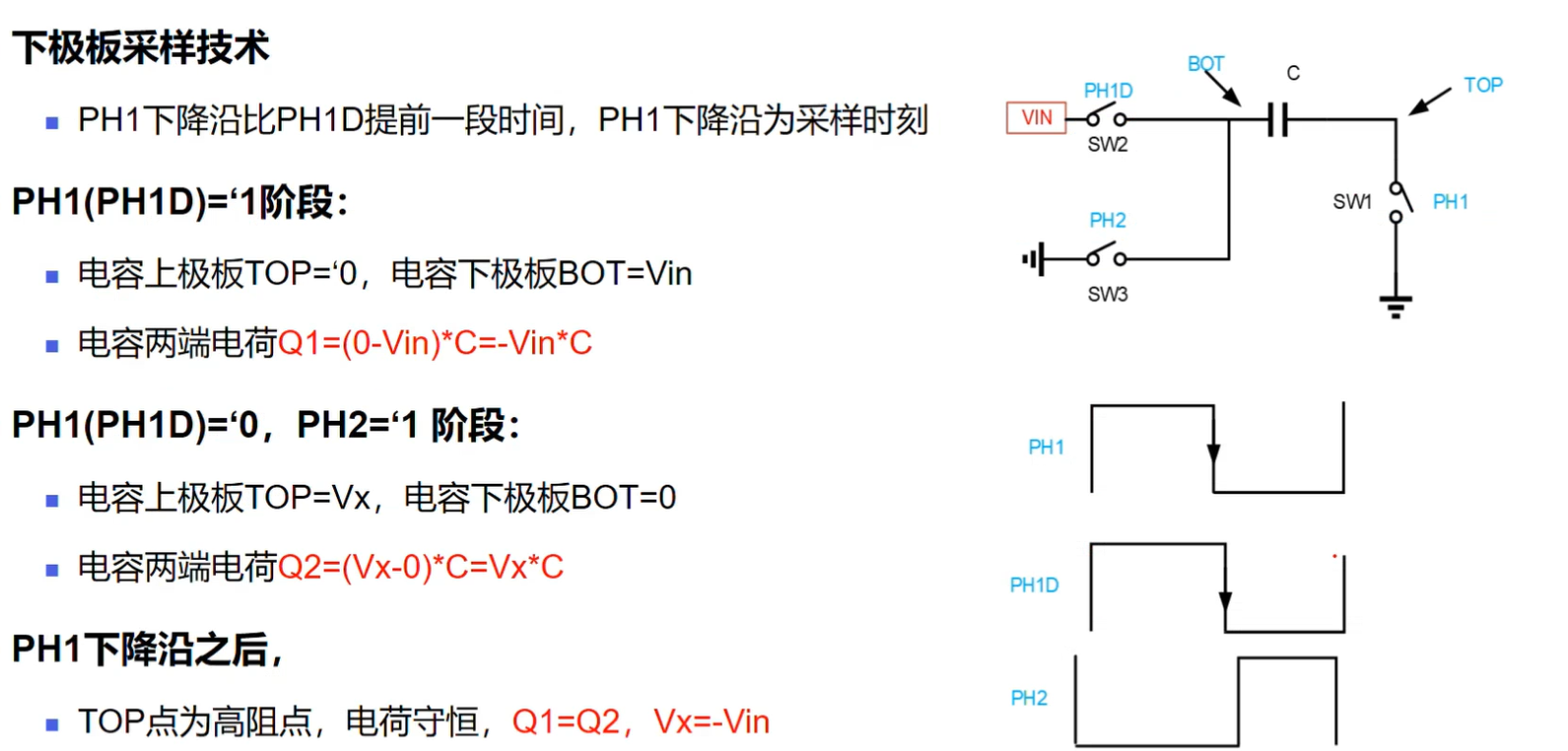

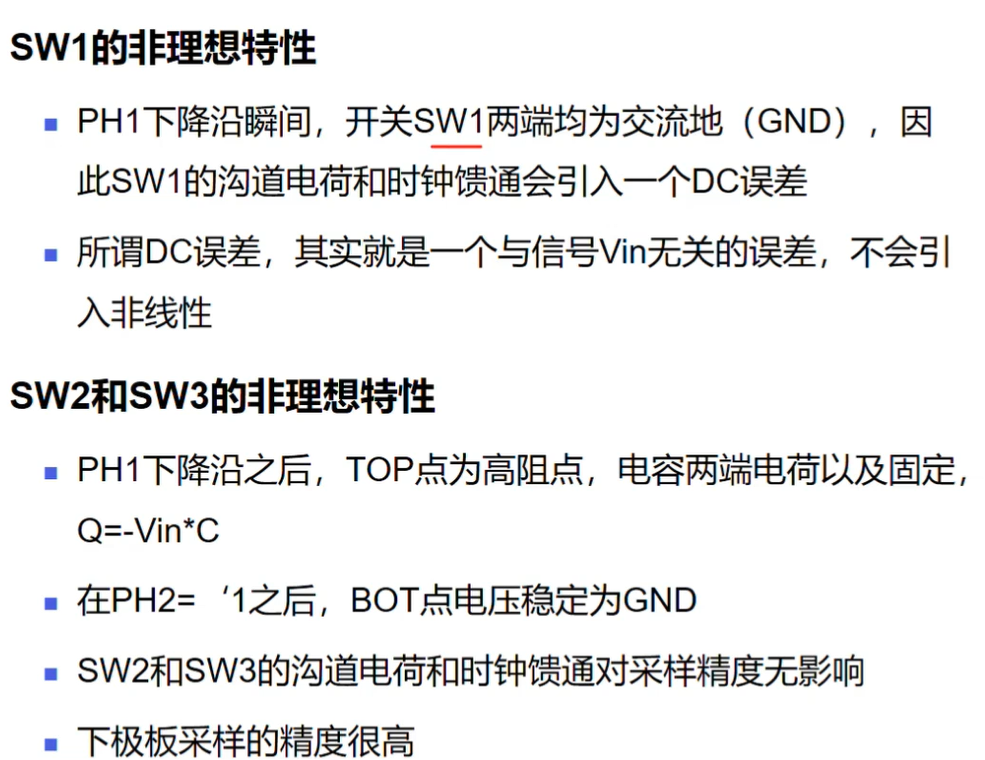

下极板采样

SW3开关的左端也可以接共模信号

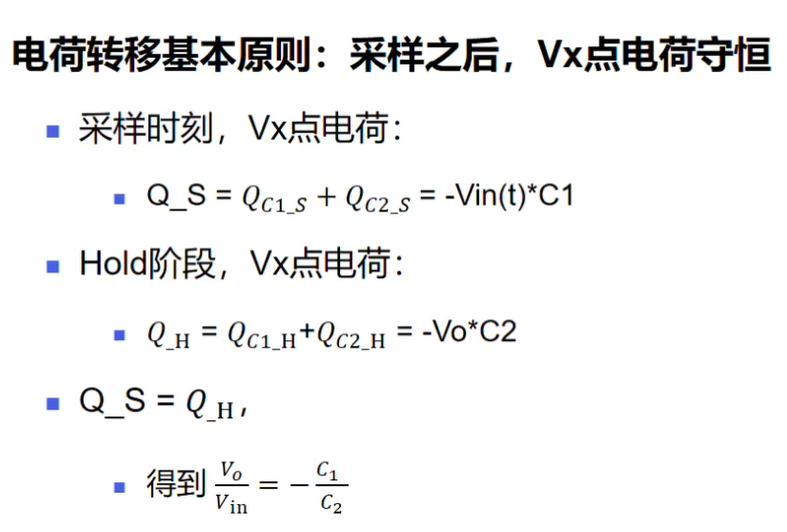

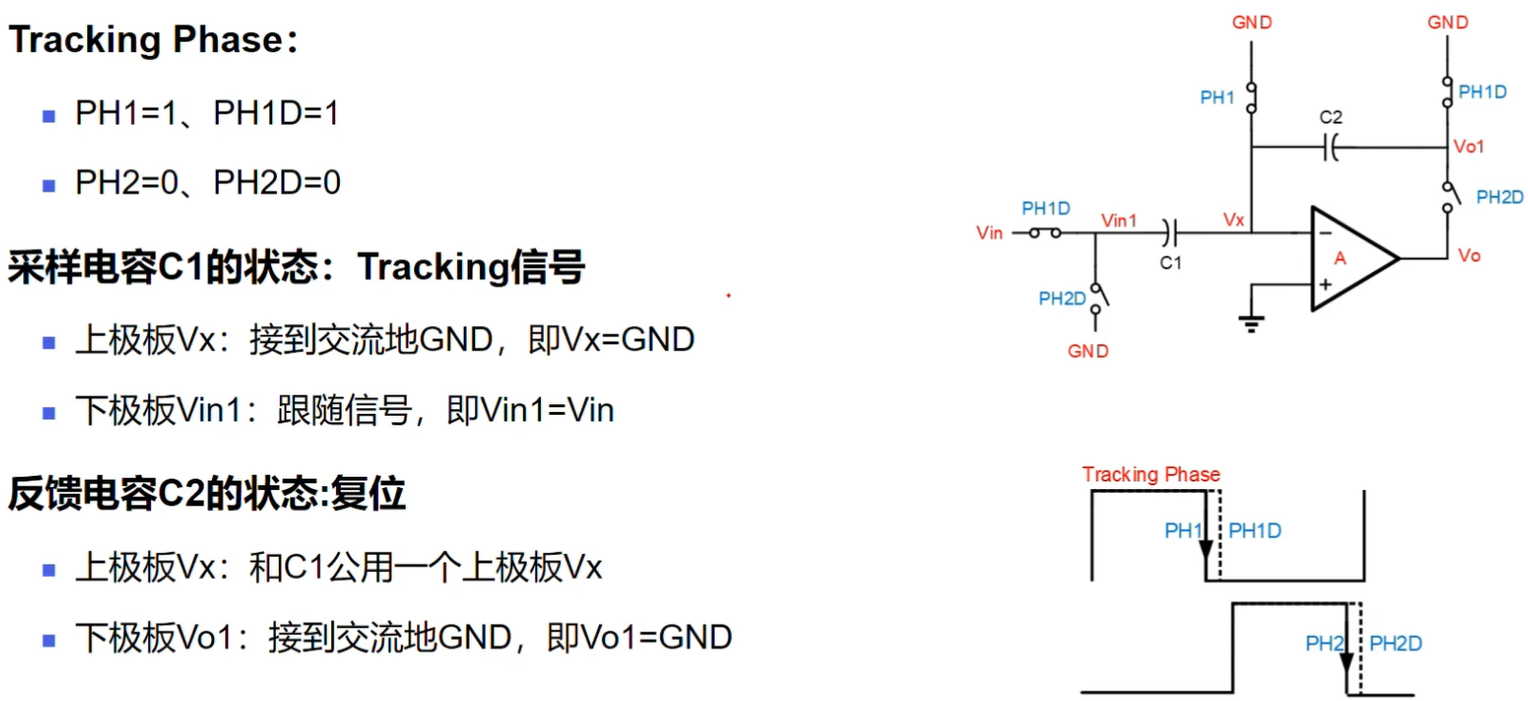

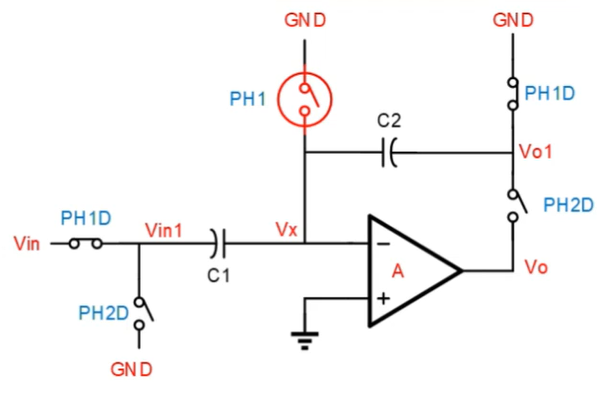

采样保持的电荷转移

跟踪阶段

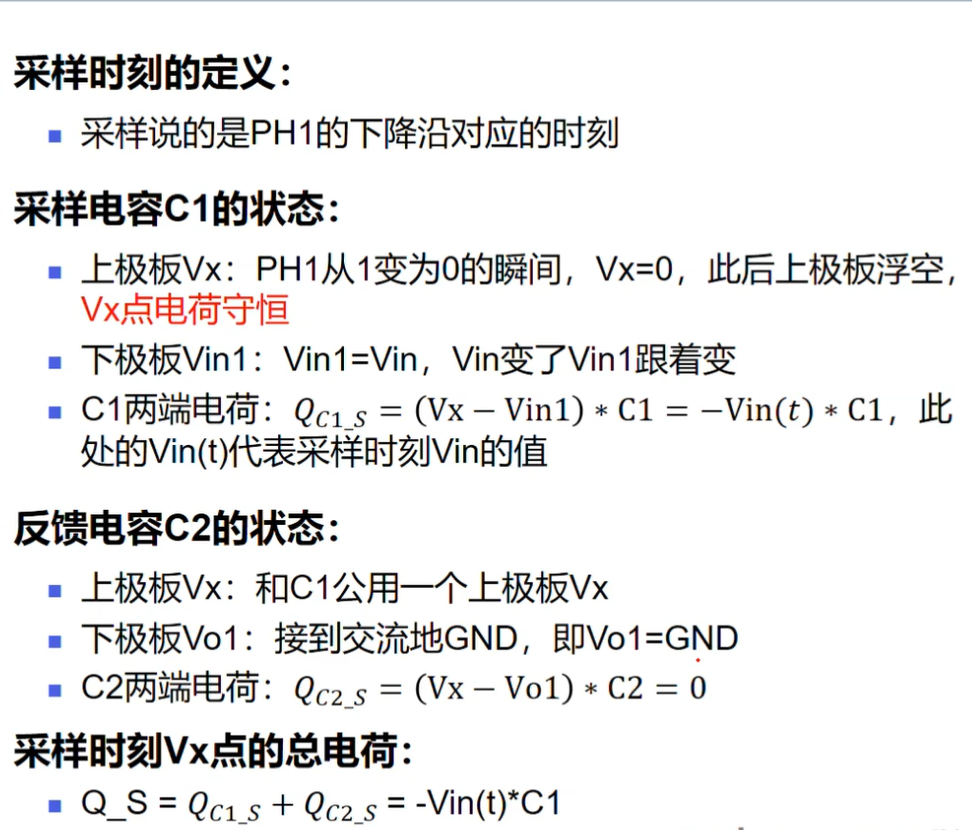

采样时刻

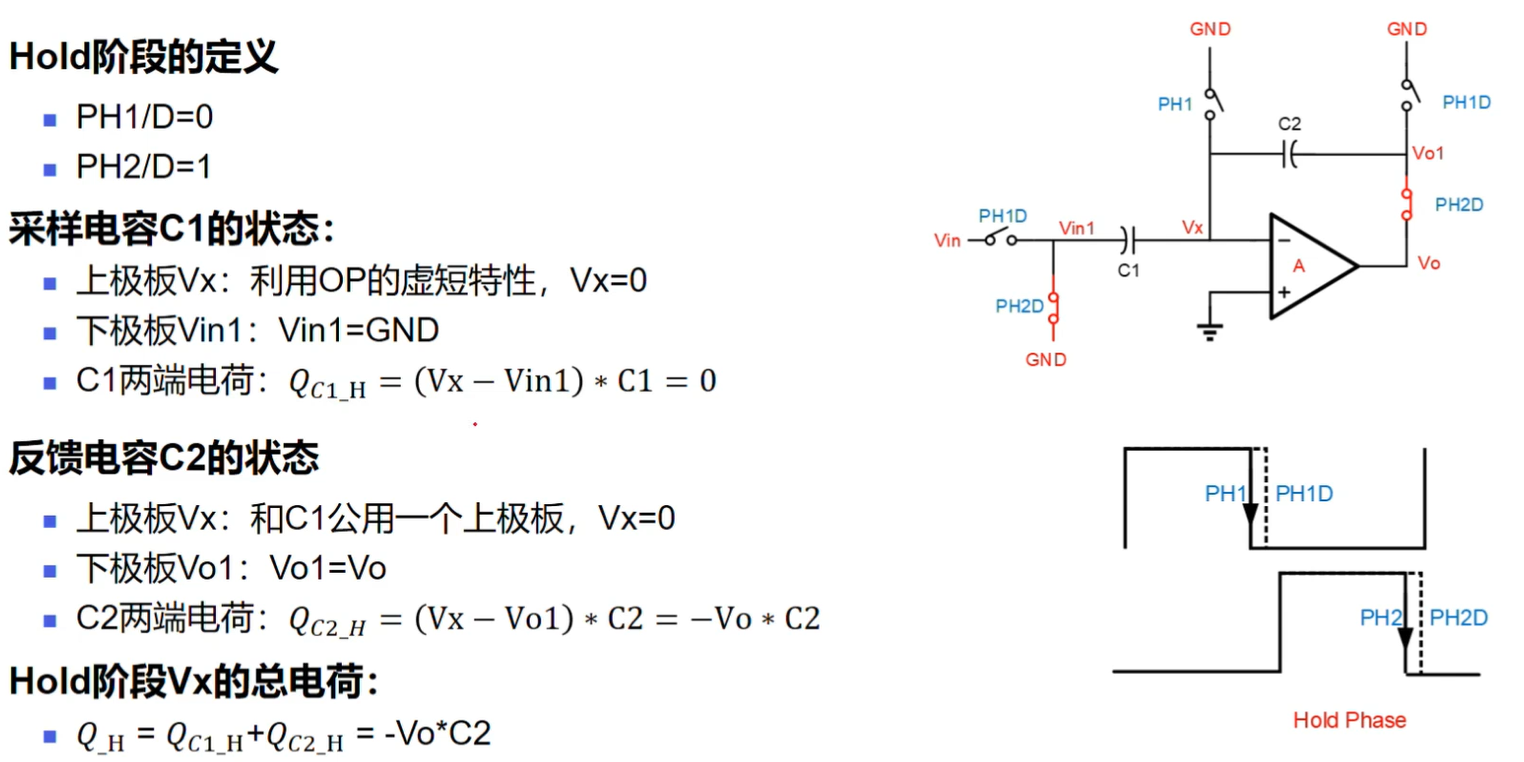

保持阶段

输出