假如系统中存在多个中断,需要合理的配置中断的优先级与中断向量表;在代码生成中,要与中断向量表对应;中断相关的知识参照博客:

DSP28335学习——中断向量表的初始化_中断向量表什么时候初始化-CSDN博客

F28335中断系统及其应用————DSP TMS320F28335 学习笔记 (二)_dsp f28335 中断跳出循环后如何回到循环-CSDN博客

1、dsp28335三级中断机制

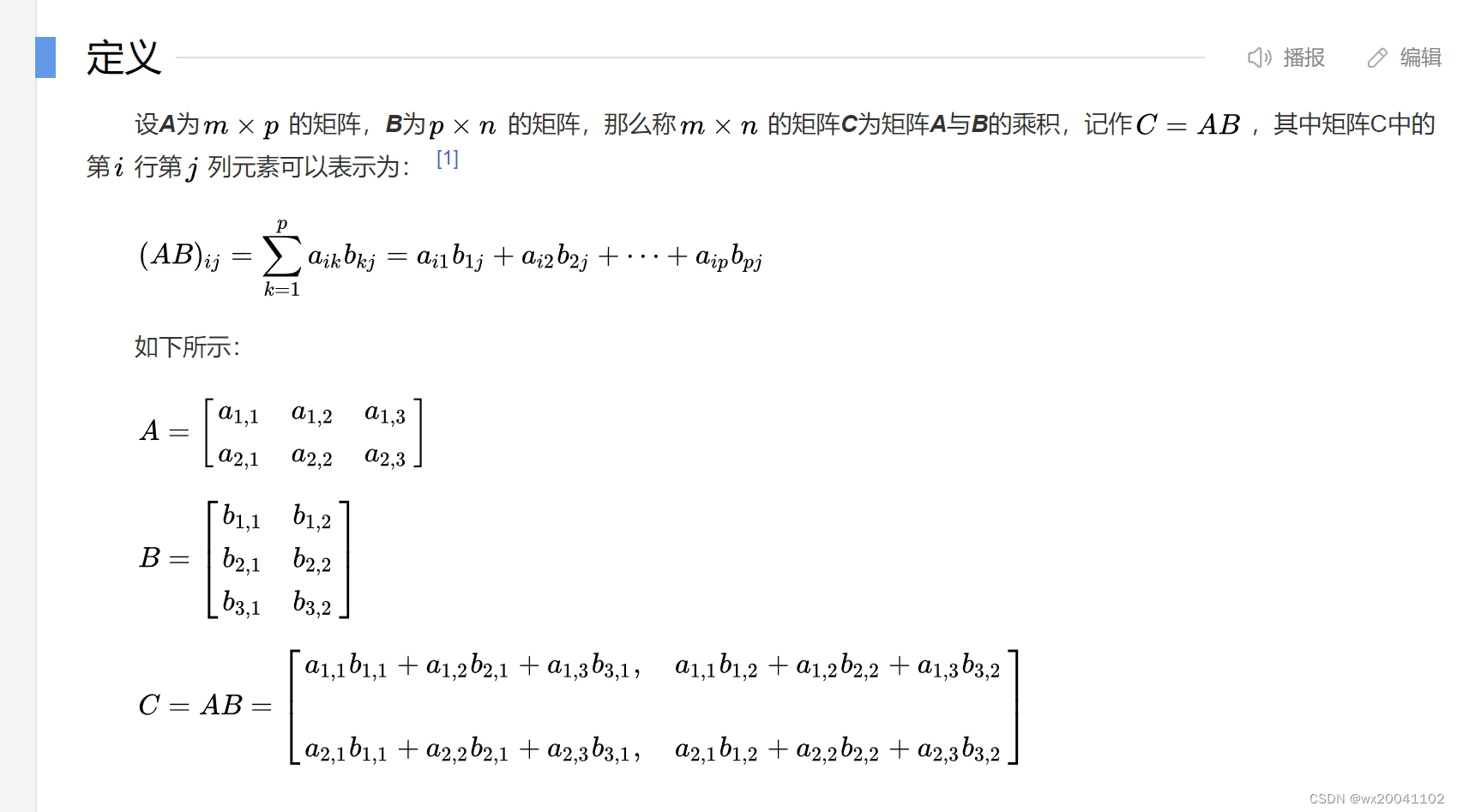

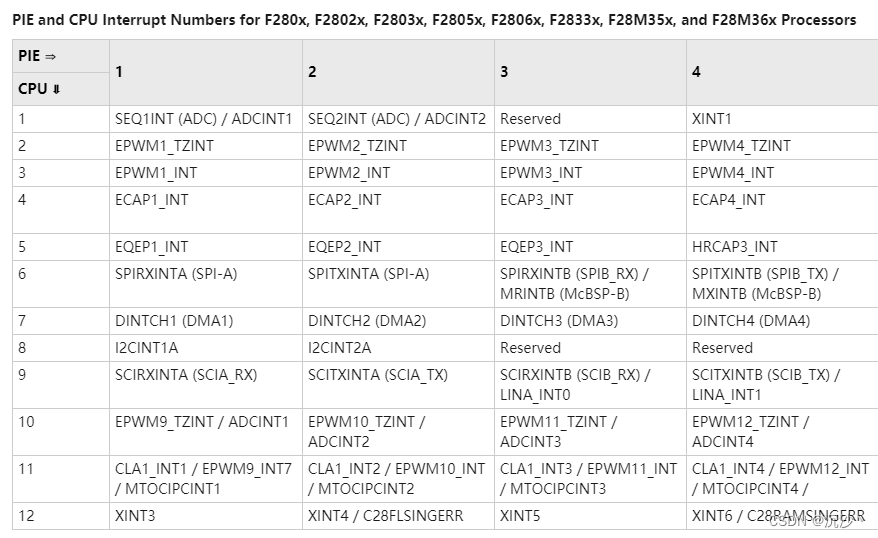

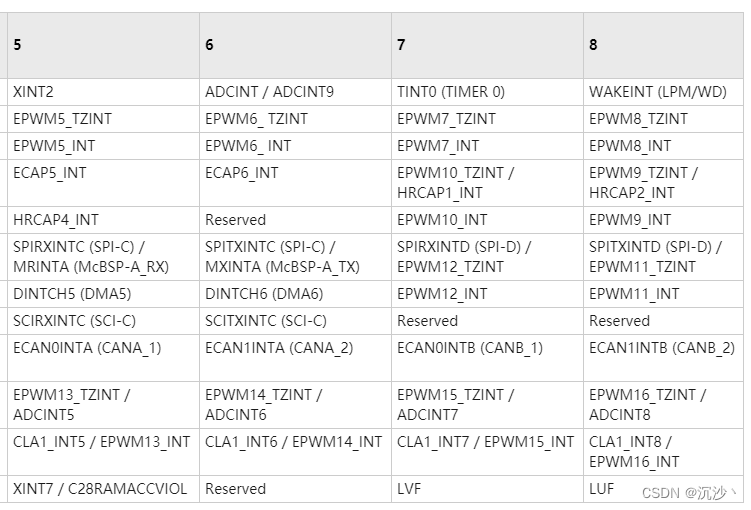

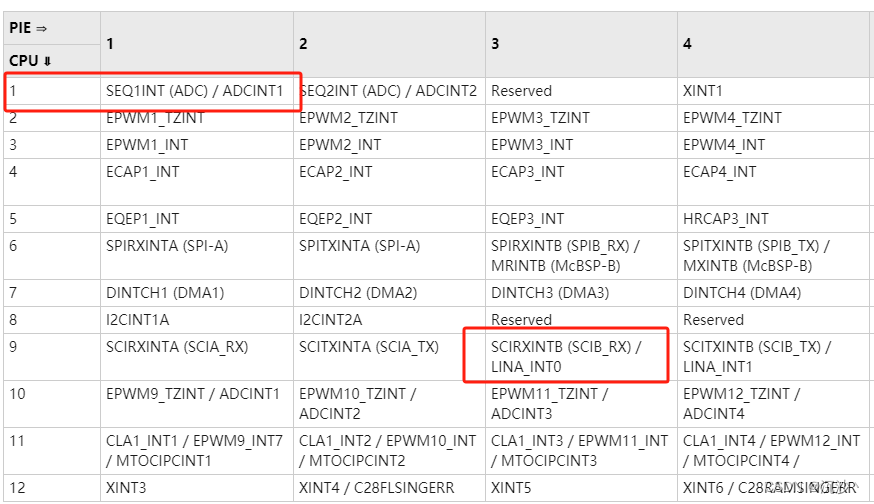

由于外设中断源有58个,而中断线只有12根,这就需要F28335的外设中断扩展模块PIE来进行分配。DSP的外设中断扩展模块结构图如下图所示,F28335的中断采用的3级中断机制,第一级是CPU中断、第二级为PIE级中断、第三级为外设级中断。至于为什么这么设计:由于DSP内部集成了多种外设,每个外设都会产生一个或者多个外设级中断,但是由于CPU中断线有限无法处理所有的外设级中断,因此只能让出12根中断线交给PIE模块进行管理,将所有的外设中断分为了12组,并通过寄存器进行管理。而要实现一次中断响应,通过对下图分析可知,外设级中断要得到CPU的响应需要同时满足两个条件。:1、得到PIE模块的允许(由PIE模块的:PIEIER和PIEIFR寄存器控制分配,由PIEACK控制使能),2、得到CPU的允许(由CPU中断的:IFR和IER寄存器控制分批额,由INTM控制使能)

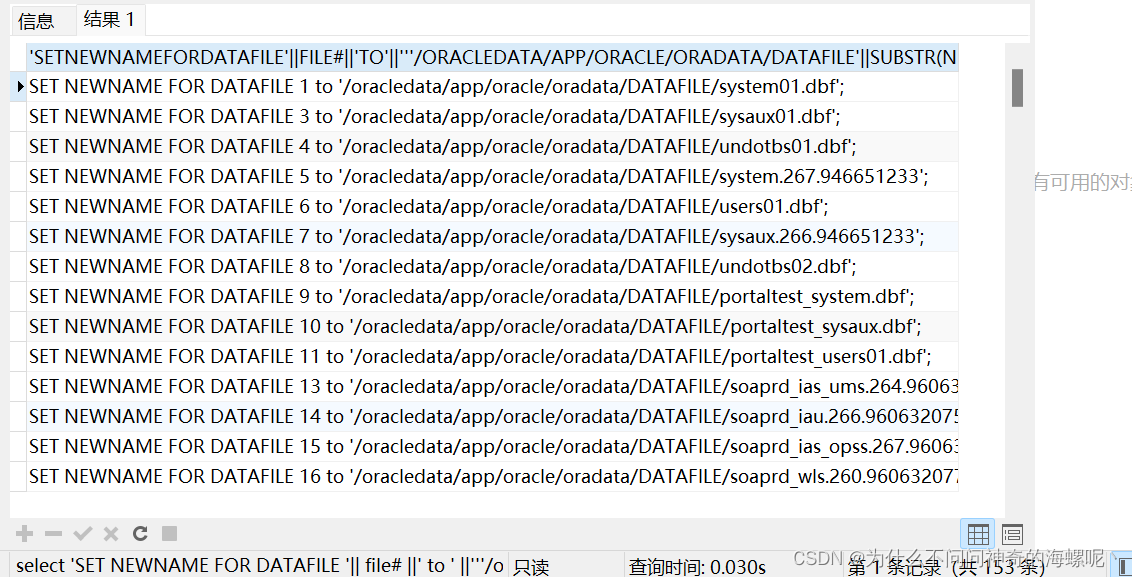

2、中断向量表

前4:

后4:

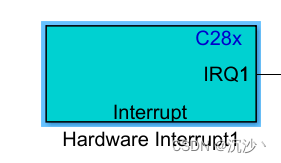

3 、Simulink中的配置

模块截图

模块设置;

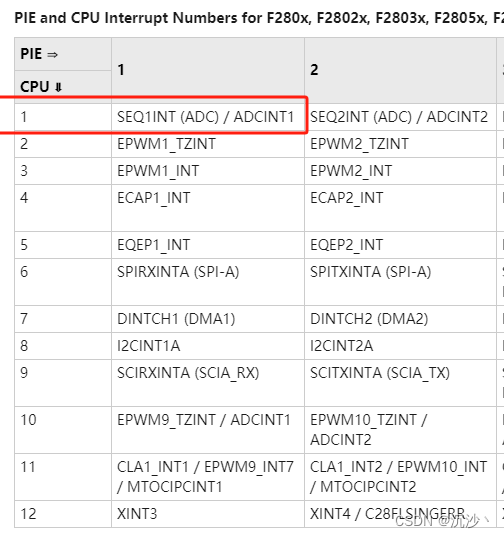

例如常用的ADC中断的配置;ADC中断的PIE级中断号是1,ADC中断的CPU级中断号也是1;因此都设置为1;

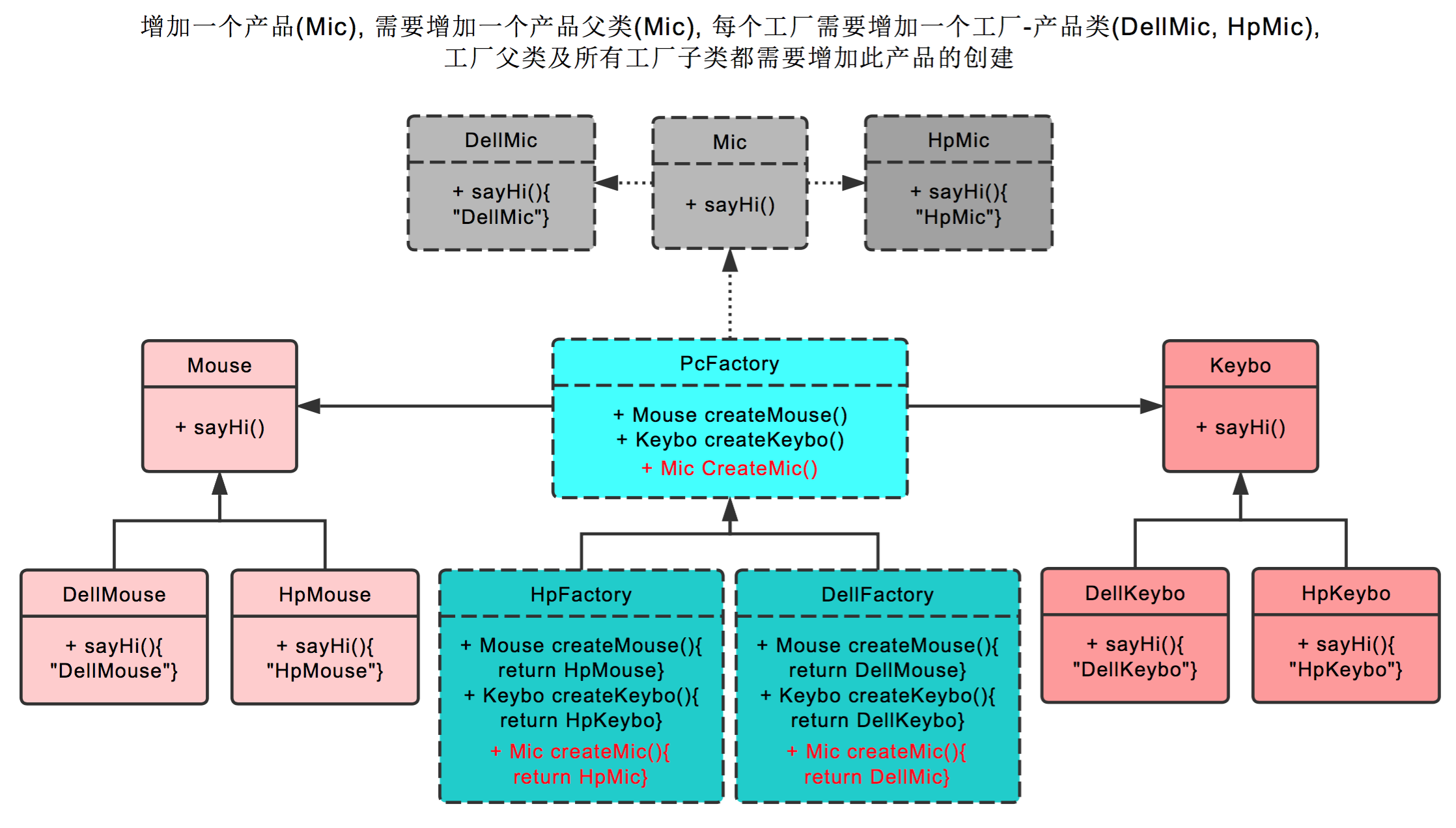

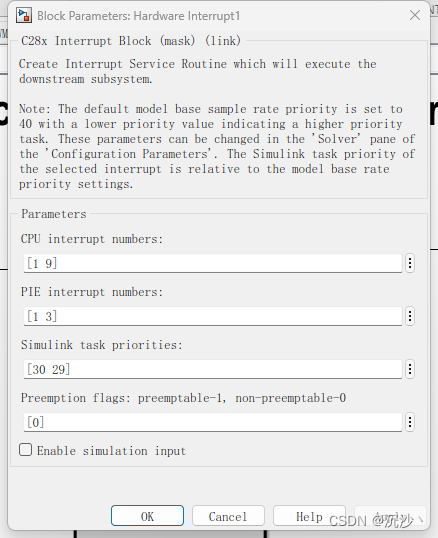

4、Simulink中多级中断的配置

当需要配置多个中断的时候;就需要设置中断向量表,假如我们需要串口接收中断+ADC中断,优先级 ADC > 串口接收中断,配置则如下图所示;

配置如下所示:目前优先级就按照中断向量表来的,CPU的中断优先级是由高到低是INT1~INT12,PIE的中断优先级由高到低是INTx.1~INTx.8。

5、如何验证中断时间?

配置完成后,关键是要验证各级中断的触发是否符合设计;例如执行控制算法的中断周期必须与PWM的载波周期完全一致,假如无法一致,系统将会失控,这个点必须检查;

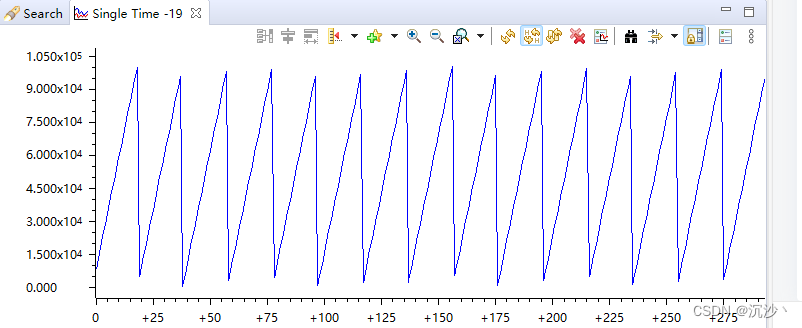

步骤一:算法中加入一个计数器,count = count + 1,加到100000归零;

步骤二:代码生成后,下载至控制板,在expression窗口观测该变量的变化,右键该变量,点击graph,选择实时更新;根据下图测试结果可知,此时中断累加到100000所需要的时间是10s(CCS的grash窗口采样周期设为500ms),中断周期 = 20/100000 = 200us,中断频率为50kHz;

步骤三:若与设计不对应,检查系统时钟、ePWM模块比较值、ADC时钟等;

以下列步骤为例:

(1)检查系统时钟,系统时钟、低速时钟和高速时钟均为150MHz;

(2)检查ADC时钟,ADC时钟为25MHz,为采样模块最大时钟频率;

(3)检查ePWM模块设置和ADC模块设置;

首先是ADC模块选择ePWM作为触发转换源头,并选择Post interrupt at the end of conversion

然后是ePWM模块;

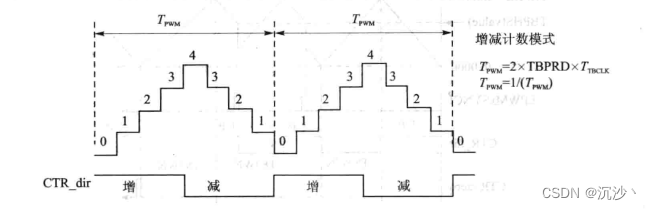

TPRD的值和Counting mode共同决定了载波的周期,在Up-Down模式载波周期 = (2*TPRD)/ePWM时钟 ;而 ePWM时钟 = 系统时钟SYSCLK / (TBCLKDIV * HSPCLKDIV) ,按照当前的设置,PWM周期为 2*7500/150000000 = 100us;

(4)以上均为计算时间,但是实际应用过程中,假如中断算法模块中嵌入了其他的模块,中断时间将受到影响。

例如在中断执行模块中假如和QEP和SCI模块,累加100000所需时间如下图所示,(125-55)*0.5 = 35s。

假如只保存SCI模块,则累加到100000的时间如下图所示;(130-60)*0.5 = 35s,这是不符合设计的。

假如只保存QEP模块,则累加到100000的时间如下图所示;(76-56)*0.5 = 10s,这是符合设计的。

假如不加任何其他模块在中断执行模块中,则累加到100000的时间如下图所示,(78-58)*0.5 = 10s,这是符合设计的。

小结:

1、F28335的中断采用的3级中断机制,第一级是CPU中断、第二级为PIE级中断、第三级为外设级中断。

2、PU的中断优先级是由高到低是INT1~INT12,PIE的中断优先级由高到低是INTx.1~INTx.8。

3、例如执行控制算法的中断周期必须与PWM的载波周期完全一致,假如无法一致,系统将会失控;

4、假如中断算法模块中嵌入了其他的模块,中断时间将受到影响。添加模块后需要验证;