目录

一、中断控制器

中断控制器的作用:

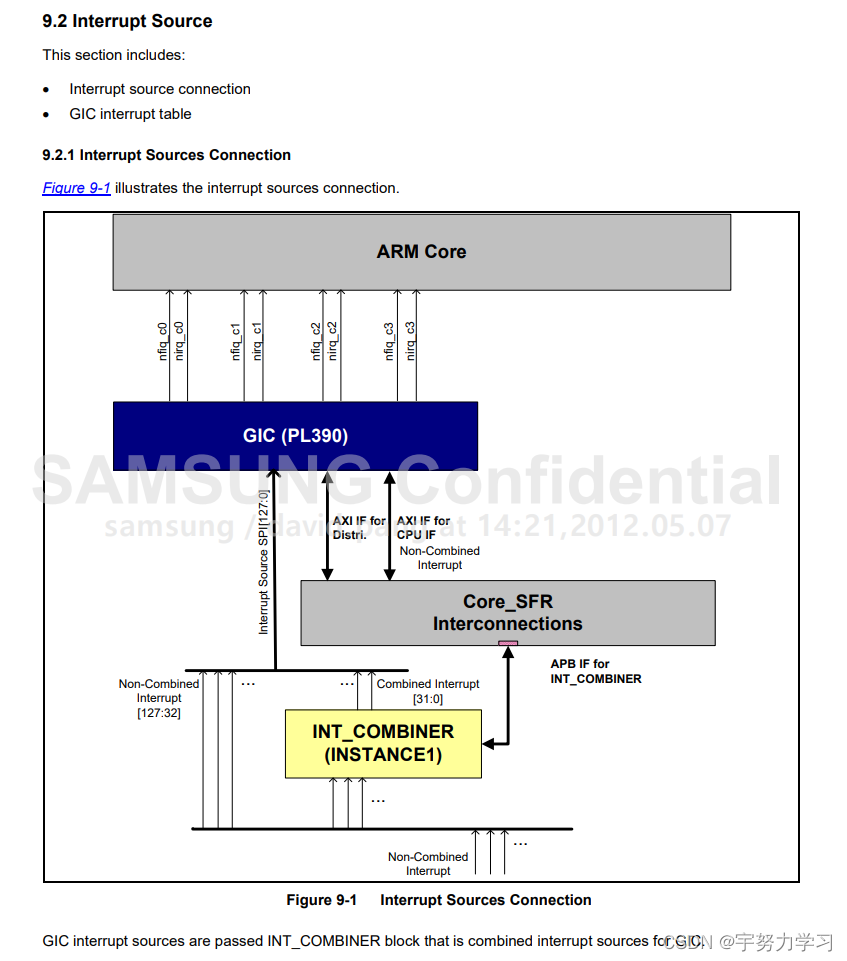

二、Exynos_4412下的中断控制器

它支持三种类型的中断

可以编程设置:

三、中断控制器详解

四、中断控制器编程

一、中断控制器

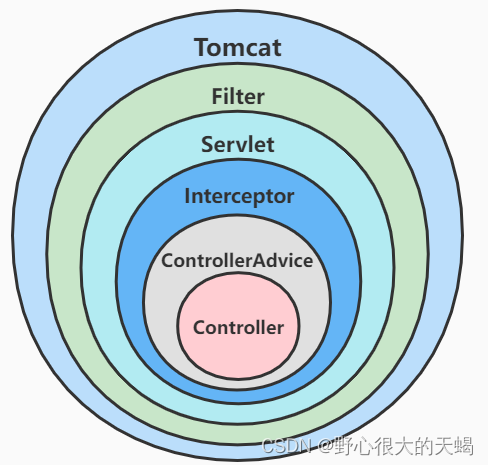

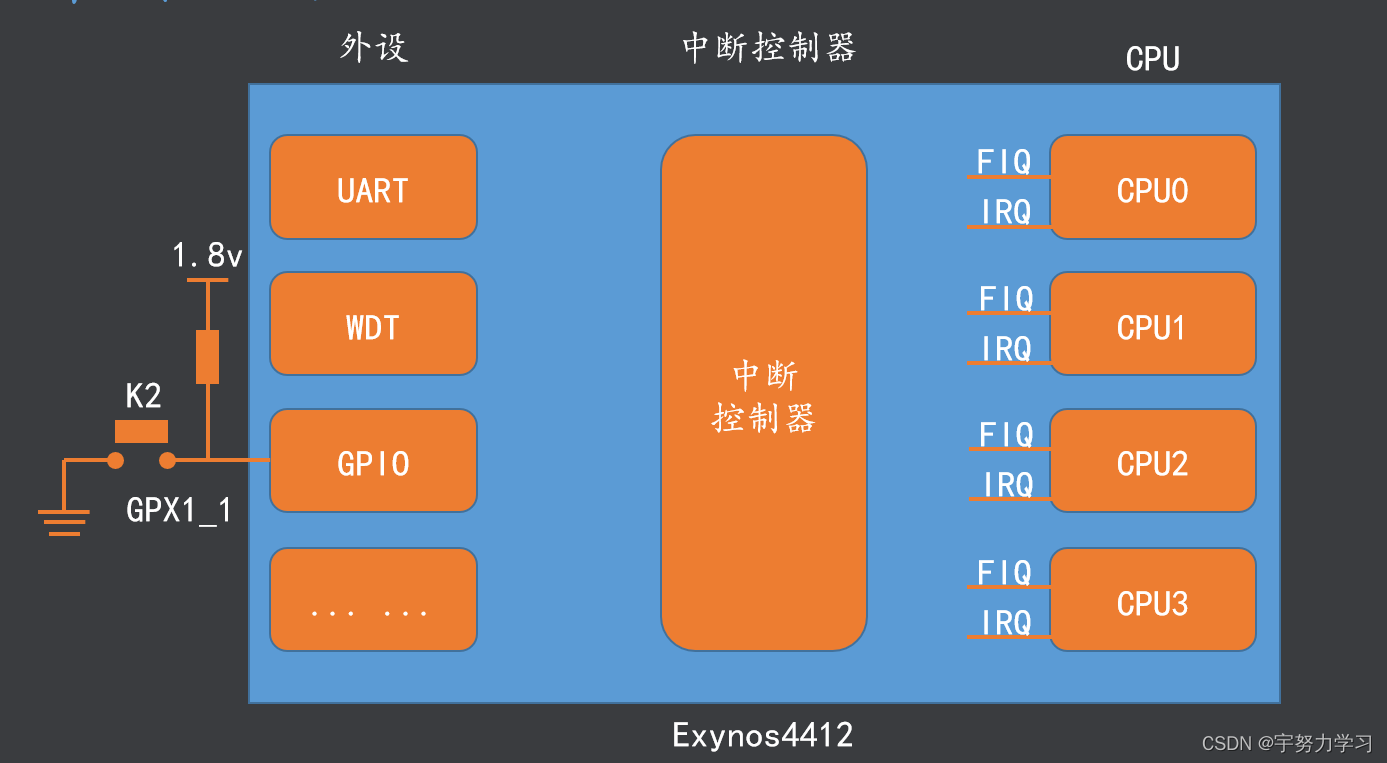

外设产生的中断信号,先要经过中断控制器,中断是异常的一种,如果没有中断控制器,多个外设一起产生中断我们该执行哪一个?在中断处理程序中又收到了中断应该打断吗?

在处理IRQ的时候,会将CPSR写入IRQ_SPSR,然后将CPU切换为IRQ模式,把状态改成ARM状态,把I位写成1禁止全部的IRQ,所以中断这样是我们不想要的。4412是一个四核的CPU,在发送中断前要确定发送给哪个CPU。任何一个外部设备都能触发FIQ和IRQ,只是FIQ速度快一些。还有很多问题,为了解决这些问题,三星公司在设计时就加了一个中断控制器

中断优先级只是决定排队的先后,但是高优先级的不能打断低优先级的中断。

中断控制器的作用:

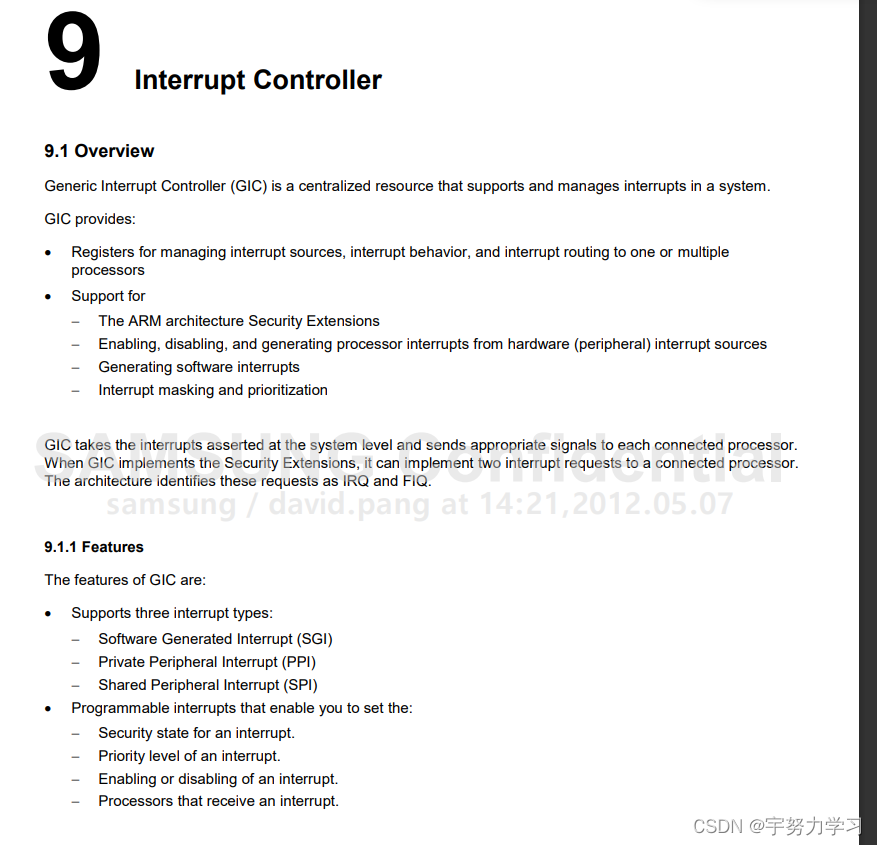

二、Exynos_4412下的中断控制器

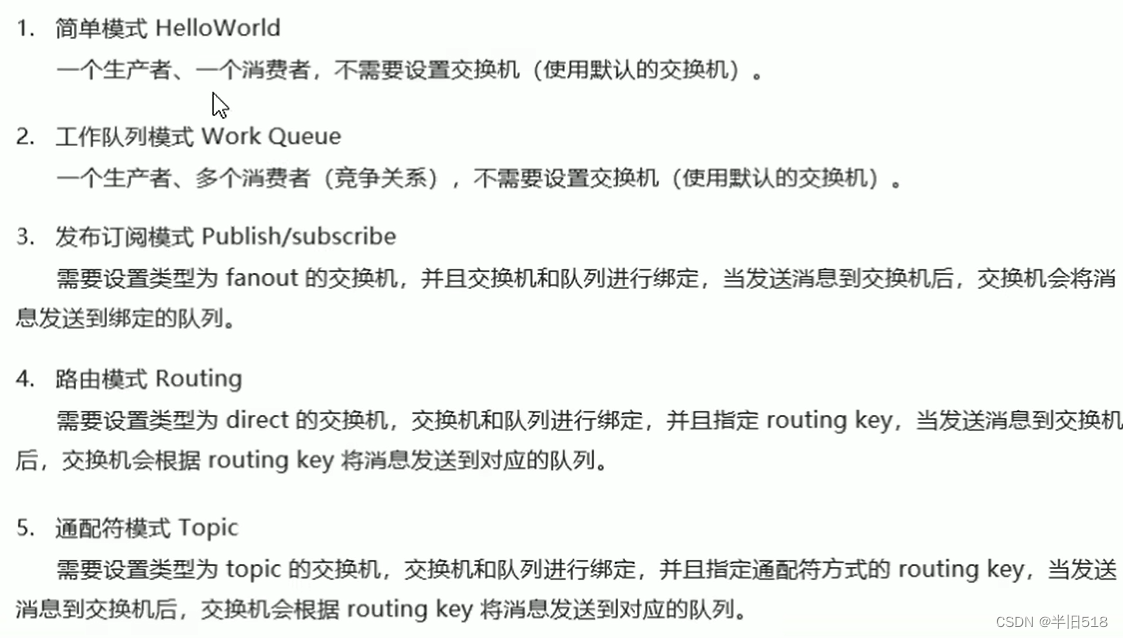

它支持三种类型的中断

SGI:软中断,不是ARM架构里的那个SWI,这个是多核处理器之间用的比较多,一般操作系统内核中会使用。

PPI:私有外设中断

SPI:共享外设中断可以发送给任何一个CPU去执行。

可以编程设置:

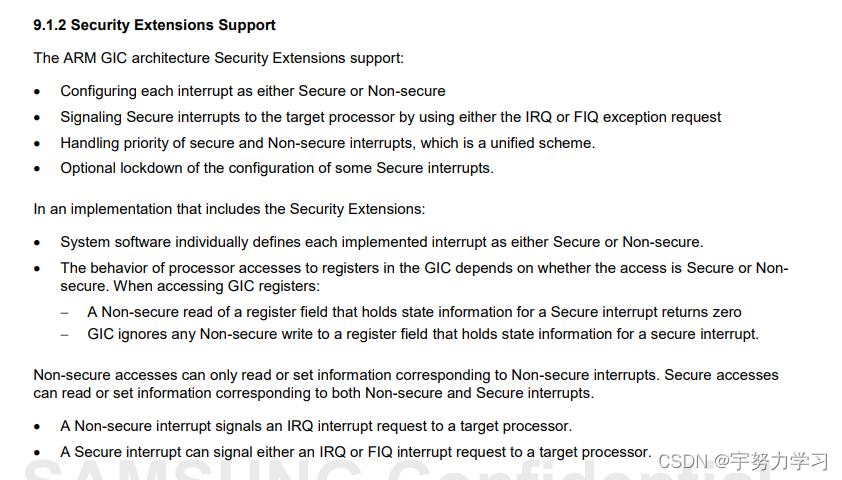

安全模式和非安全模式:安全状态可以触发FIQ和IRQ,非安全状态只可以触发IRQ,咱们一般只使用IRQ

配置中断优先级:

打开或者关闭一些中断:

接收中断的处理器:

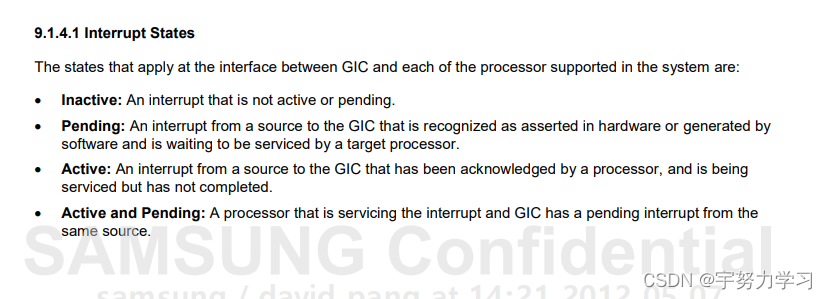

中断状态说明:可以选择这几种状态

中断状态说明:可以选择这几种状态

一共有160个中断信号

中断控制器(GIC)有0-159个中断信号ID,只是起到标识作用没有其它作用

128个SPI 16个PPI 16个SGI

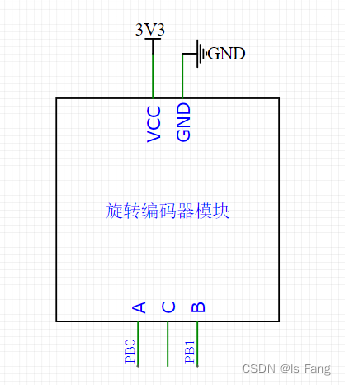

我们这次使用的GPIO中断是EINT[9],也就是外部中断9

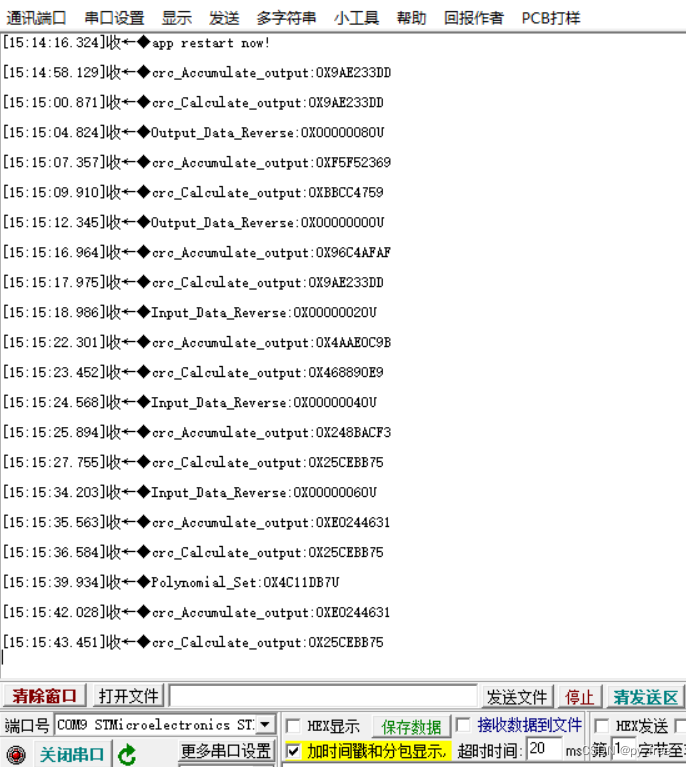

![]()

三、中断控制器详解

真正做开发时这些中断控制器的配置其实是不需要自己写的,ARM-cortex-A9系列的控制器一般都要跑个Linux或者Android操作系统,而这些东西操作系统都为我们写好了,直接调就行。但现在是裸机开发,所以把相关的寄存器找到配置一次

写0忽略全部的外部中断信号,并且不将挂起的中断转发到CPU的接口

写1 监控所有的外部中断,并将挂起的中断转发到CPU的接口

相当于GIC(中断控制器)的总开关。

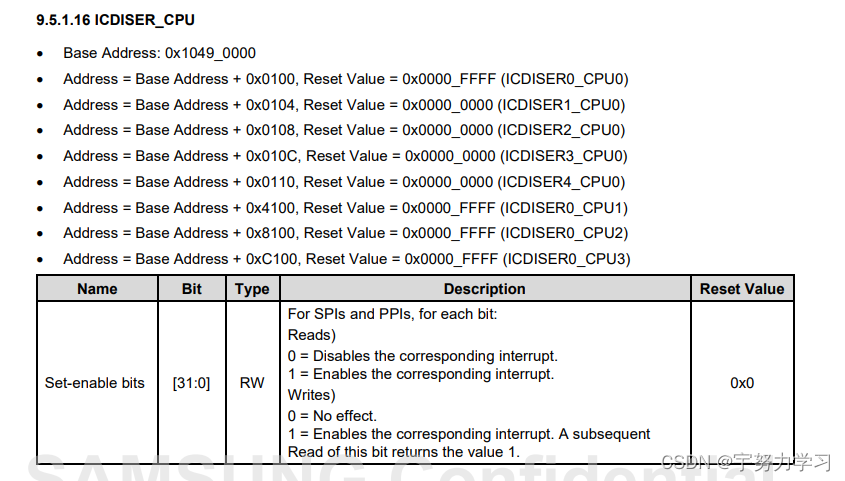

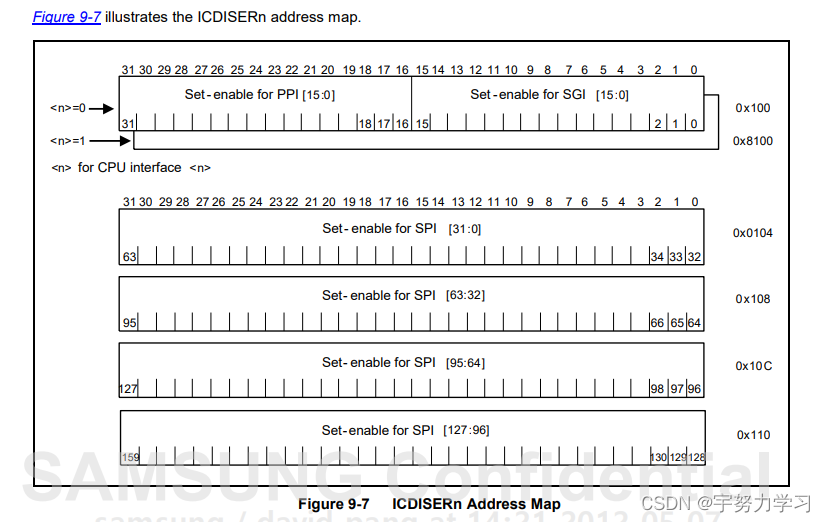

5个32位的寄存器控制这160个中断

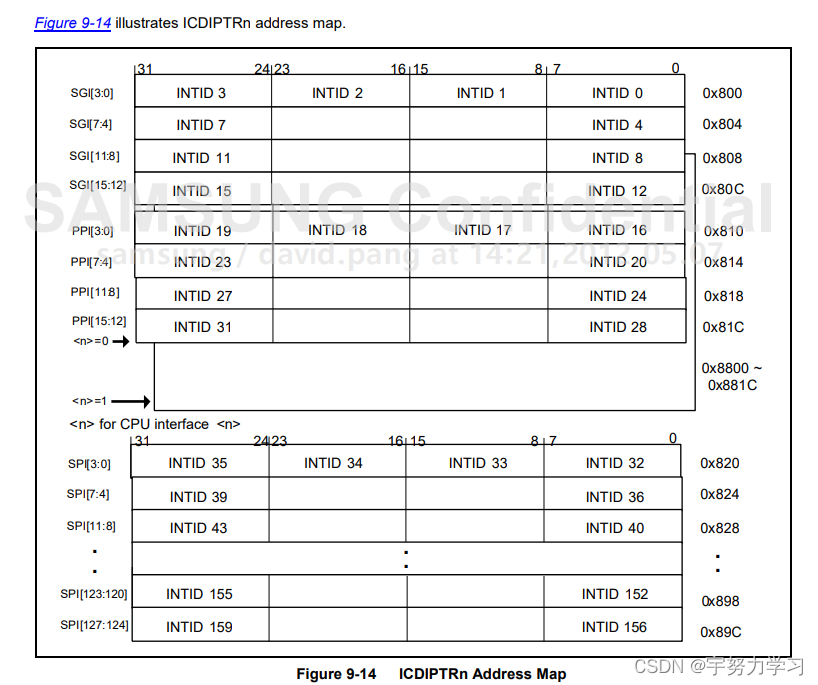

下面这个寄存器用来为每一个中断选择处理他的CPU

4412是一个四核的CPU所以高四位是没有用的。

一共需要40个寄存器来管理这160个中断归属于哪一个CPU处理

正常上电只能使用CPU0,想使用其它的CPU要设置很多CPU相关的寄存器。

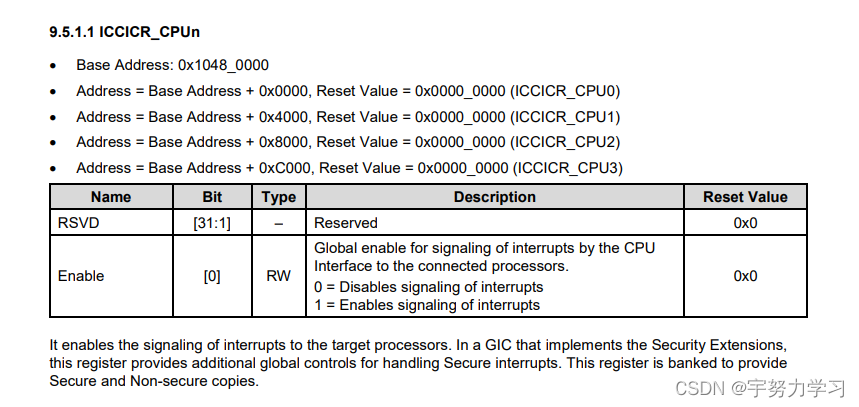

上面是中断控制器和CPU之间的接口,他就像一个开关用哪个就要打开哪个

不设置FIQ和IRQ默认是给IRQ所以我们就不设置了,因为本来就是要做IRQ的实验

然后因为只有一个中断所以也不需要设置中断优先级。

所以我们一共需要设置4个寄存器就可以了

ICDDCR:中断总开关

ICDISER:每个中断的小开关,我们要打开57号中断的开关

ICDIPTR:确定我们的57号中断发送给哪个CPU处理,暂时只能是CPU0

ICCICR:中断控制器和CPU之间的接口

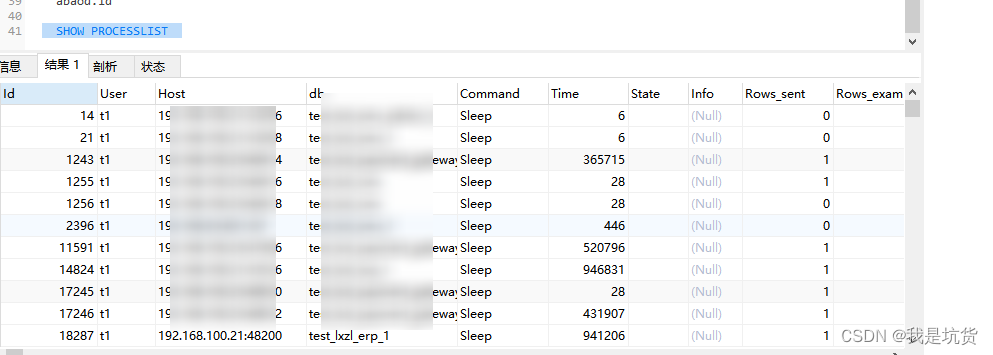

四、中断控制器编程

#include "exynos_4412.h"

int main()

{

GPX1.CON = GPX1.CON | (0xF << 4);

EXT_INT41_CON = EXT_INT41_CON & (~(0x7 << 4)) | (0x2 << 4);

EXT_INT41_MASK = EXT_INT41_MASK & (~(1 << 1));

ICDDCR = ICDDCR | 1;

ICDISER.ICDISER1 = ICDISER.ICDISER1 | (1 << 25);

ICDIPTR.ICDIPTR14 = ICDIPTR.ICDIPTR14 & (~(0xFF << 8)) | (0x01 << 8);

CPU0.ICCICR = CPU0.ICCICR | 1;

return 0;

}