一、FPGA与AD9162的JESD204B接口

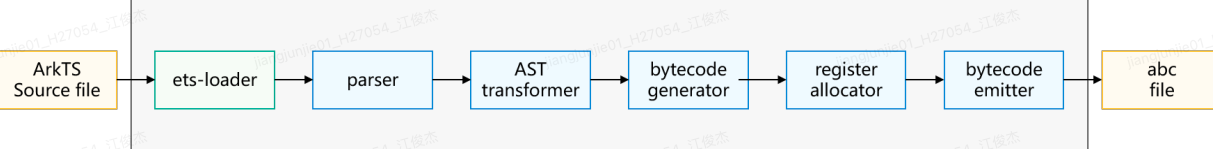

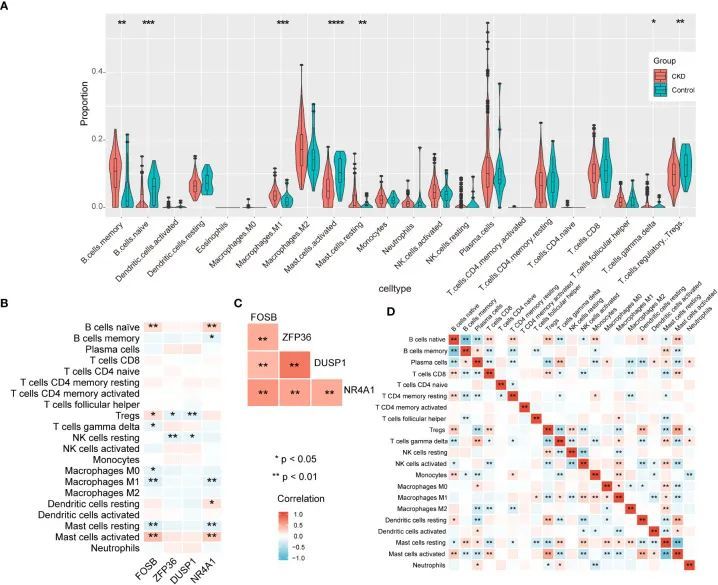

FPGA作为JESD204B接口的发送端,AD9162作为JESD204B接口的接收端。FPGA和AD9162的device clk、SYSREF由同源时钟芯片产生。其中,FPGA和AD9162的divice clk时钟不同,并且FPGA的decive clk等同于JESD204B IP的core clk。如图,为JESD204B接口建立链接的整个过程。

1.相关术语:

L :lane数量。

F:每条lane每帧的字节数。

K:每个多帧的包含的帧数量。

M:(converter)转换器数量。

S:每个转换器每帧的样本数量。

N:转换器分辨率。

NP(N'):每个样本的总bit数。

LaneRate:lane速率。

ByteRate:字节速率。

FrameRate:帧速率。

Multi_FrameRate:多帧速率。

device clk:设备时钟。

SYSREF:确定性延时参考钟。

2.FPGA和AD9162配置:(DAC采样率2.4GHz)

- DAC decode mode:mix mode

- Interpolation mode:1x(bypass)

- L=8,M=1,F=1,S=4,K=32,N=16,NP(N')=16。

- LaneRate=20*FDAC*(M/L)=20*2.4G*(1/8)=6Gbps.

- ByteRate = LaneRate/10=600M

- FrameRate = ByteRate/F=ByteRate/1=600M

- Multi_FrameRate=FrameRate /K=FrameRate /32=18.75M

- FPAG device clk = FPGA core clk = FPGA GTX reference clk = Lane Rate/40=150M。

- SYSREF时钟周期为Multi_FrameRate时钟周期的整倍数分频,做5倍分频。SYSREF =Multi_FrameRate/5=3.75M。

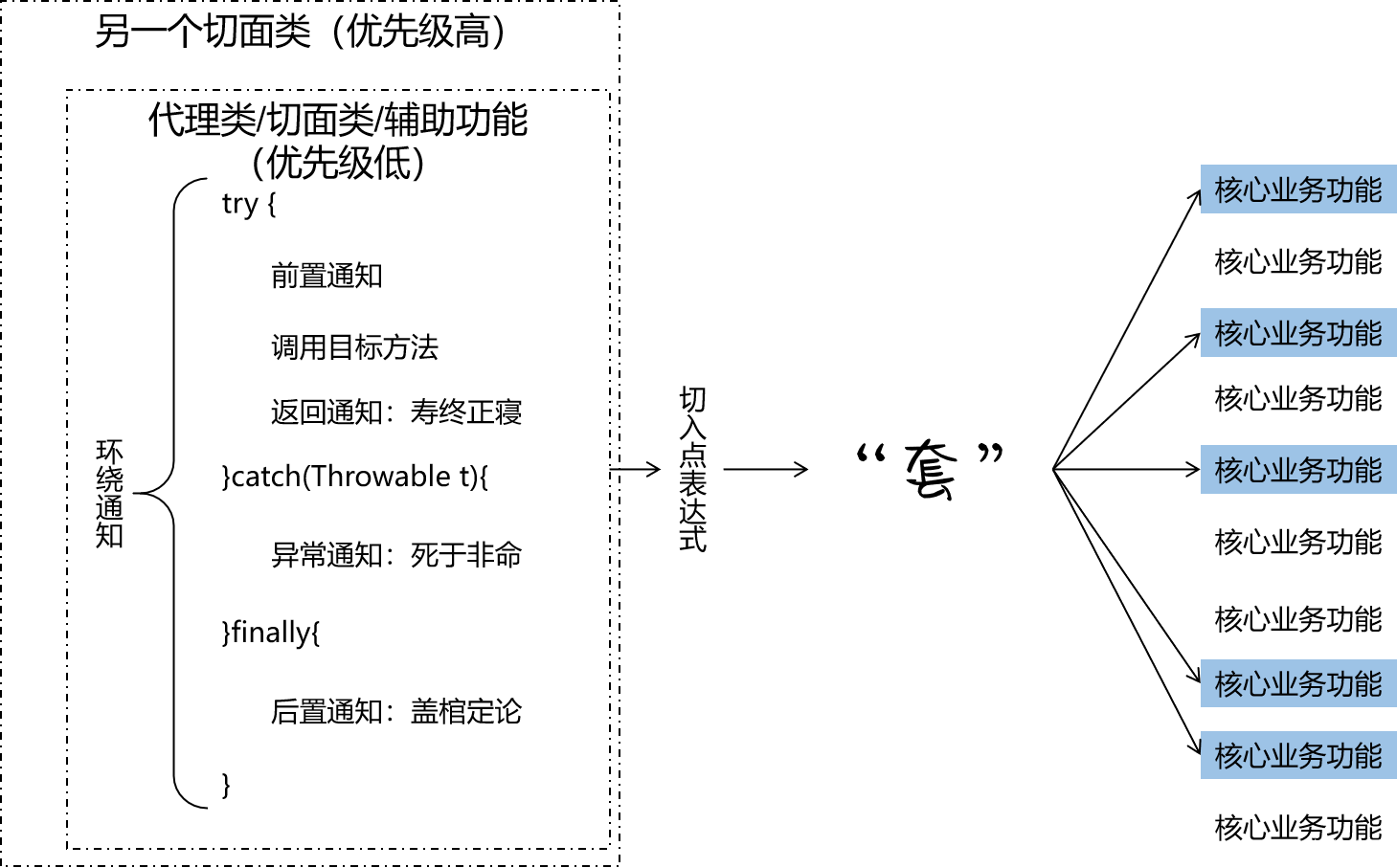

3.JESD204B建立过程

3.1 FPGA和AD9162接收到同源的SYSREF和device clk。

FPGA在接收到SYSREF和device clk后,开始发送K28.5(BC)码值。

3.2 JESD204B建立链接的第一个阶段:码值识别。

AD9162捕捉SYSREF的上升沿,开始识别FPGA发送的连续4个K28.5(BC)码值,识别正确后,完成第一个阶段,将SYNC信号在本地多帧时钟(Local Multi Frame Clock,简称LMFC)边沿拉高,发送至FPGA,进入第二阶段——初始化链路序列对齐。

3.3 JESD204B建立链接的第二个阶段:初始化链路序列对齐(Inital Lane Alignment Sequence,简称ILAS)。

ILAS由四个或更多的多帧组成,每个多帧的最后一个字符是多帧对齐字符/ A/(K.28.3)(7C)。第一、第三和第四个多帧用预定的数据值填充。第二个多帧包含/R/ (K.28.0)(1C), /Q/ (K.28.4)(9C),然后是链接参数对应的数据。在这个过程中,AD9162会缓存多帧,详细后写(有时间再写)在最后一个ILAS的最后一个/A/字符之后,进入第三个阶段——数据流(也就是用户数据阶段)。

3.4 JESD204B建立链接的第三个阶段:数据流阶段。

在这个阶段,如果用户不在JESD204B接口上发送数据,空闲状态下,每条lane会发送FC00+7C00码值。存在有效数据时,注意有效数据在每条lane上的排列顺序,发送数据即可。

附录:8b10b码表。