主页: 元存储博客

文章目录

- 前言

- 1. bit 类型

- 2. reg 类型

- 3 wire类型

- 4 integer类型

- 5 real类型

- 6 parameter类型

- 7 enum类型

- 8 array 类型

- 9 向量类型

- 10 time 类型

- 11 string 类型

前言

在 Verilog 中,有几种不同的数据类型可以用于声明和操作变量。

在 Verilog 中,主要有四种数据类型:

bit类型:bit 是最基本的数据类型,它只能取 0 或 1 两个值,用于表示一个二进制位。

reg类型:reg 类型可用于表示任意宽度的二进制数据,用于描述寄存器的值。reg 类型可以用于存储整数或逻辑值。

wire类型:wire 类型用于描述信号线。它可以表示连接不同模块之间的输出和输入信号。

integer类型:integer 类型用于表示整数,可以存储带符号或无符号的整数值。

除了上述基本数据类型,Verilog 还提供了其他一些高级数据类型:

real类型:real 类型用于表示浮点数,可以存储单精度浮点数值。

parameter类型:parameter 类型用于定义常量值,可以在整个设计中使用。

enum类型:enum 类型用于定义枚举类型,可以为一个变量定义一组可能的值。

array类型:array 类型用于定义数组,可以存储多个相同类型的值。

在 Verilog 中,还可以使用内置的运算符和函数来操作这些数据类型,以实现逻辑运算、位运算和算术运算等功能。

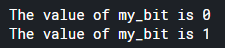

1. bit 类型

Verilog中的bit类型是一种1位宽的数据类型,用于表示二进制位。它只能取0或1的值。

在Verilog中,可以使用bit类型来声明和操作单个二进制位。以下是一个使用bit类型的示例:

module example;

reg bit my_bit;

initial begin

my_bit = 0;

$display("The value of my_bit is %b", my_bit);

#10;

my_bit = 1;

$display("The value of my_bit is %b", my_bit);

end

endmodule

在上面的示例中,我们声明了一个名为my_bit的bit类型寄存器。初始值为0。然后,在仿真开始后的10个时间单位后,我们将my_bit的值更改为1,并将其打印出来。

实际应用中,bit类型可用于表示状态标志、控制信号等。

实践

定义bit类型变量:

bit enable; // 定义一个bit类型的变量enable

定义bit类型信号:

reg [7:0] data; // 定义一个8位的寄存器类型信号data

wire [3:0] address; // 定义一个4位的线网类型信号address

定义bit类型端口:

module myModule (

input bit clk,

input bit [7:0] data_in,

output reg bit [7:0] data_out

);

...

endmodule

clk是一个输入端口,data_in是一个8位的输入端口,data_out是一个8位的输出端口,它们都是bit类型。

对bit类型进行操作:

assign a = b & c; // 按位与运算

assign d = ~e; // 按位取反运算

assign f = g ^ h; // 按位异或运算

这些操作可以对bit类型的变量、信号和端口进行按位运算。

需要注意的是,在Verilog中,bit类型的取值只能是0或1,不能是其他值。

2. reg 类型

reg类型用于存储一个或多个位的值,可以表示整数、浮点数、布尔值以及其他数据类型。

reg类型在模块的顶层声明中使用,类似于变量的声明。

reg类型可以在模块的内部或always块中使用,并可以通过赋值语句对其进行读写操作。

reg类型的值可以通过使用=或<=赋值运算符进行赋值。

reg类型的值可以在条件语句中使用,例如if语句或case语句。

reg类型的信号可以用于表示时钟信号、输入/输出端口、中间结果等。

以下是一个使用reg类型的简单示例:

module reg_example(input clk, input reset, input data, output reg output_data);

always @(posedge clk or posedge reset) begin

if (reset)

output_data <= 0;

else if (data)

output_data <= 1;

end

endmodule

output_data是一个reg类型的输出端口。它根据时钟信号clk和复位信号reset的上升沿进行更新。如果reset为高电平,则将output_data置为0;如果data为高电平,则将output_data置为1。

实践

声明和初始化reg变量:

reg [7:0] data; // 声明一个8位的寄存器变量

reg reg_init = 1'b1; // 声明并初始化一个1位的寄存器变量

reg [3:0] reg_array [0:9]; // 声明一个大小为10的1维寄存器数组

在always块中使用reg:

reg [7:0] counter;

always @(posedge clk) begin

if (reset) begin

counter <= 8'd0;

else begin

counter <= counter + 1;

end

end

在模块中使用reg:

module my_module (

input wire clk,

input wire reset,

output reg [7:0] data

);

always @(posedge clk) begin

if (reset) begin

data <= 8'd0;

else begin

data <= data + 1;

end

end

endmodule

在测试台中使用reg:

module my_module_tb;

reg clk;

reg reset;

wire [7:0] data;

my_module_tb dut (

.clk(clk),

.reset(reset),

.data(data)

);

always begin

#5 clk = ~clk;

end

initial begin

clk = 0;

reset = 1;

#10 reset = 0;

#100 $finish;

end

endmodule

这段代码是一个测试模块,用于测试一个名为my_module的模块。

首先定义了三个信号:clk、reset和data。

然后使用my_module模块实例化了一个名为dut的实例,并将clk、reset和data连接到该实例的对应端口。

接下来使用always模块定义了一个时钟信号clk的行为。每隔5个时间单位,clk的值会取反。

接着使用initial模块初始化了clk和reset的值。将reset设置为1,然后在10个时间单位后将reset设置为0。最后在100个时间单位后结束仿真。

代码的作用是模拟一个时钟信号clk,并在时钟上升沿时将reset信号从1变为0,然后仿真结束。

Verilog的reg类型是用来定义寄存器的,可以在时钟上升沿到来时更新其值。

module reg_practice (

input wire clk, // 时钟信号

input wire reset, // 复位信号

output reg out // 输出信号

);

reg [7:0] counter; // 8位寄存器

always @(posedge clk or posedge reset) begin

if (reset) begin

counter <= 8'b0; // 复位时将寄存器值设置为0

end else begin

counter <= counter + 1; // 非复位状态下,每个时钟周期将寄存器值加1

end

end

always @(posedge clk) begin

if (counter >= 8'b100) begin

out <= 1'b1; // 当寄存器值达到100时,将输出信号设置为1

end else begin

out <= 1'b0; // 否则将输出信号设置为0

end

end

endmodule

代码中,定义了一个8位寄存器 counter 和一个输出信号 out。在时钟的上升沿到来时,根据复位信号的状态,更新寄存器的值。

通过两个always块,分别对复位和时钟上升沿进行操作。在复位状态下,将寄存器的值设置为0。在非复位状态下,每个时钟周期将寄存器的值加1。

另外,在第二个always块中,通过判断寄存器的值是否大于等于100来控制输出信号 out 的值。如果寄存器的值大于等于100,则将输出信号设置为1,否则设置为0。

3 wire类型

wire 是一种数据类型,用于表示信号或线路的连接。

wire 可以用于连接不同模块之间的信号,并传递数据。它类似于电子电路中的导线,可以用来连接不同的逻辑门或寄存器。在 Verilog 中,wire 可以在 module 的输入和输出端口中定义,也可以在 module 的内部用于连接模块内的不同信号。

wire 的声明通常在 module 的头部,例如:

module my_module(input wire a, input wire b, output wire c);

endmodule

在上述的例子中,wire a 和 b 是 my_module 的输入端口,wire c 是输出端口。它们分别用于连接其他模块输入和输出。

wire 类型的信号在 module 内部可以进行复制、连接和驱动。例如,可以使用 assign 语句将一个 wire 连接到另一个 wire,或者将一个 wire 直接连接到一个逻辑表达式的输出。例如:

wire d; wire e; assign d = a & b; assign e = d | c;

在上面的例子中,wire d 的值等于 a 和 b 的逻辑与操作的结果,wire e 的值等于 d 和 c 的逻辑或操作的结果。

wire 类型的信号在 module 内部可以驱动(赋值),也可以参与模块之间的连接,但不能显示地被赋值。也就是说,只能通过连接其他信号的方式来改变 wire 的值。

在Verilog中,wire变量的赋值是通过连续赋值(continuous assignment)语句完成的。连续赋值语句使用“assign”关键字,将一个或多个表达式与wire变量相连。

module ExampleModule (

input wire a,

input wire b,

output wire sum

);

assign sum = a + b;

endmodule

例子中,定义了一个名为ExampleModule的模块,具有两个输入端口(a和b)和一个输出端口(sum)。在模块内部,使用了连续赋值语句将输入端口的值相加,并将结果赋给输出端口。

需要注意的是,wire变量在Verilog中默认是无符号(unsigned)类型。如果希望使用有符号(signed)类型的信号传输,可以使用signed关键字来声明wire变量。

除了在模块中使用wire变量外,它还可以在模块之间连接,实现模块的互联。通过将模块的输出端口和另一个模块的输入端口连接起来,可以实现信号的传递。

以下是一个使用wire变量连接模块的例子:

module Adder (

input wire a,

input wire b,

output wire sum

);

assign sum = a + b;

endmodule

module TopModule;

wire a, b;

wire sum;

Adder adder_inst (

.a(a),

.b(b),

.sum(sum)

);

endmodule

例子中,定义了一个名为Adder的模块,实现了两个输入相加的功能。在TopModule中,声明了三个wire变量(a、b和sum),然后将它们连接到Adder模块的输入和输出端口。

通过这种方式,当对a和b进行赋值时,Adder模块会自动计算并将结果传递给sum变量。

4 integer类型

integer是一种预定义的有符号整数数据类型。它的取值范围为-231到231-1,即-2147483648到2147483647。integer类型通常用于表示整数数据,例如计数器、地址等。在Verilog中,可以使用integer类型来声明和操作整数变量。

module example;

integer a, b, c;

initial begin

a = 10;

b = 20;

c = a + b;

$display("The sum of %0d and %0d is %0d", a, b, c);

$finish;

end

endmodule

例子中,我们声明了三个整数变量a、b和c,并使用赋值语句将a和b分别赋值为10和20。然后,我们使用加法运算符将a和b相加,并将结果存储在变量c中。最后,我们使用$display函数打印出a、b和c的值。

需要注意的是,integer类型在Verilog中是有符号的,默认是带符号扩展的。如果要使用无符号整数,可以使用reg类型或使用unsigned修饰符来声明变量。

示例

定义一个整数变量:

integer myInt;

这将创建一个名为myInt的整数变量。

定义一个整数信号

reg [7:0] mySignal;

这将创建一个名为mySignal的8位整数信号。可以使用reg类型来定义整数信号。

初始化整数变量:

integer myInt = 10;

创建一个值为10的整数变量myInt。

使用整数变量进行计算:

integer a = 5;

integer b = 3;

integer sum;

always @* begin

sum = a + b;

end

创建两个整数变量a和b,并将它们相加的结果存储在sum变量中

使用整数信号进行逻辑运算

reg [7:0] a = 4;

reg [7:0] b = 2;

wire [7:0] result;

assign result = a & b;

这将创建两个8位整数信号a和b,并通过逻辑AND运算符将它们的结果存储在result信号中。

5 real类型

real类型是一种浮点数类型,用于表示有小数的数字。它具有32位的精度,可以表示大约7位有效数字。real类型可以用于执行浮点运算,例如加法、减法、乘法和除法。

module test;

real a, b, c;

initial begin

a = 3.14;

b = 2.5;

c = a + b;

$display("c = %0f", c);

c = a - b;

$display("c = %0f", c);

c = a * b;

$display("c = %0f", c);

c = a / b;

$display("c = %0f", c);

end

endmodule

输出结果:

c = 5.64

c = 0.64

c = 7.85

c = 1.256

6 parameter类型

参数(parameter)是一种用于指定常量值的数据类型。参数可以用来定义模块的大小、地址范围、延迟等常量值。

Verilog中有三种参数类型:

parameter:这是最常用的参数类型,用于定义常量值。参数值在编译时确定,并且在整个设计中保持不变。

module my_module #(parameter WIDTH = 8);

// ...

endmodule

WIDTH是一个参数,它的默认值为8。在实例化my_module时可以通过修改参数值来改变模块的行为。

localparam:这是一种局部参数类型,它只在模块内部可见。localparam与parameter类似,但其值只在模块内部使用,对外部不可见。

module my_module;

localparam MAX_VALUE = 100;

// ...

endmodule

MAX_VALUE是一个局部参数,它的值只在my_module内部使用。

defparam:这是用于修改模块实例参数值的关键字。defparam可以在实例化之后,通过修改参数值来改变模块的行为。

module my_module #(parameter WIDTH = 8);

// ...

endmodule

// 修改参数值

defparam my_module.WIDTH = 16;

通过defparam关键字,可以修改已实例化的my_module的WIDTH参数值为16。

7 enum类型

有两种方式定义 enum 类型:

使用 parameter 和 typedef 关键字:

parameter RED = 0;

parameter GREEN = 1;

parameter BLUE = 2;

typedef enum logic [1:0] {RED, GREEN, BLUE} color_t;

代码定义了三个枚举值 RED、GREEN 和 BLUE,并且定义了一个名为 color_t 的 enum 类型,它是一个 2 位逻辑向量。

使用新的 Verilog-2005 标准引入的 enum 类型关键字:

enum color {RED, GREEN, BLUE};

代码定义了一个名为 color 的 enum 类型,其中包含了 RED、GREEN 和 BLUE 三个枚举值。

无论使用哪种方式定义 enum 类型,它们都可以用来声明变量、函数参数或函数返回值的类型:

color_t color_var;

color my_color;

上述代码分别声明了一个名为 color_var 的变量,它的类型是 color_t,以及一个名为 my_color 的变量,它的类型是 color。

8 array 类型

在Verilog中,数组可以是一维或多维的。一维数组是最简单的形式,它由一个索引范围和一组元素组成。例如,下面是一个包含4个元素的一维数组的定义:

reg [7:0] my_array [3:0];

这个数组的索引范围是3到0,也就是说,数组的索引范围是3、2、1、0。每个元素的大小是8位,因为它们是使用reg数据类型定义的。

可以使用索引来访问数组中的元素。例如,以下代码将my_array数组中索引为2的元素赋值为8’b01100010:

my_array[2] = 8'b01100010;

多维数组类似于一维数组,只是它们有多个索引范围。例如,以下是一个定义了2行3列的二维数组的示例:

reg [7:0] my_array [1:0] [2:0];

这个二维数组有两个索引范围:第一个范围是1到0,表示行;第二个范围是2到0,表示列。因此,这个数组可以表示为一个2x3的矩阵。可以使用两个索引来访问数组中的元素。

对于一维数组和多维数组,可以使用for循环来遍历数组中的元素。例如,以下代码将遍历一维数组,并输出每个元素的值

for (i = 0; i <= 3; i = i + 1) begin

$display("my_array[%d] = %b", i, my_array[i]);

end

在Verilog中使用数组可以简化代码的编写,并提高代码的可读性和可维护性。数组可以用于存储大量的数据,并可以通过索引进行访问和处理。

9 向量类型

当位宽大于 1 时,wire 或 reg 即可声明为向量的形式。

reg [3:0] counter ; //声明4bit位宽的寄存器counter

wire [32-1:0] gpio_data; //声明32bit位宽的线型变量gpio_data

wire [8:2] addr ; //声明7bit位宽的线型变量addr,位宽范围为8:2

reg [0:31] data ; //声明32bit位宽的寄存器变量data, 最高有效位为0

对于上面的向量,我们可以指定某一位或若干相邻位,作为其他逻辑使用。例如:

wire [9:0] data_low = data[0:9] ;

addr_temp[3:2] = addr[8:7] + 1'b1 ;

Verilog 支持可变的向量域选择,例如:

reg [31:0] data1 ;

reg [7:0] byte1 [3:0];

integer j ;

always@* begin

for (j=0; j<=3;j=j+1) begin

byte1[j] = data1[(j+1)*8-1 : j*8];

//把data1[7:0]…data1[31:24]依次赋值给byte1[0][7:0]…byte[3][7:0]

end

end

Verillog 还支持指定 bit 位后固定位宽的向量域选择访问。

[bit+: width] : 从起始 bit 位开始递增,位宽为 width。

[bit-: width] : 从起始 bit 位开始递减,位宽为 width。

//下面 2 种赋值是等效的

A = data1[31-: 8] ;

A = data1[31:24] ;

//下面 2 种赋值是等效的

B = data1[0+ : 8] ;

B = data1[0:7] ;

对信号重新进行组合成新的向量时,需要借助大括号。例如:

wire [31:0] temp1, temp2 ;

assign temp1 = {byte1[0][7:0], data1[31:8]}; //数据拼接

assign temp2 = {32{1'b0}}; //赋值32位的数值0

Verilog中的向量类型用于表示多位的数字信号,可以是有符号的或无符号的。向量类型可以用于表示寄存器、端口、线网等。

module vector_example (

input [7:0] input_vector,

output [3:0] output_vector

);

reg [7:0] temp_vector;

always @(posedge clk) begin

temp_vector <= input_vector;

output_vector <= temp_vector[4:1];

end

endmodule

有一个8位的输入向量input_vector和一个4位的输出向量output_vector。temp_vector是一个8位的寄存器。

在always块中,我们使用临时变量temp_vector存储输入向量的值,并将temp_vector的4位到1位赋值给输出向量output_vector。

这个例子展示了如何使用向量类型进行信号处理和数据传输。与标量变量类似,向量类型也支持位选择、切片、连接等操作。

Verilog中的向量类型还可以进行算术运算、逻辑运算、位移等操作,更多操作可以参考Verilog语言手册。

需要注意的是,向量类型的位宽必须在声明时指定,并且在代码中使用时需要指定位选择范围。如果没有指定范围,默认为全范围。

10 time 类型

time类型用来表示时间的数值。它是一种整数类型,其单位被定义为纳秒。

time类型的取值范围是从0到2^64-1,大约相当于584年。在模拟过程中,time类型的数值会随着仿真时间的推进而自动增加。

time类型可以用于表示信号的延迟,任务和函数的执行时间等。在Verilog中,使用#符号来表示时间延迟,例如#10表示延迟10个时间单位。

time类型的变量可以使用time关键字进行声明,例如:

time delay;

time类型的变量可以进行数学运算,比较运算和逻辑运算。此外,还可以使用$time系统函数获取当前仿真时间的数值。

module test;

time delay;

initial begin

$display("Simulation time start: %0t", $time);

delay = 10;

if (delay > 5) begin

$display("Delay is greater than 5");

end

#delay;

$display("Simulation time end: %0t", $time);

end

endmodule

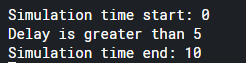

我们声明了一个time类型的变量delay,并将其设置为10。然后,我们使用一个if语句判断delay是否大于5,并在条件满足时打印一条消息。接着,我们使用#delay进行延迟,然后使用$display函数打印当前仿真时间的数值。

运行结果

程序开始时, 我们获取了一次仿真起始时间是0 ns, 执行一次 delay (10) 后,仿真时间变成了 10 ns.

11 string 类型

在 Verilog 中,没有直接支持字符串数据类型。但是,我们可以使用 char 或者 byte 数组来表示字符串。

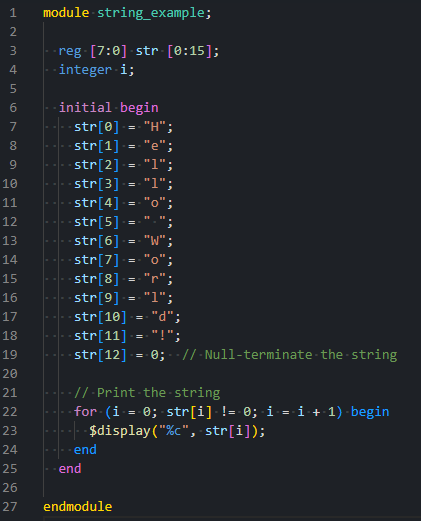

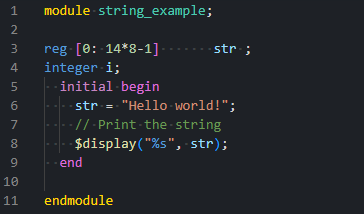

一个简单的实例是,将一个字符串存储在一个 char 数组中,并通过循环将其打印出来

我们定义了一个大小为 16 的 char 数组 str 来存储字符串。我们将字符串 “Hello World!” 存储在这个数组中,并在循环中逐字符打印出来。循环会一直执行直到遇到 null 字符 (ASCII 码值为 0)。

请注意,在 Verilog 中,字符串是以 ASCII 字符的形式存储的,所以我们可以直接使用 ASCII 字符表示字符串中的字符。

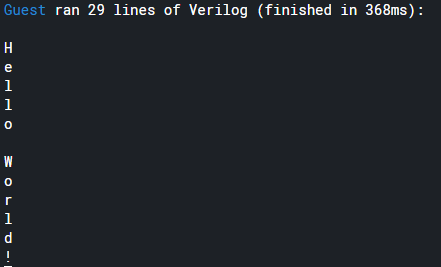

或者换个方式更简约

效果是一样

参考文献

声明

本文仅为学习交流目的。

文中部分文字和图片来源于互联网,列在参考的文献,但可能有遗漏。如有侵权,请告知我删除。