一、目的

上一篇中《HPM6750系列--第九篇 GPIO详解(基本操作)》我们讲解了HPM6750 GPIO相关内容,再进一步讲解其他外设功能之前,我们有必要先讲解一下时钟系统。

时钟可以说是微控制器系统中的心脏,外设必须依赖时钟才能正常工作。

二、介绍

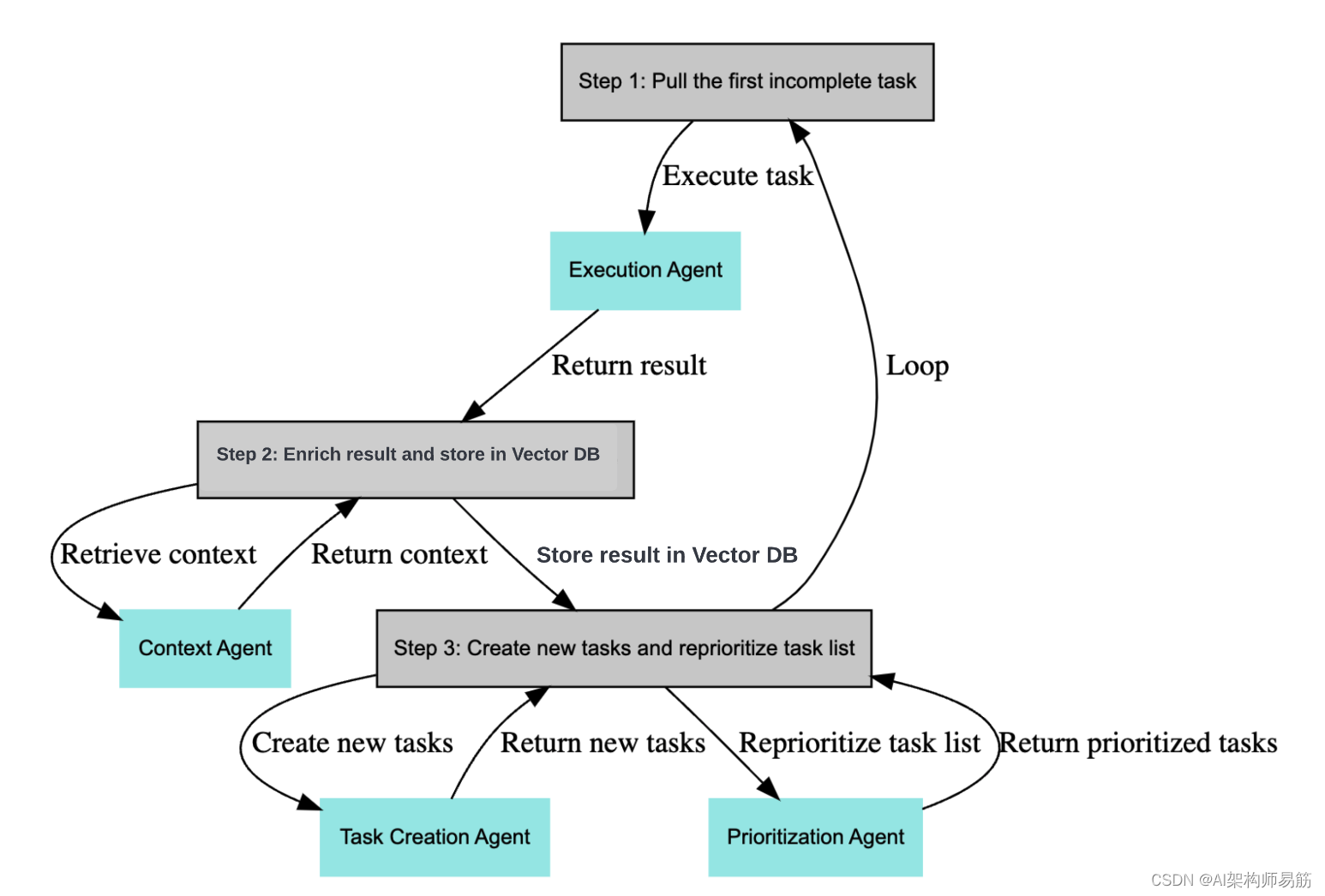

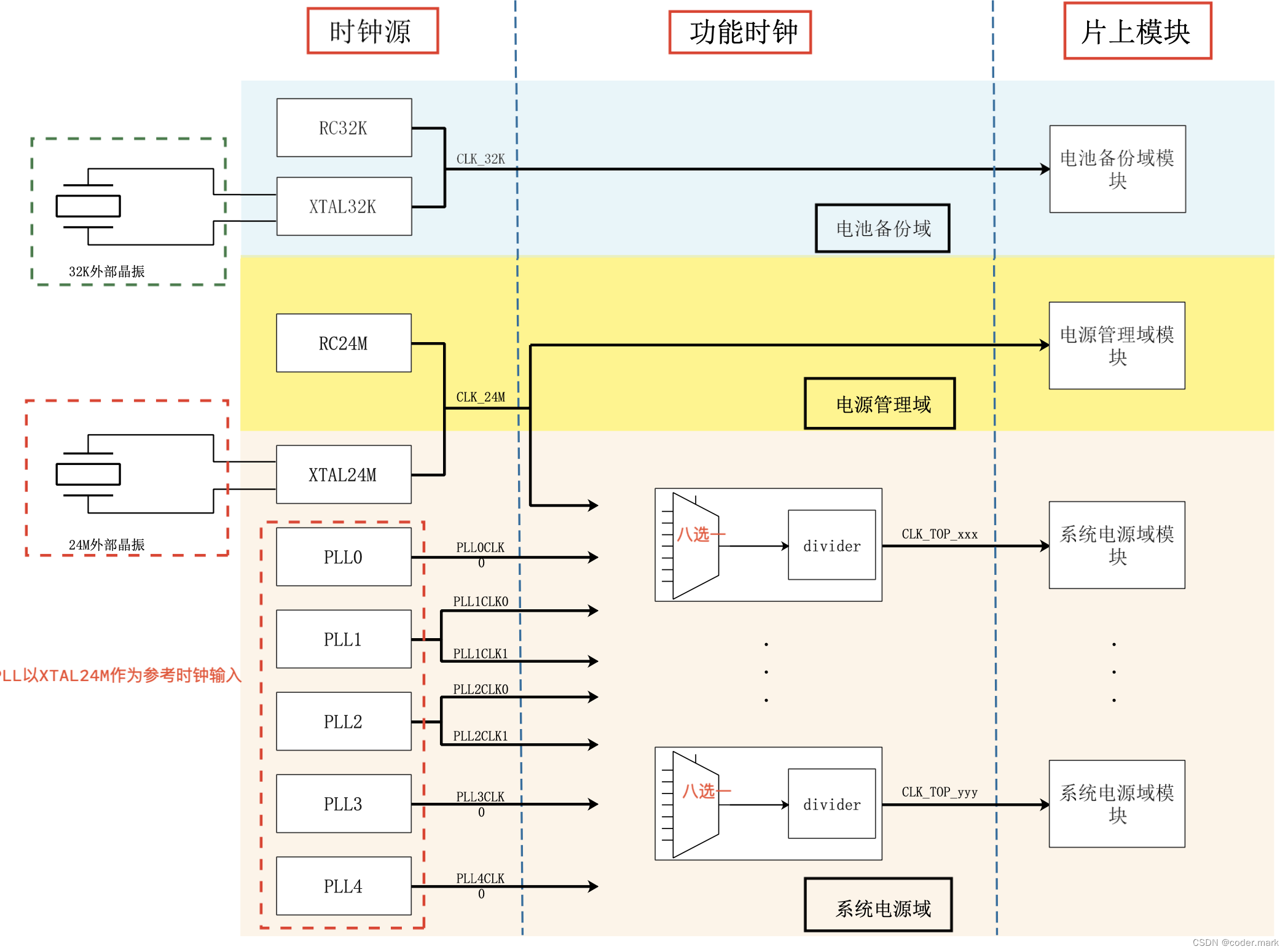

首先我们先看一下整个系统的时钟框图。

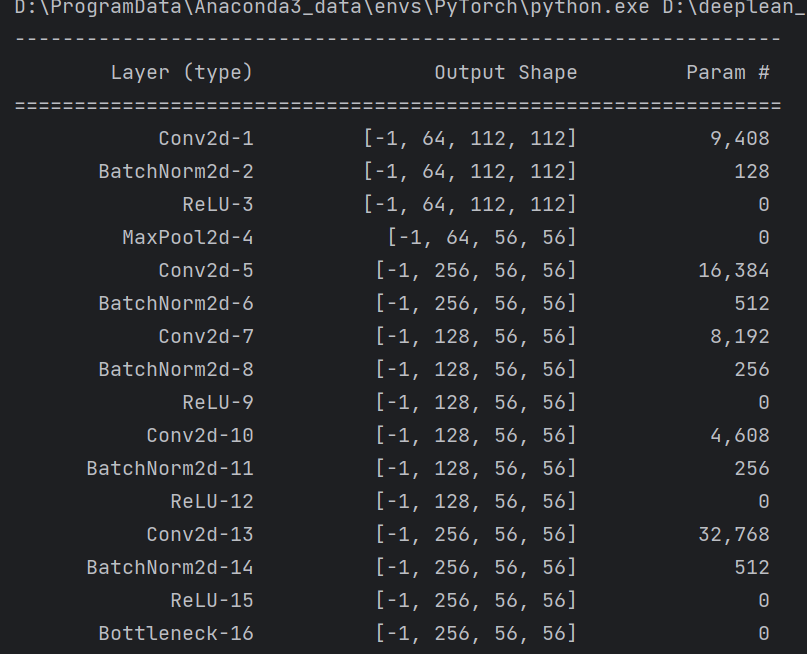

1.时钟系统

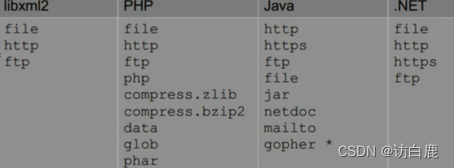

整个时钟系统由三部分组成,分别为外部时钟输入、时钟源和功能时钟组成,系统中不同电源域的片上模块使用不同的功能时钟,有些偏上模块也会直接使用外部时钟。

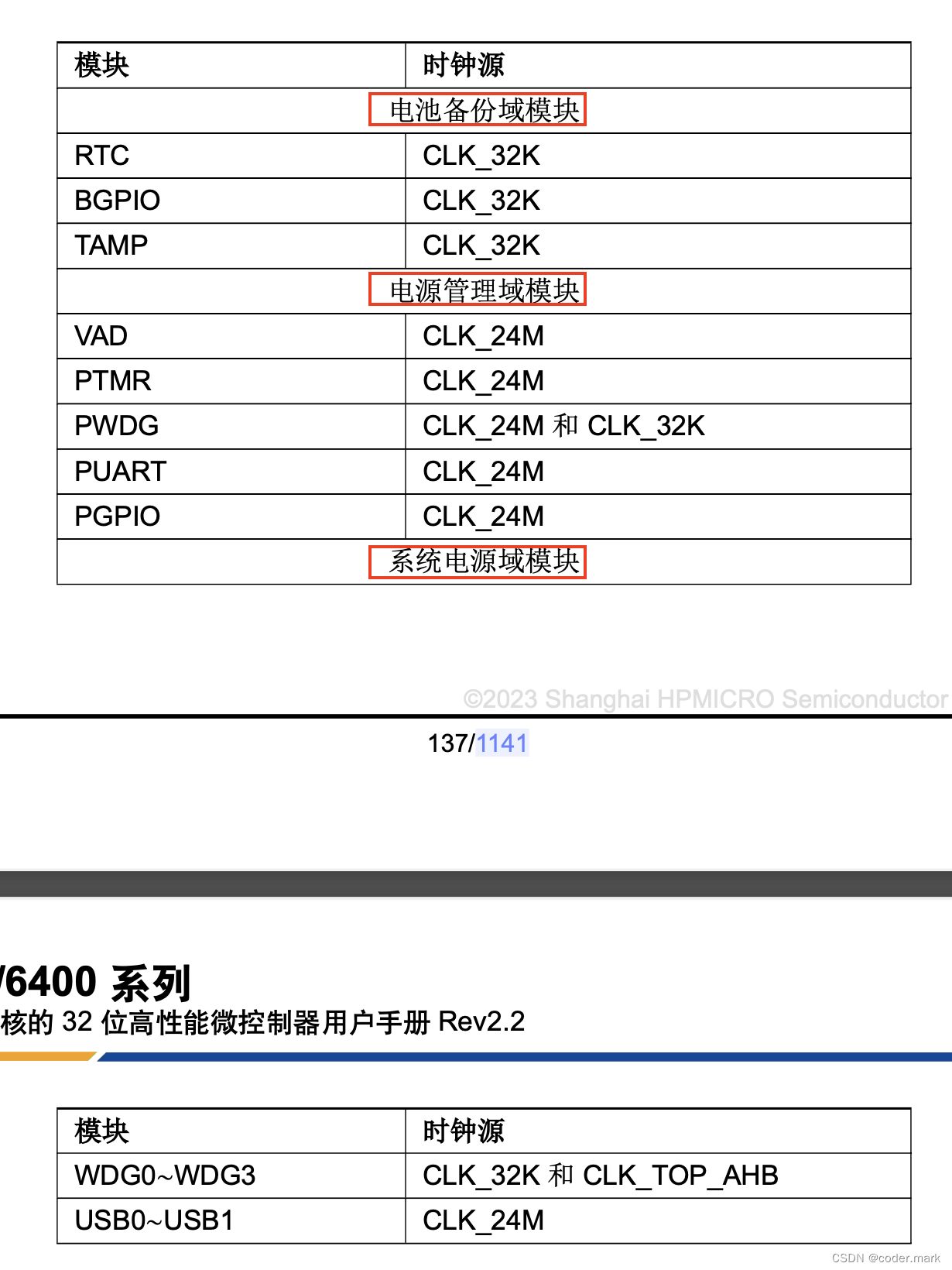

如上图说明,电池备份域使用CLK32K时钟源,XTAL32K 和 RC32K 共同构成 CLK_32K 时钟源。当 XTAL32K 频率稳定时,CLK_32K 来自 XTAL32K 的输 出时钟。当 XTAL32K 尚未稳定或没有外接 32K 晶振时,CLK_32K 来自 RC32K 的输出时钟。两个时钟之间的切 换自动进行。

电源管理域使用CLK_24M时钟源,XTAL24M 和 RC24M 共同构成 CLK_24M 时钟源。当 XTAL24M 使能并频率稳定时,CLK_24M 来自 XTAL24M 的输出时钟,当 XTAL24M 关闭或尚未稳定时,CLK_24M 来自 RC24M 的输出时钟。两个时钟之间的切换自动进 行。

系统电源域使用有五组PLL作为时钟源,PLL自身使用XTAL24M作为参考时钟输入。

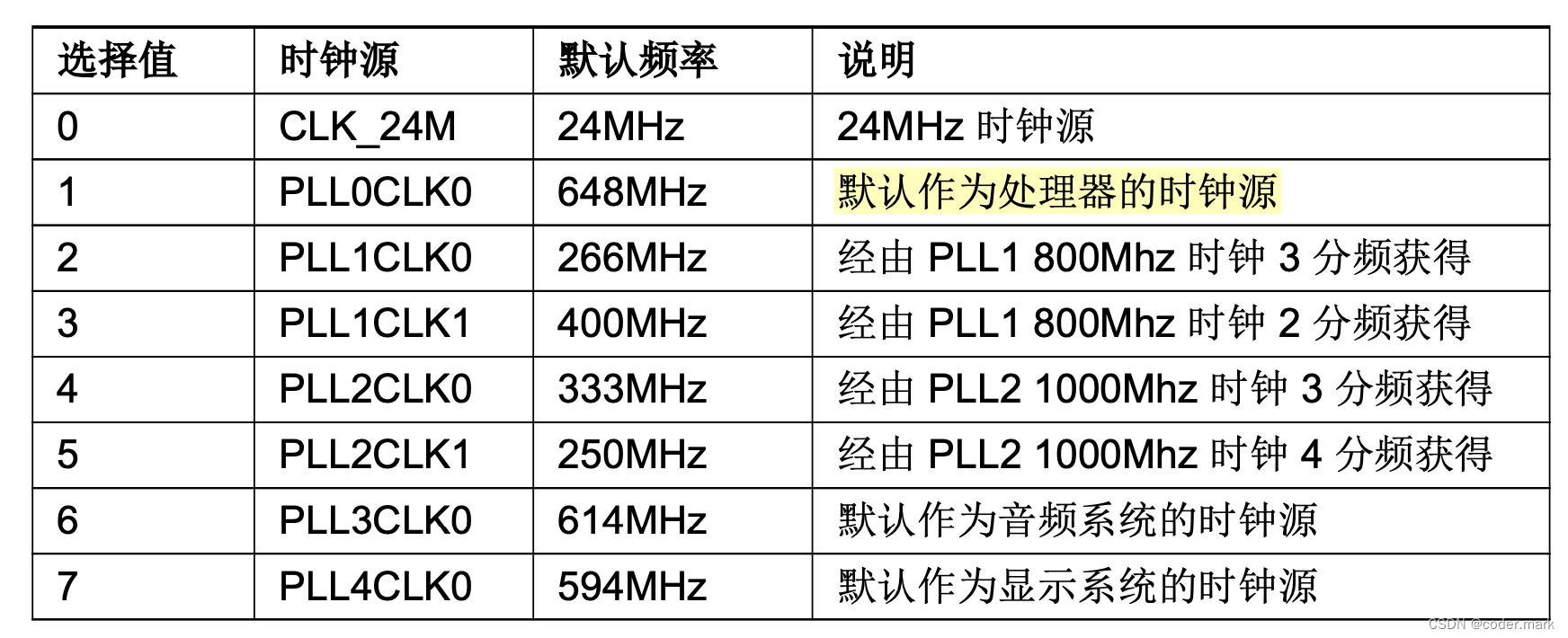

功能时钟在多个时钟源中进行选择(八选一),并且每个功能时钟的默认频率都已经设定好。

选择好时钟源之后,每个功能时钟又可以单独设置分频系数。

例如上图中CLK_TOP_HART0功能时钟作为CPU0核心时钟,其选择PLL0CLK0作为时钟源,然后再次二分频,PLL0CLK0的默认输出频率为648MHz,故CPU0的时钟为324MHz。

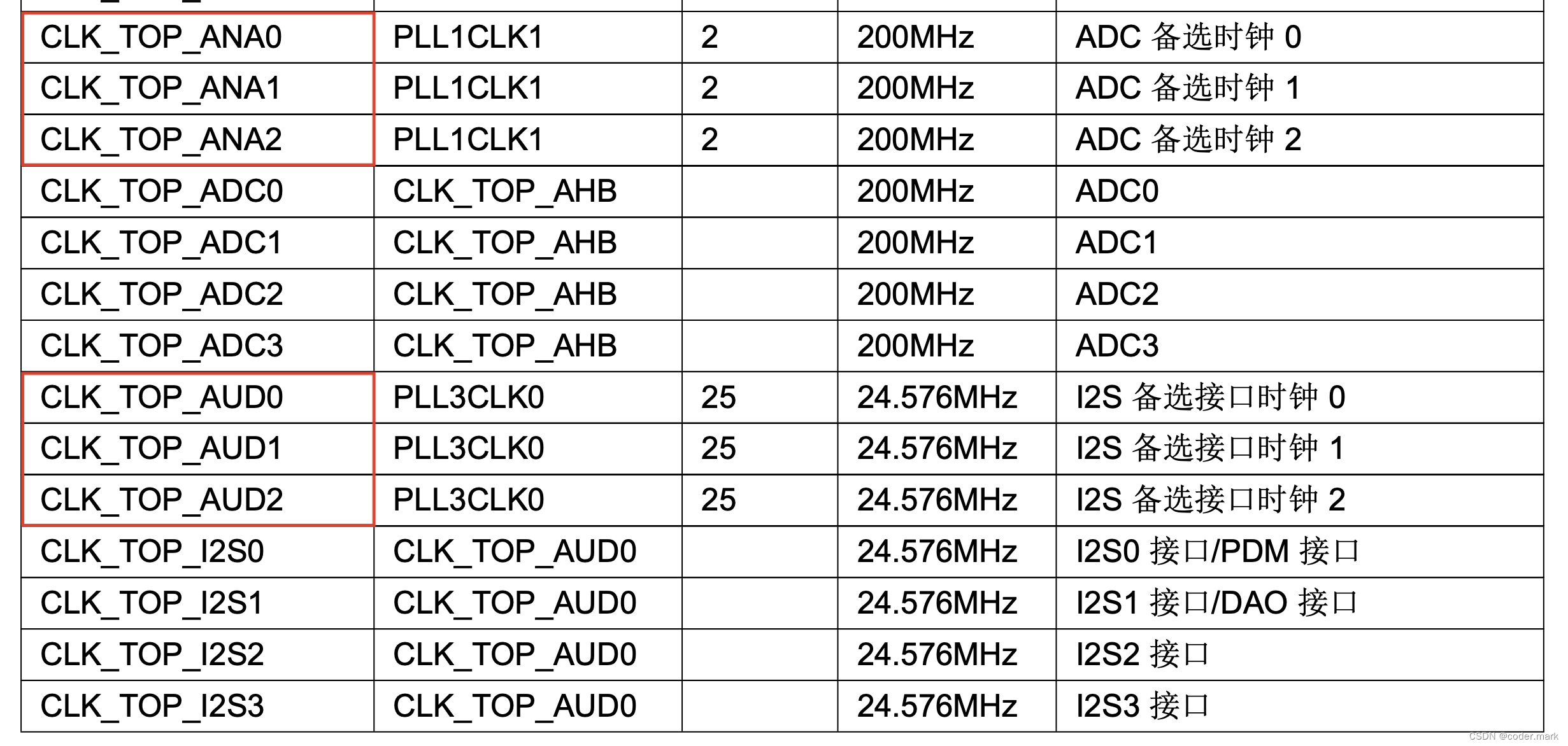

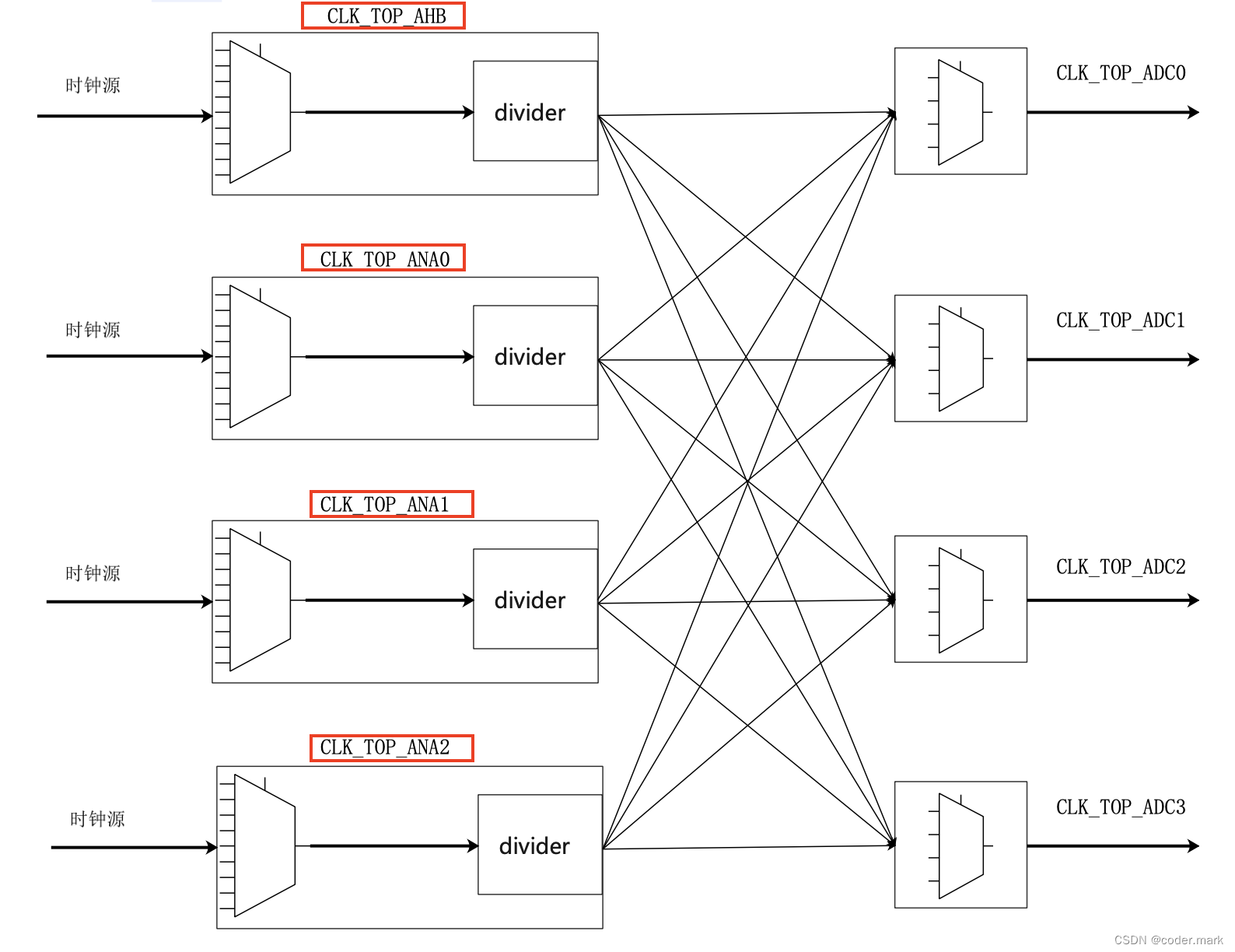

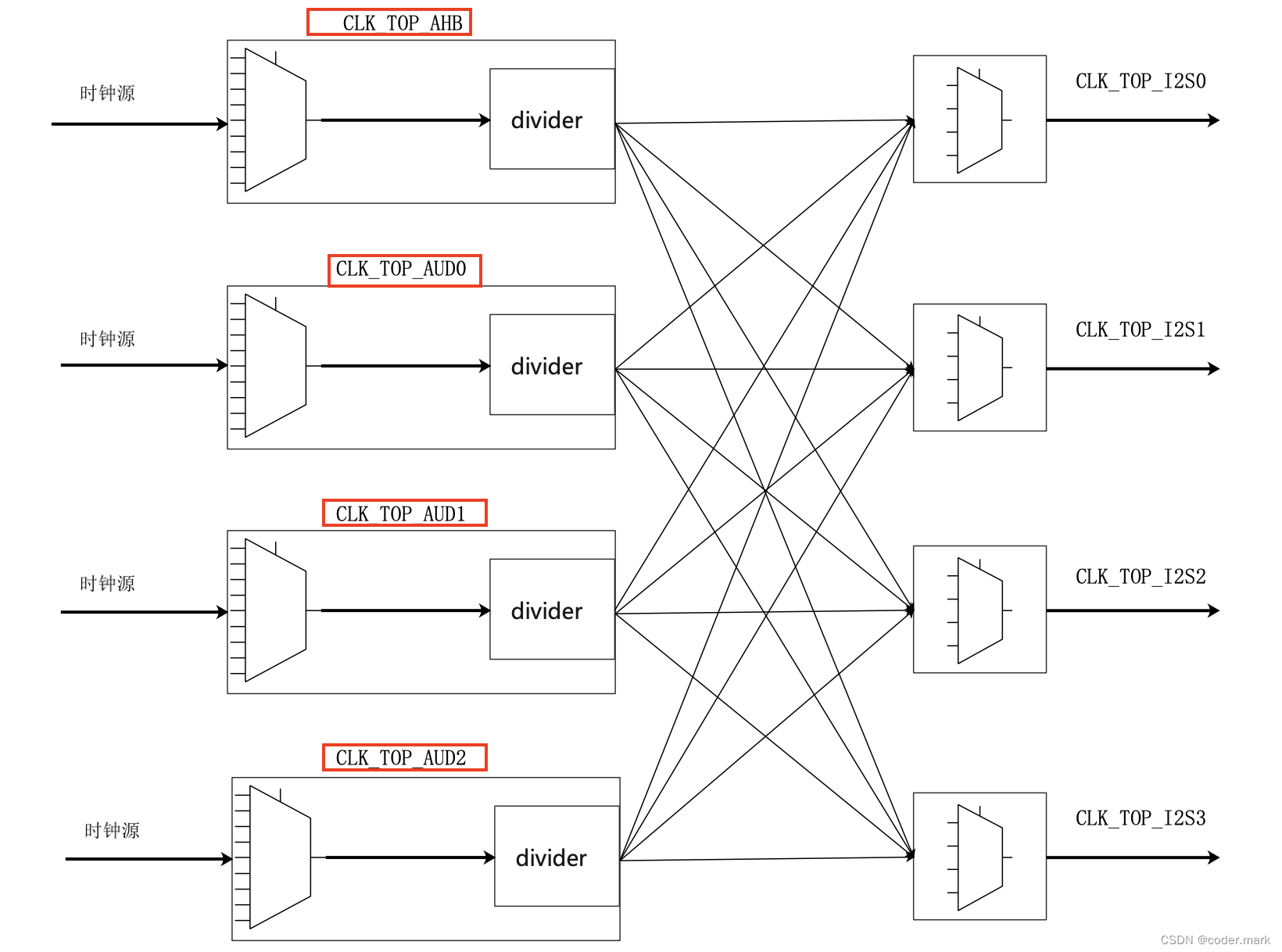

针对ADC和I2S模块存在一个二级时钟选择模块,可以从多个功能时钟中选择,这样的好处是多个ADC模块间可以同步、多个I2S模块间也可以同步。

2.直接使用时钟源的模块

3.资源节点

在系统电源域中,各种能够被开启或关闭的节点称为资源节点 (resource),包括各功能模块、功能时钟、子系统电源和复位、时钟源等。

下游的资源节点 ENET0 的正常工作依赖于 CLK_TOP_ENET0 供接口时钟,依赖于CLK_TOP_AXI 供总线时钟,还需要其所在的 CONN 子系统处于非复位状态且电源开关打开。

简言之,功能时钟也是作为资源节点被统一管理,如果要使用某个模块,那么这个模块的时钟就必须打开,也可以通过设置自动打开。

关于资源节点更加详细的内容请参考官方文档中描述。涉及到的内容较多,此处就不再一一说明。

4.PLL设置

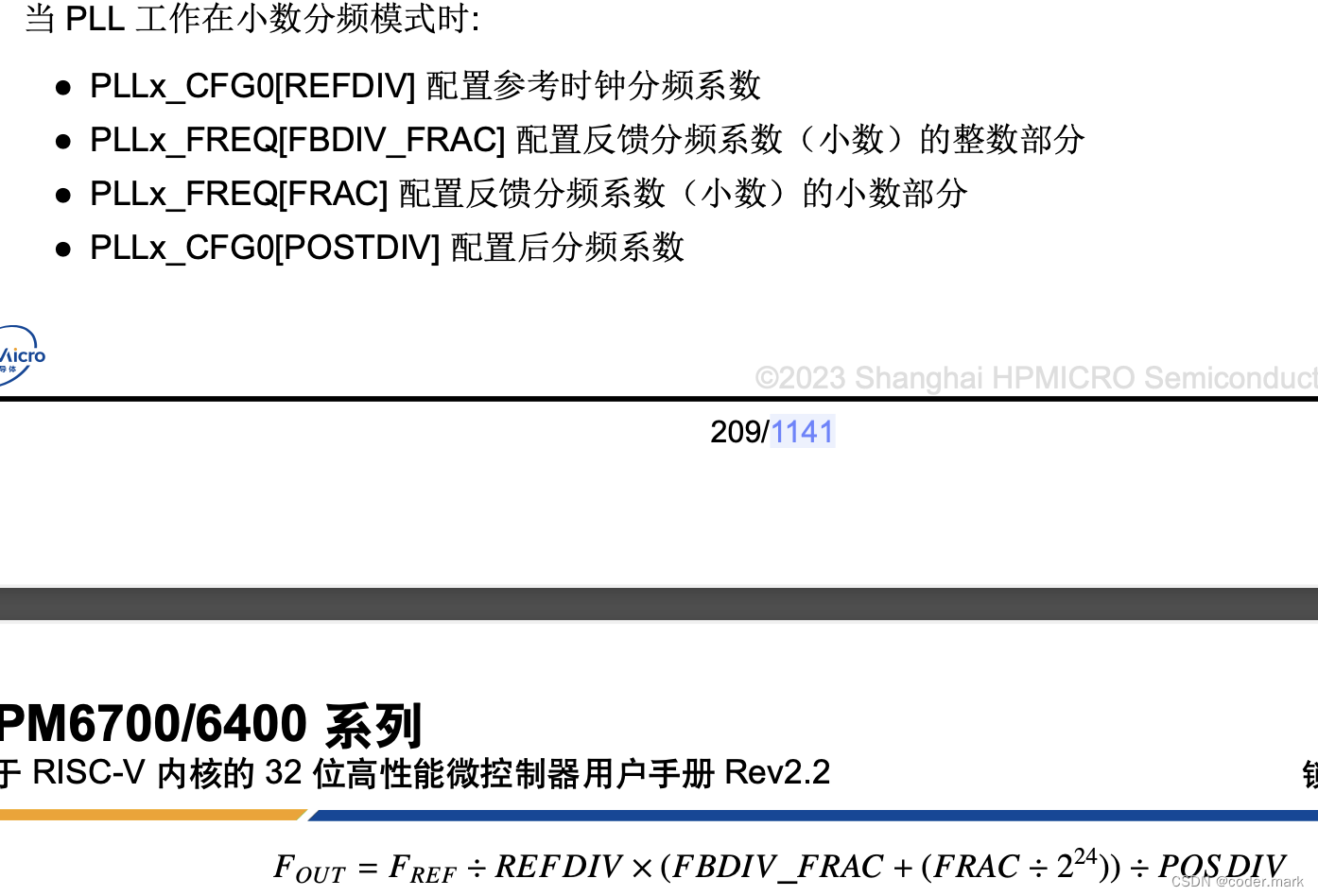

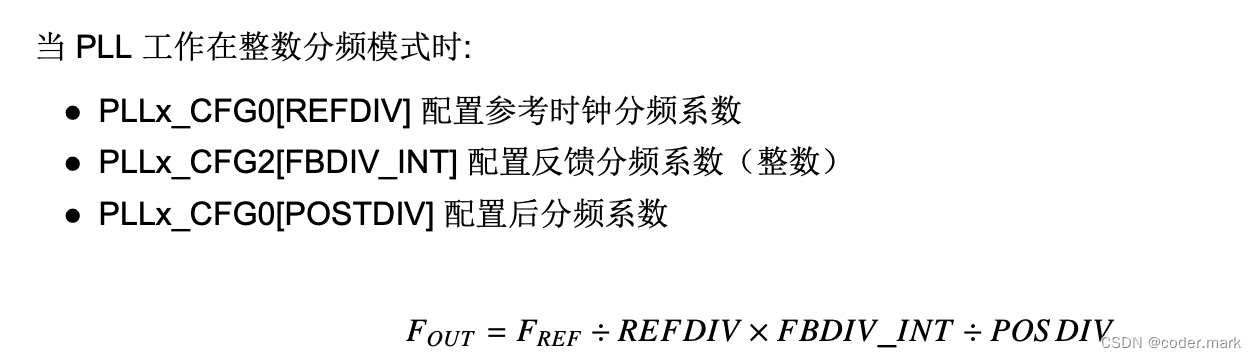

锁相环支持整数分频和小数分频的工作模式。

三、实战

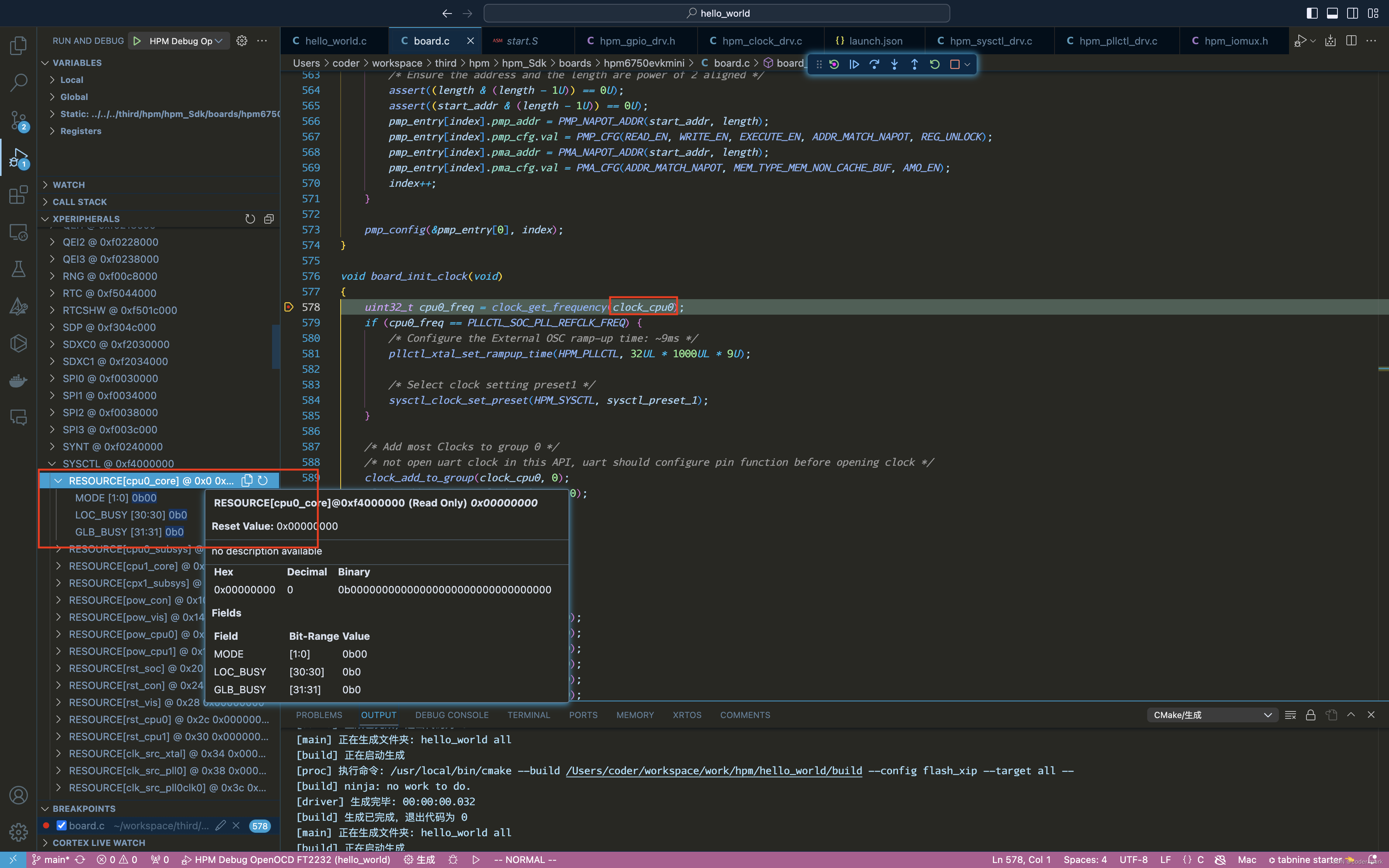

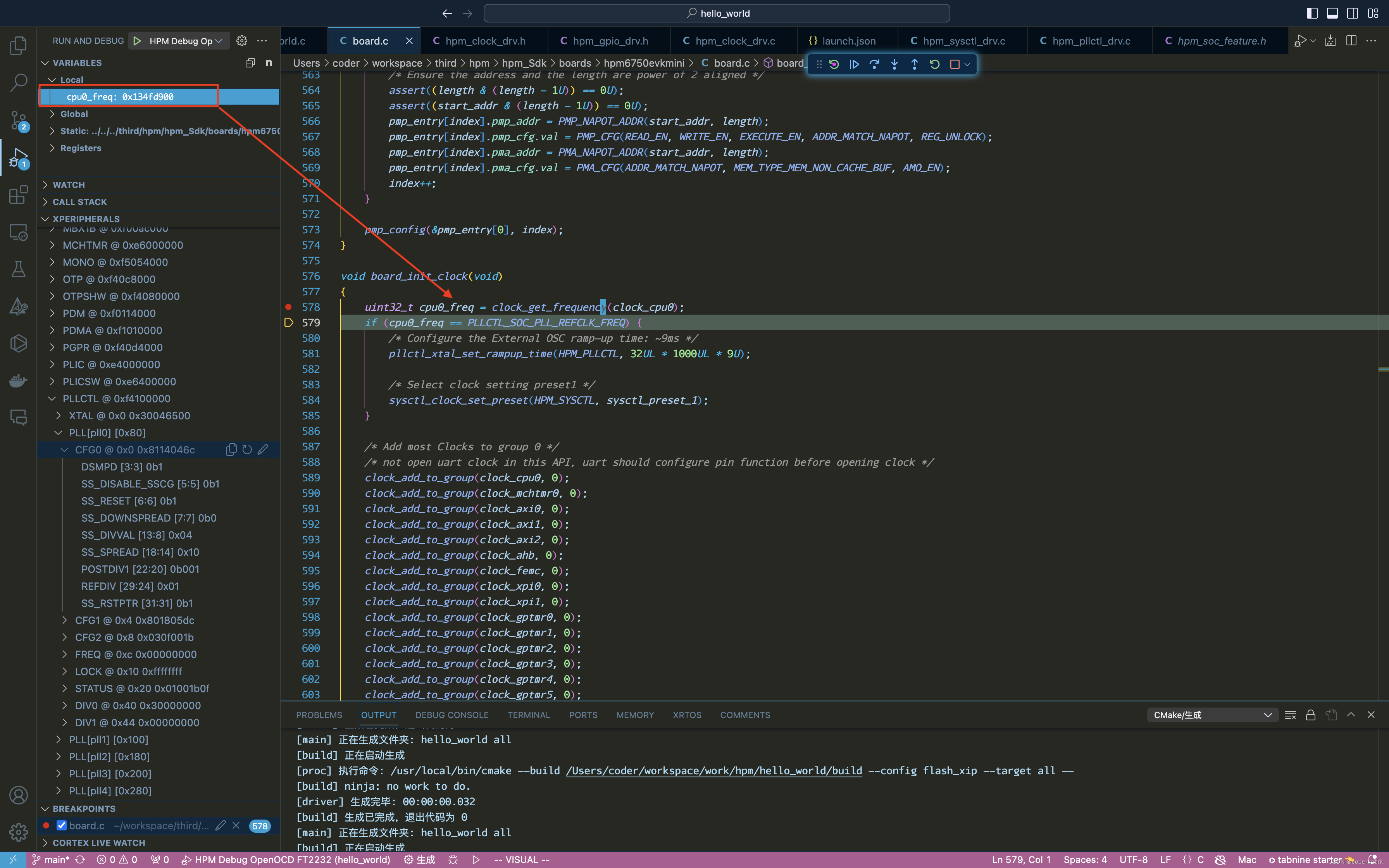

vscode打开hello_world工程进入调试模式并定位到board_init_clock函数

cd ~/workspace/work/hpm/hello_world

code .

clock_cpu0属于系统资源sysctl_resource_cpu0下CLK_SRC_GROUP_COMMON组clock_node_cpu0节点。

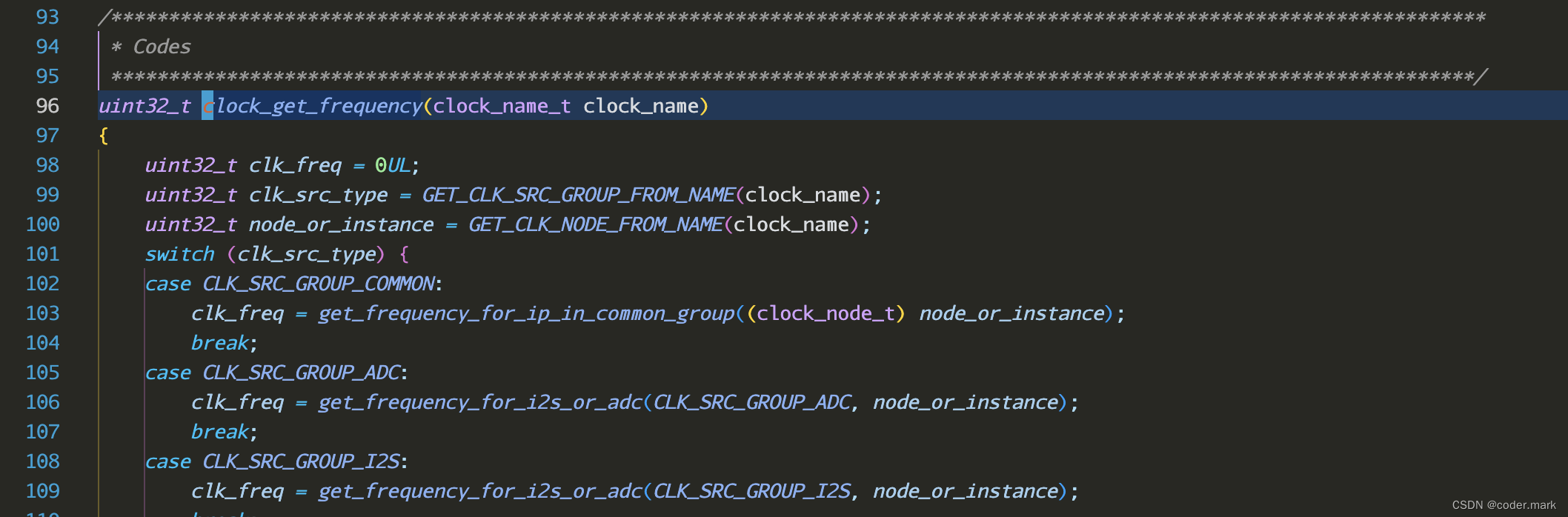

通过clock_get_frequency函数可以获取功能节点的时钟。

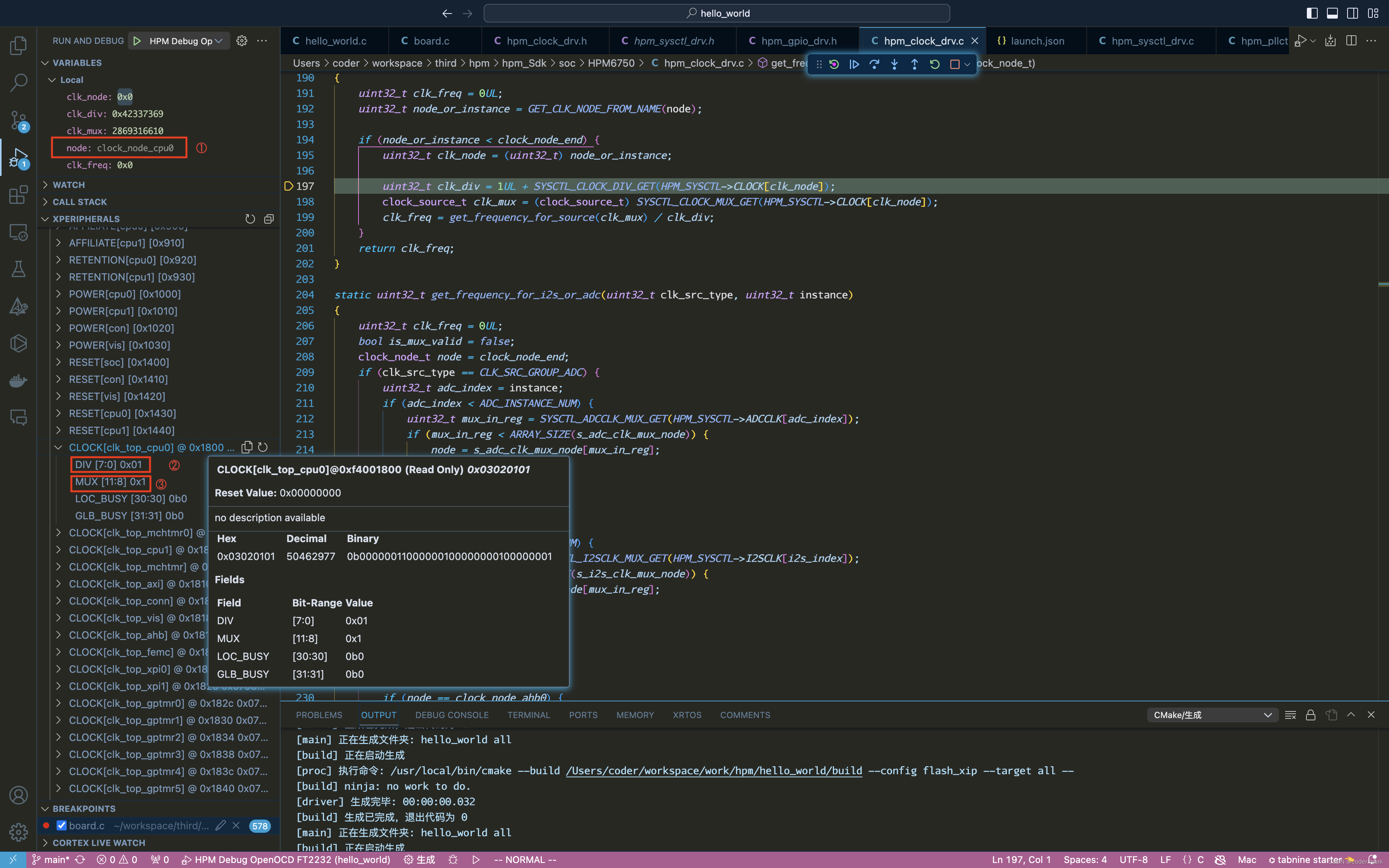

get_frequency_for_ip_in_common_group函数获取CLK_SRC_GROUP_COMMON组内的模块的时钟。

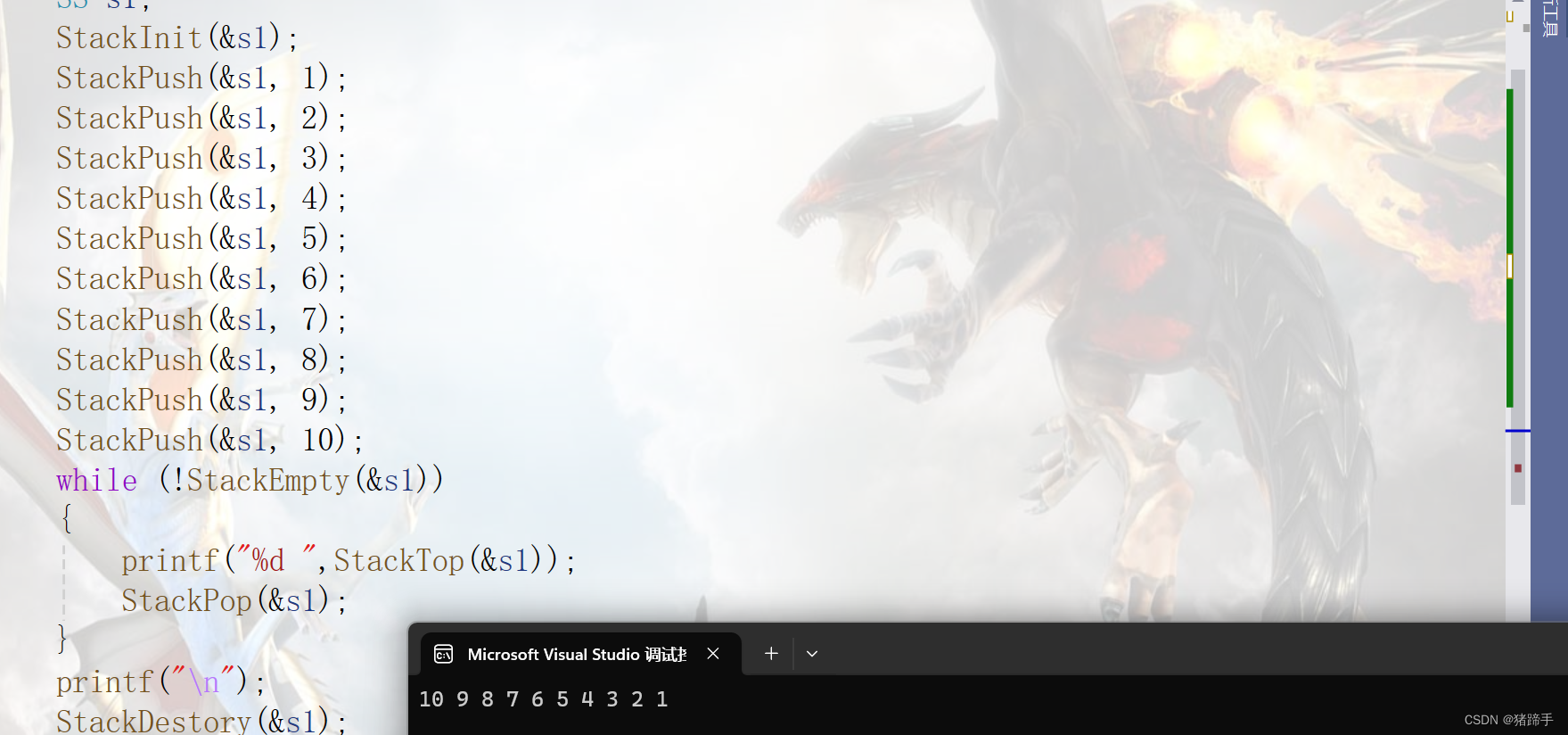

①获取节点clock_node_cpu0

②获取时钟分频系数DIV=1(2分频)

③获取时钟源索引MUX=1(八选一),选择了clock_source_pll0_clk0,也就是pll0作为时钟源。

获取PLL0的输出频率

PLLCTL_SOC_PLL_REFCLK_FREQ=24MHz

fbdiv=0x1b(27)

refdiv=0x1(1)

pos_div = 0x1

Fout = 24M / 1 * 27 / 1 = 648MHz,也就是说PLL0CLK0输出频率为648MHz,我们对功能时钟又进行了DIV=1(二分频),故CPU0时钟等于324MH。

至此,关于HPM6750的时钟系统的基本知识点就讲解完毕,关于资源节点的自动开启、硬件控制等知识点需自行钻研。