一、实验目的

1.掌握存储器的工作原理和接口。

2.掌握存储器的实现方法和初始化方法。

3.掌握RISC-V中存储器的存取方式。

二、实验内容

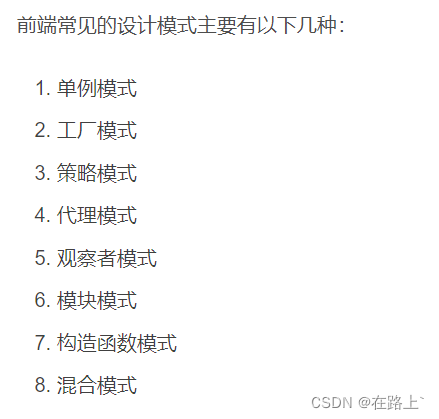

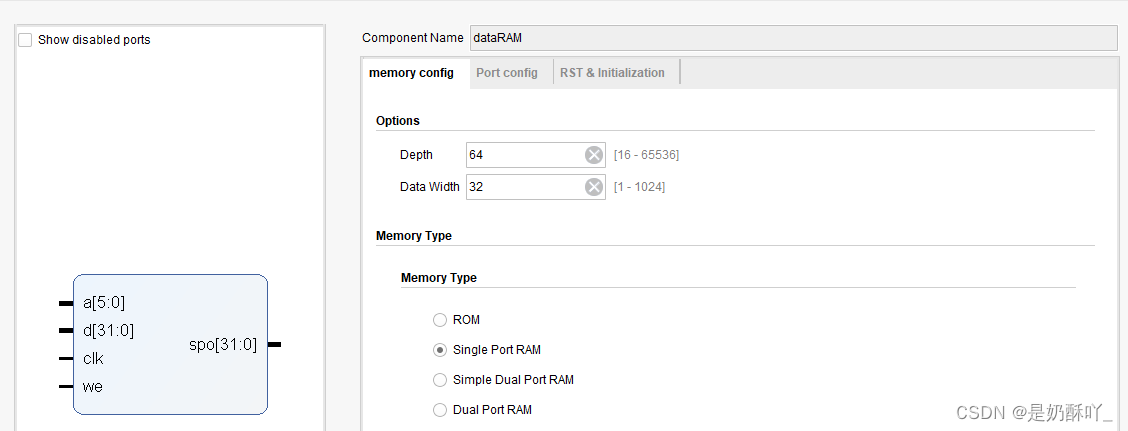

1.利用vivado IP核创建6432的ROM,并在 系数文件中设置数据为123489ab;

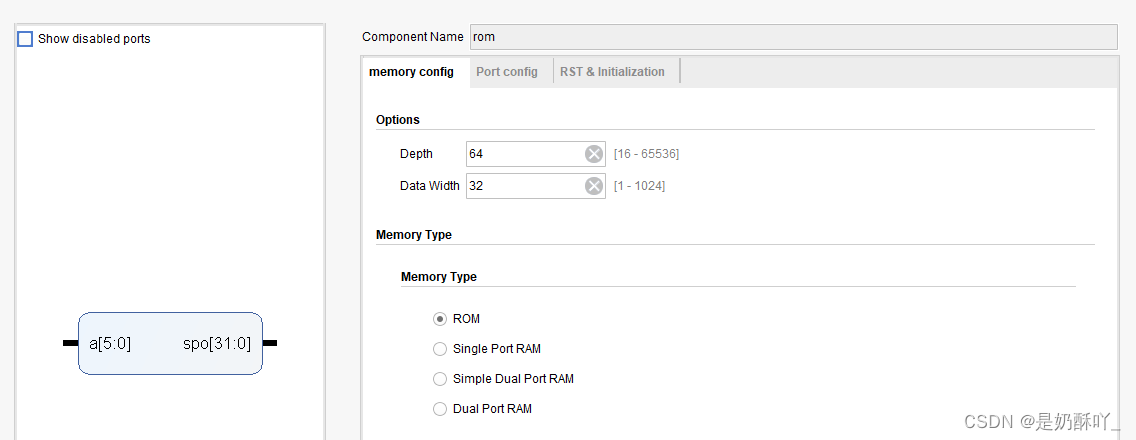

2.利用vivado IP核创建6432的RAM,并在 其上封装一个模块,使得其能完成risc-v 的load/store指令功能。

3.将ROM中的数据读出并保存到RAM中。

4.识别code编码对应的load指令将该数据 从RAM中读出来,结果显示数据的 [31:28][15:12][7:4]。

31:28 15:12 7:4

可选:用七段数码管显示该数据的全部 32位。

三、实验程序

rom

ram

ins

NEWRAM.v

module NEWRAM(

input [5:0] maddr,

input [31:0] mwdata,

input clk,

input we,

input [2:0] mm,

output [31:0] mdata

);

wire [31:0] tmp,tmp_b,tmp_h,tmp_bu,tmp_hu;

wire [31:0] tmp_mwdata;

dataRAM dr(.a(maddr),.d(tmp_mwdata),.clk(clk),.we(we),.spo(tmp));

wire lb,lh,lw,lbu,lhu,sb,sh,sw;

// 识别出各类读写方法

assign lb=~(|mm); // 000

assign lh=~(|mm[2:1])&mm[0]; // 001

assign lw=mm[2]&~(|mm[1:0]); // 100

assign lbu=~mm[2]&mm[1]&~mm[0]; // 010

assign lhu=~mm[2]&(&mm[1:0]); // 011

assign sb=mm[2]&~mm[1]&mm[0]; // 101

assign sh=(&mm[2:1])&~mm[0]; // 110

assign sw=&mm; // 111

// 读数据

assign tmp_b={{24{tmp[7]}},tmp[7:0]};

assign tmp_h={{16{tmp[15]}},tmp[15:0]};

assign tmp_bu={24'b0,tmp[7:0]};

assign tmp_hu={16'b0,tmp[15:0]};

assign mdata={32{lb}}&tmp_b|

{32{lh}}&tmp_h|

{32{lw}}&tmp|

{32{lbu}}&tmp_bu|

{32{lhu}}&tmp_hu;

// 写数据

assign tmp_mwdata={32{sb}}&{24'b0, mwdata[7:0]}|

{32{sh}}&{16'b0, mwdata[15:0]}|

{32{sw}}&mwdata;

endmodule

div.v(分频器)

module div(

input clk,

output clk_new

);

reg[17:0] q = 18'b0;

always @(posedge clk)

begin

q=q+1'b1;

end

assign clk_new=q[17];

endmodule

seven.v(七段数码管)

module seven(

input [3:0] data,

output reg[6:0] out

);

always @(*)

case (data)

4'b0000:out = 7'b1111110; // 7e

4'b0001:out = 7'b0110000; // 30

4'b0010:out = 7'b1101101; // 6d

4'b0011:out = 7'b1111001; // 79

4'b0100:out = 7'b0110011; // 33

4'b0101:out = 7'b1011011; // 5b

4'b0110:out = 7'b1011111; // 5f

4'b0111:out = 7'b1110000; // 70

4'b1000:out = 7'b1111111; // 7f

4'b1001:out = 7'b1111011; // 7b

4'b1010:out = 7'b1110111; // 77

4'b1011:out = 7'b0011111; // 1f

4'b1100:out = 7'b1001110; // 4e

4'b1101:out = 7'b0111101; // 3d

4'b1110:out = 7'b1001111; // 4f

4'b1111:out = 7'b1000111; // 47

default:out = 7'b1111110; //7e

endcase

endmodule

show.v(七段数码管显示)

module show(

input rst,

input clk,

input [31:0] result,

output reg[3:0] an1,

output reg[3:0] an2,

output [6:0] out1,

output [6:0] out2

);

wire clk_new;

div mydiv(.clk(clk),.clk_new(clk_new));

reg [3:0] data1,data2;

reg [1:0] cur_state,nex_state;

// 状态转移

always @(posedge clk_new)

// always @(posedge clk)

begin

if(!rst)

cur_state<=2'b00;

else

cur_state<=nex_state;

end

// 状态转移条件

always @(*)

begin

case(cur_state)

2'b00:

nex_state<=2'b01;

2'b01:

nex_state<=2'b10;

2'b10:

nex_state<=2'b11;

2'b11:

nex_state<=2'b00;

endcase

end

// 状态输出

always @(posedge clk_new)

// always @(posedge clk)

begin

case(cur_state)

2'b00:

begin

an1<=4'b0001;

data1<=result[19:16];

an2<=4'b0001;

data2<=result[3:0];

end

2'b01:

begin

an1<=4'b0010;

data1<=result[23:20];

an2<=4'b0010;

data2<=result[7:4];

end

2'b10:

begin

an1<=4'b0100;

data1<=result[27:24];

an2<=4'b0100;

data2<=result[11:8];

end

2'b11:

begin

an1<=4'b1000;

data1<=result[31:28];

an2<=4'b1000;

data2<=result[15:12];

end

endcase

end

seven myseven1(.data(data1),.out(out1));

seven myseven2(.data(data2),.out(out2));

endmodule

top.v(不用数码管显示)

module top(

input clk,

input rst,

input [2:0] code,

output [31:0] result

);

wire [31:0] addr=32'b0;

wire [31:0] outdata;

wire [31:0] result;

reg we;

reg [31:0] count;

always @(posedge clk)

begin

if (rst==1'b0)

begin

we<=1'b1;

count<=1'b0;

end

else

if (count>=32'b100)

we<=1'b0;

else

count<=count+1;

end

rom myrom(.a(addr),.spo(outdata));

NEWRAM nr(.maddr(addr),.mwdata(outdata),.clk(clk),.we(we),.mm(code),.mdata(result));

endmodule

top.v(用数码管显示)

module top(

input clk,

input rst,

input [2:0] code,

output [3:0] an1,

output [3:0] an2,

output [6:0] out1,

output [6:0] out2

);

wire [31:0] addr=32'b0;

wire [31:0] outdata;

wire [31:0] result;

reg we;

reg [31:0] count;

always @(posedge clk)

begin

if (rst==1'b0)

begin

we<=1'b1;

count<=1'b0;

end

else

if (count>=32'b100)

we<=1'b0;

else

count<=count+1;

end

rom myrom(.a(addr),.spo(outdata));

NEWRAM nr(.maddr(addr),.mwdata(outdata),.clk(clk),.we(we),.mm(code),.mdata(result));

show myshow(.clk(clk),.rst(rst),.result(result),.an1(an1),.an2(an2),.out1(out1),.out2(out2));

endmodule

四、仿真程序

mysim.v(不用数码管显示)

module mysim(

);

reg clk=1'b0;

reg rst=1'b0;

wire[31:0] result;

always

#10 clk=~clk;

initial

#11 rst=1'b1;

reg[2:0] code=3'b011;

top mytop(.clk(clk),.rst(rst),.code(code),.result(result));

endmodule

mysim.v(用数码管显示)

module mysim(

);

reg clk=1'b0;

reg rst=1'b0;

wire [3:0] an1,an2;

wire [6:0] out1,out2;

always

#10 clk=~clk;

initial

#11 rst=1'b1;

reg[2:0] code=3'b011;

top mytop(.clk(clk),.rst(rst),.code(code),.an1(an1),.an2(an2),.out1(out1),.out2(out2));

endmodule

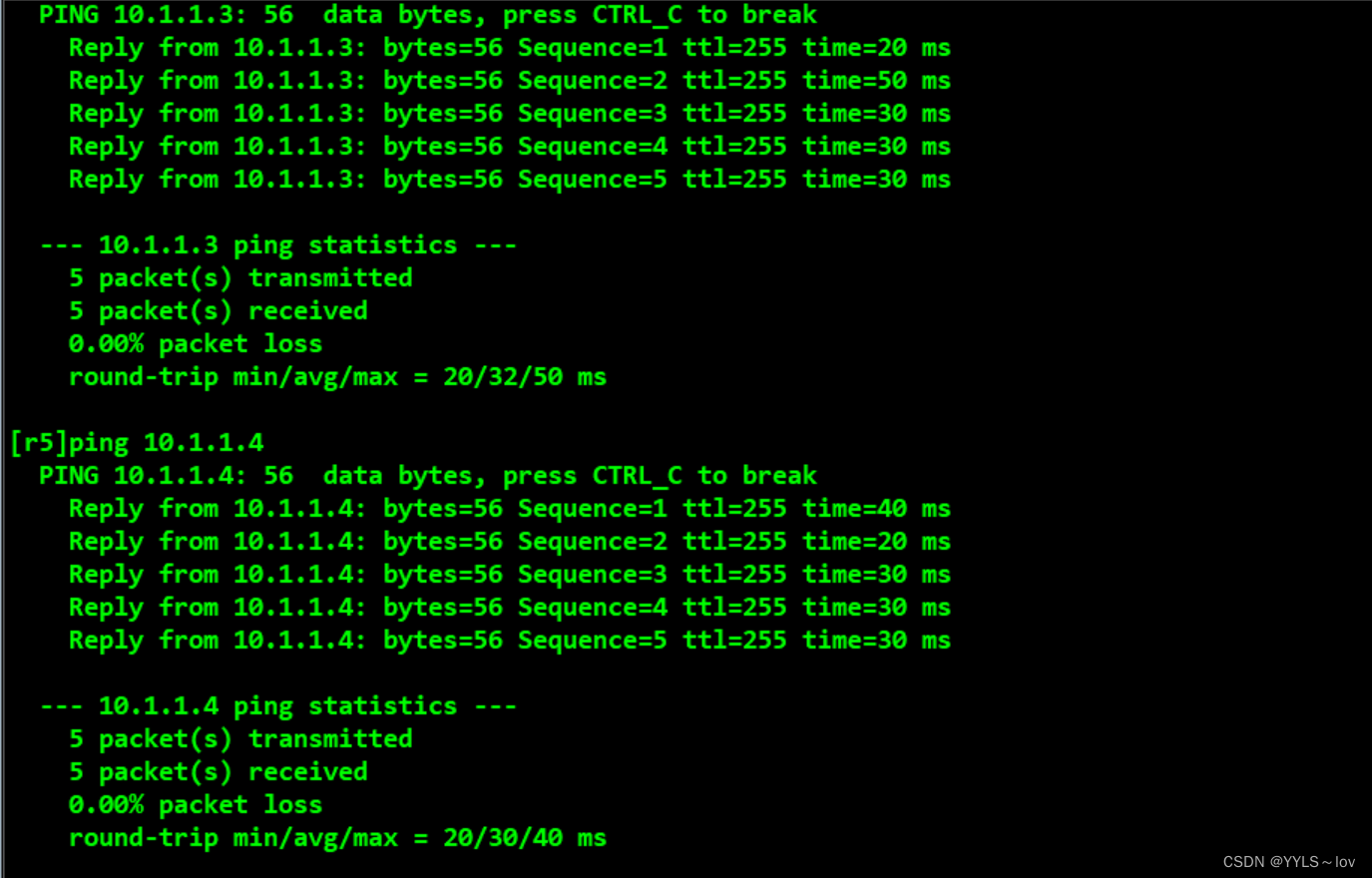

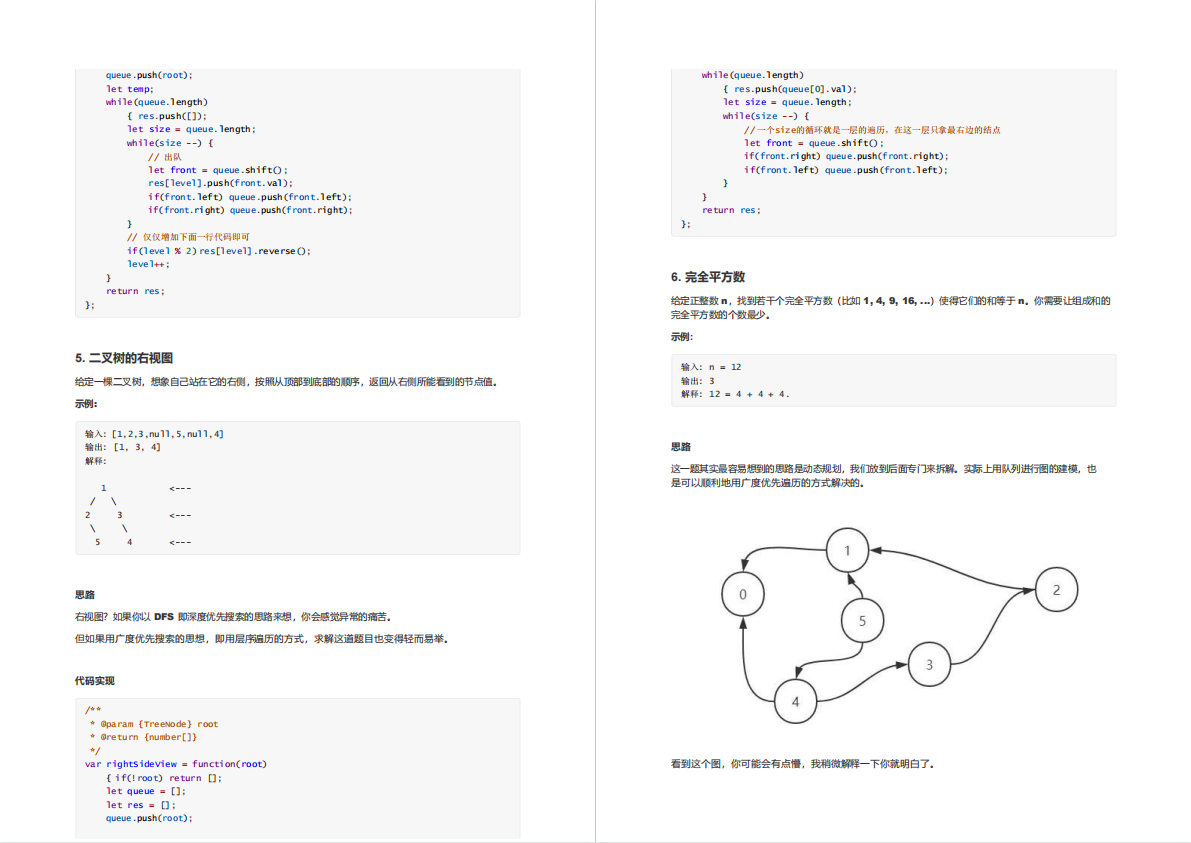

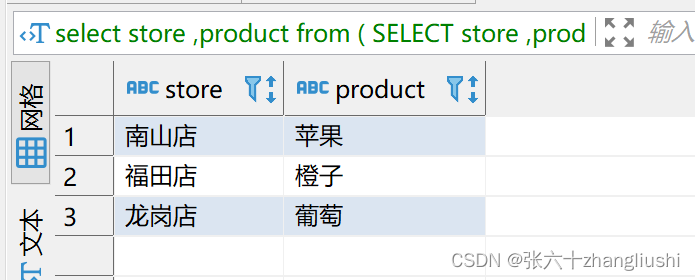

五、仿真结果

不用数码管显示:

用数码管显示:

六、实验结果

用数码管显示

![Rabbit客户端操作不同交换机[包含延迟类型]](https://img-blog.csdnimg.cn/b61baf95e18a431a82cd1ae06c2d1751.png)

![[牛客复盘] 牛客2022跨年场 20221212](https://img-blog.csdnimg.cn/07c2880706ad4a5eb2363567714be2e9.png)

![[ XSS-labs通关宝典 ] xss-labs 通关宝典之 less1 - less5](https://img-blog.csdnimg.cn/a125b39655294c87bb54d2a8c7691701.png)