在计算和数据中心、军事和航天、政府、仪器与测量、金融服务和广播和视频等行业,需要高可靠性的硬件和软件产品,帮助客户更快地开发部署新一代产品,减少技术和市场风险,我司研发的低延迟TCP/IP的IP核的传输速率高于传统网口,延迟较低,可以解决网络通信、数据包处理、云储存、和加速算法等应用遇到的技术挑战。

低延迟TCP/IP的IP核有以下特点:

●10G以太网连接。

●完整的RTL层1、2、3和4,包括专有的超低延迟全硬件TCP/IP、ARP、ICMP、MAC和PC实现。

●时钟可配置为250兆赫,以改善延迟结果。

●易于使用的标准化Avalon和AXI-4接口。

●每个FPGA有多个实例,每个实例有多个逻辑接口,每个接口都具有唯一的IPv4、MAC地址、VLAN ID、网关和掩码。

●每个实例可使用128个TCP会话,每个会话都可以在服务器或客户机模式下动态配置。

IP特性有:

●RTL层:

■layer 1:IEEE802.3

■layer 2:IEEE802.3, ARP

■layer 3:IPv4 和ICMP

■layer 4:TCP (RFC 793)

●TCP 管理

■128个TCP会话

■每个会话都可以在服务器或客户机模式下动态配置

●可配置的TCP选项

■VLAN优先级,在发射时插入PCP和DEI字段

■MSS

■窗口比例系数

■Timestamp

●可定制的最大传输单元

■9000字节的有效载荷,支持从标准帧到巨型帧

●Mac处于混杂模式

■访问Mac Raw TX/RX接口

●多接口

■每个实例有8个逻辑接口

■链接到任何会话

■每个接口可配置VLAN

●Avalon和Axi4-4接口

■128位宽接口,从156.25到250MHz,用于TCP/IP客户端端口

■64位宽的接口,从156.25到250MHz,用于MAC客户端端口(TCP/IP旁路)

●IP 配置/管理

■32位Avalon-MM/AXI- 4 Lite从机控制接口,用于MAC和TCP配置

■可在MAC或TCP会话级别监控的状态和统计信息

●可定制的TCP重传缓冲区

■可定制缓冲区大小(深度和宽度)

■可定制的内部或外部内存支持(DDRX、QDRX等),取决于性能和FPGA大小要求

●物理接口

■PC和PMA之间的PMA并行数据(Altera Stratix V的PMA直接模式和第10代的PC直接模式)

■PC和Mac之间的MII 64位流媒体接口

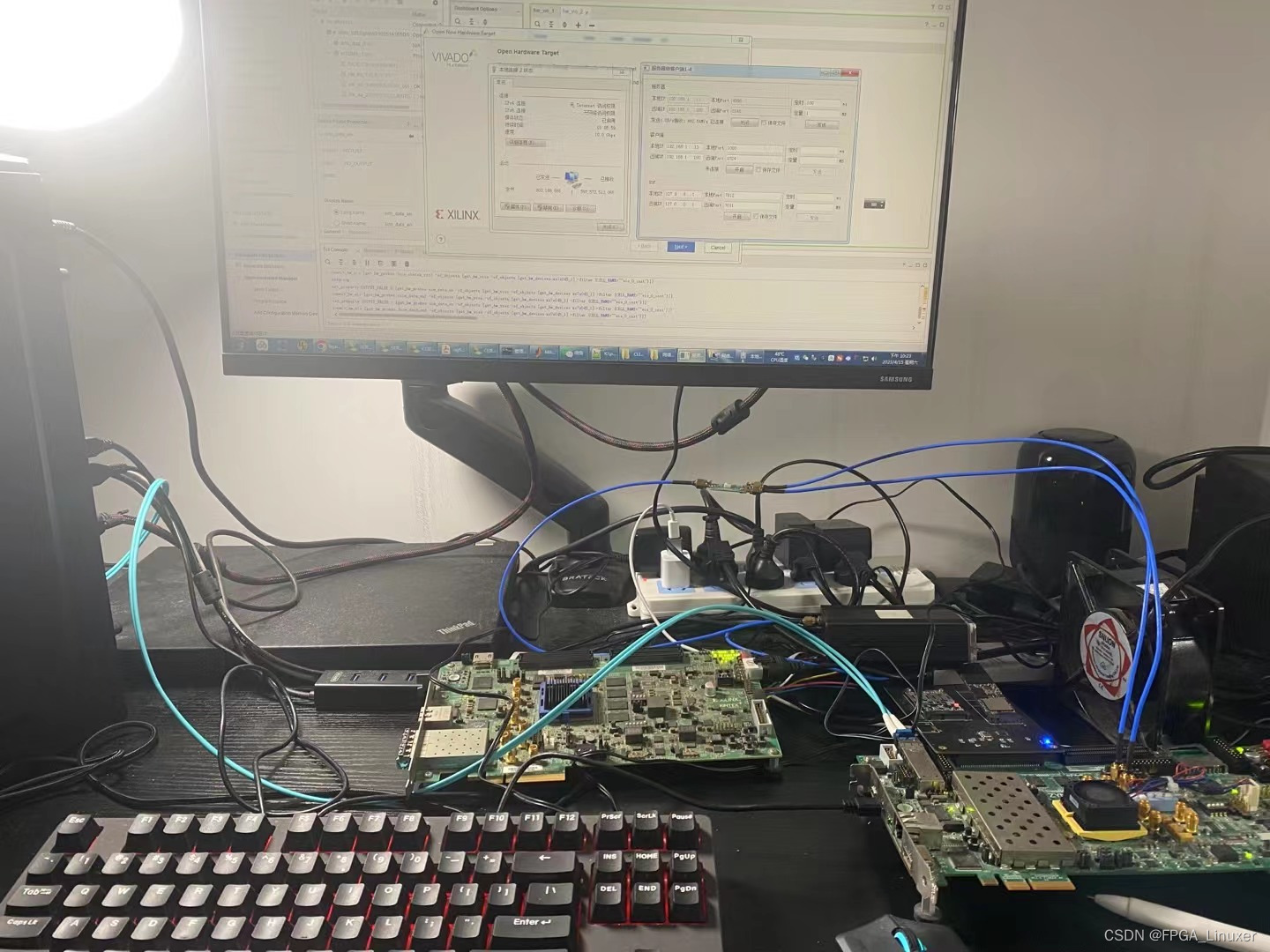

实测环境