本文仅供学习,不作任何商业用途,严禁转载。绝大部分资料来自----数字集成电路——电路、系统与设计(第二版)及中国科学院段成华教授PPT

超大规模集成电路设计----RTL级设计之FSM(八)

- 7.1 CPLD的时序模型

- 7.1.1 XPLA3 时序模型

- 7.1.2 具体时序组成(重点)

- 1. Pad to Pad(tPD)

- 2. Clock Pad to Output Pad (tCO)

- 3. Clock to Setup (tCYC)

- 4. Clock to Pad

- 5. Path Ending at Clock Pin of Flip-Flop

- 6. Pad to Setup

- 7.Setup to Clock at Pad (tSU or tSUF)

- 8. fSYS

- 9. 总结

- 7.2 使用FSM设计存储控制器

- 单个写、阵发读的存储器控制原理

- 状态机的泡泡图

- 补充:如何寻找状态转移图中能够使用移位寄存器制作的部分

为什么要学习这一章:详细讲述了FPGA的时序模型及FSM的设计。标黄部分属于必须掌握的部分,黑体部分表示强调部分,有助于理解,对于普通字体部分,时间紧急的浏览者可以选择忽略,对于初学者,建议博文每部分都需要连贯阅读。

7.1 CPLD的时序模型

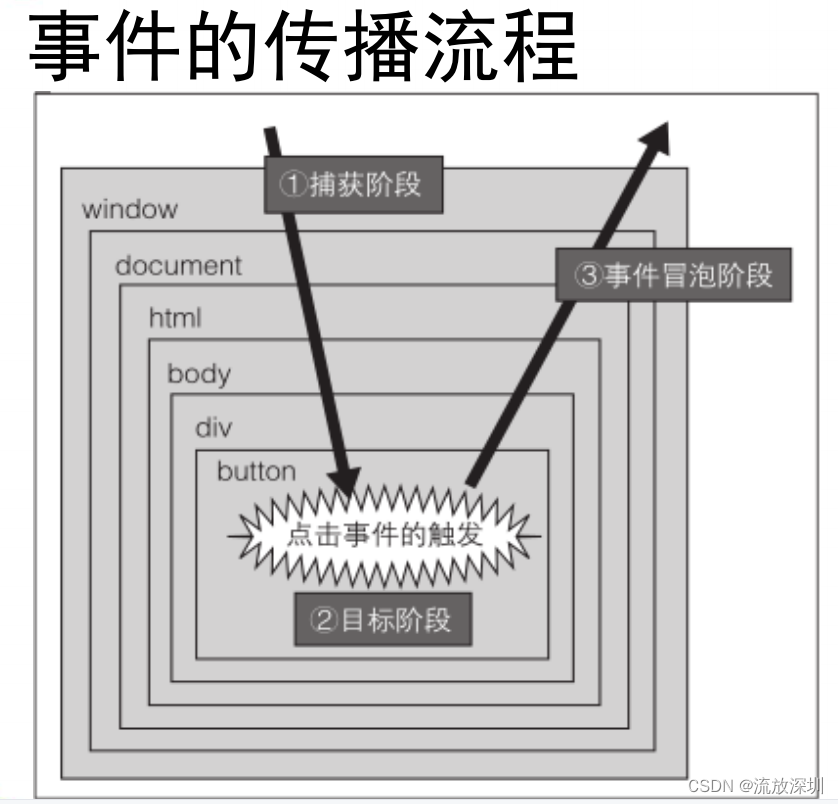

7.1.1 XPLA3 时序模型

- T L O G I 1 \color{red}{\mathrm{T}_{\mathrm{LOGI1}}} TLOGI1是简单逻辑的延时

- T L O G I 2 \color{red}{\mathrm{T}_{\mathrm{LOGI}2}} TLOGI2是复杂逻辑的延时

- T L O G I 3 \color{red}{\mathrm{T}_{\mathrm{LOGI3}}} TLOGI3是反馈逻辑的延时

- T F I N \color{red}T_{\mathrm{FIN}} TFIN是快速输入的逻辑延时

- T I N , T O U T \color{red}{\mathrm{T}_{\mathrm{IN}},\mathrm{T}_{\mathrm{OUT}}} TIN,TOUT是输入输出路径的延时

- T F \color{red}{\mathrm{T}_{\mathrm{F}}} TF是输出反馈路径的延时

- T P T C K \color{red}{\mathrm{T}_{\mathrm{PTCK}}} TPTCK乘积项时间

- T G C K \color{red}{\mathrm{T}_{\mathrm{GCK}}} TGCK是全局时钟

7.1.2 具体时序组成(重点)

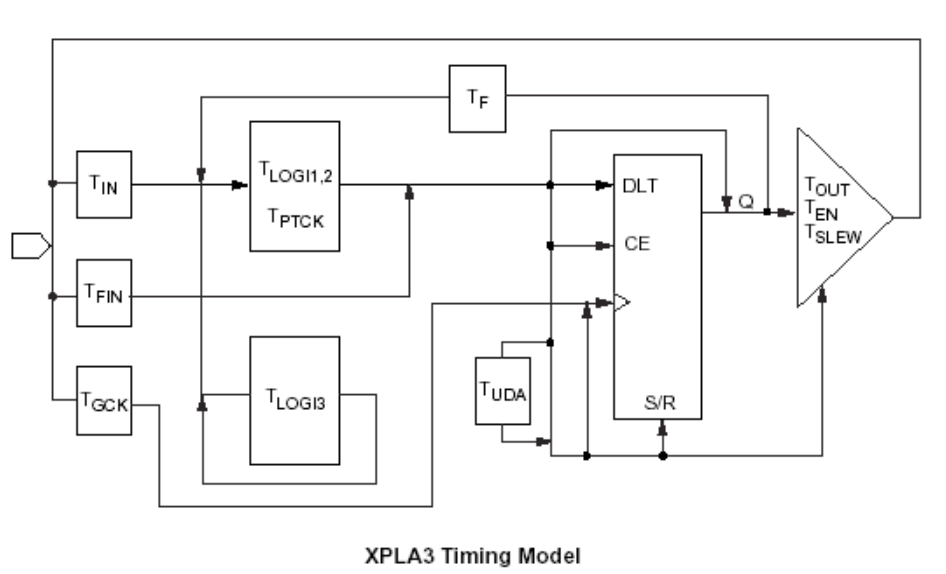

1. Pad to Pad(tPD)

从输入焊盘(Input Pads)开始,到输出焊盘(Output Pads)结束所经路径的时间。路径不通过寄存器。

如图所示,

tPD

\text{tPD}

tPD延时按该公式

tPD=tIN+tLOGI2(tLOGI1)+tOUT

\text{tPD=tIN+tLOGI2(tLOGI1)+tOUT}

tPD=tIN+tLOGI2(tLOGI1)+tOUT 计算

2. Clock Pad to Output Pad (tCO)

时钟在时钟输入的焊盘跳变开始,到寄存器数据输出到该单元的输出焊盘结束所花的时间,路径不通过寄存器。

tCO=tGCK + tCOI + tF + tLOGI2 (or tLOGI1) + tOUT

\text{tCO=tGCK + tCOI + tF + tLOGI2 (or tLOGI1) + tOUT}

tCO=tGCK + tCOI + tF + tLOGI2 (or tLOGI1) + tOUT

3. Clock to Setup (tCYC)

寄存器到寄存器的周期时间。包括源寄存器 tCO 和目标寄存器 tSU。假设所有寄存器都对上升沿敏感。

tCYC=tCOI+tF+tLOGI2+tSUI

\text{tCYC=tCOI+tF+tLOGI2+tSUI}

tCYC=tCOI+tF+tLOGI2+tSUI

4. Clock to Pad

从寄存器的时钟引脚(Clock Pin)开始,到输出焊盘(Output Pad)结束。

Clock to Pad =tCOI+tF+tLOGI2+tSUI.

\text{Clock to Pad =tCOI+tF+tLOGI2+tSUI.}

Clock to Pad =tCOI+tF+tLOGI2+tSUI.

Clock Pad to Output Pad (tCO) = Clock to Pad+tGCK

\text{Clock Pad to Output Pad (tCO) = Clock to Pad+tGCK}

Clock Pad to Output Pad (tCO) = Clock to Pad+tGCK

5. Path Ending at Clock Pin of Flip-Flop

从触发器的时钟的输入焊盘开始到触发器时钟Pin输入结束的路径。路径不通过寄存器。

这个时间就是

tGCK

\text{tGCK}

tGCK

6. Pad to Setup

从焊盘开始到寄存器D/T输入结束的路径(包括接收触发器的tSUI)。路径不通过寄存器。

Pad to Setup=tIN+tLOGI2+tSUI

\text{Pad to Setup=tIN+tLOGI2+tSUI}

Pad to Setup=tIN+tLOGI2+tSUI

7.Setup to Clock at Pad (tSU or tSUF)

Setup to Clock at Pad (tSU or tSUF)=Pad to Setup - tGCK \text{Setup to Clock at Pad (tSU or tSUF)=Pad to Setup - tGCK} Setup to Clock at Pad (tSU or tSUF)=Pad to Setup - tGCK

8. fSYS

最大时钟工作频率

寄存器到寄存器路径从触发器时钟输入开始,通过触发器 Q 输出和任意数量的组合逻辑电平传播,并在接收触发器 D/T 输入(包括接收触发器的 tSUI)结束。

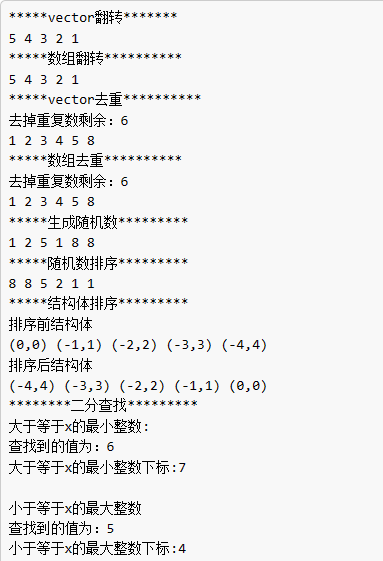

9. 总结

- tPD = tIN + tLogiC + tOUT

- tCO = tGCK + tCOI + tF + tLogic + tOUT

- tCYC = tCOI + tF + tLogic + tSUI

- Clock to Pad = tCOI + tF + tLogic + tOUT

- Path Ending at Clock Pin of Flip-Flop = tGCK

- Pad to Setup = tIN + tLogic + tSUI

- Setup to Clock at Pad = Pad to Setup - tGCK

- tSYS = 最大工作频率

tSU和tSUI的区别在于前一个是D Pad的建立时间,后一个是D pin的建立时间

tCO和tCOI的区别在于前一个是Clock Pad到寄存器输出的时间,后一个是Clock Pin 到寄存器输出的时间。

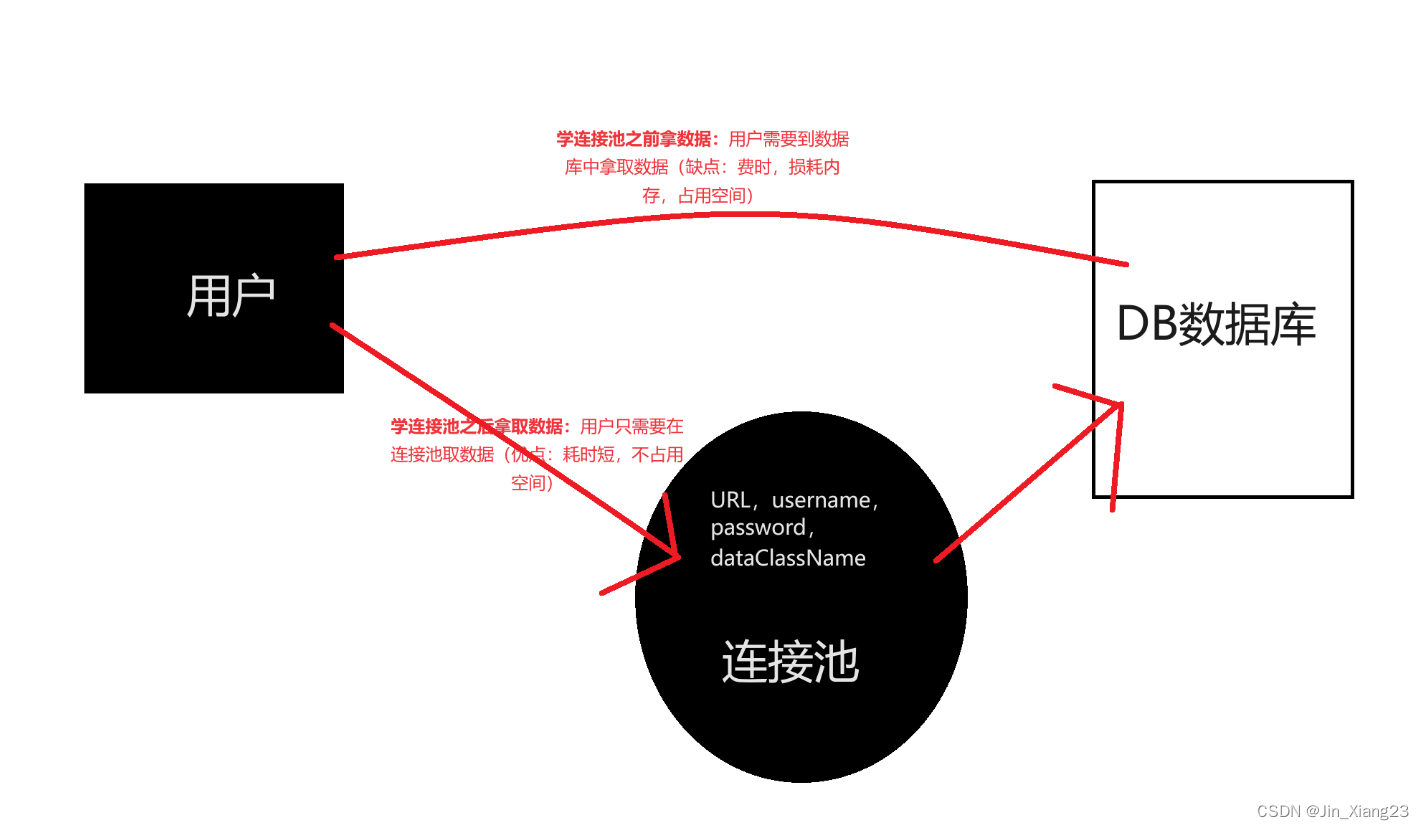

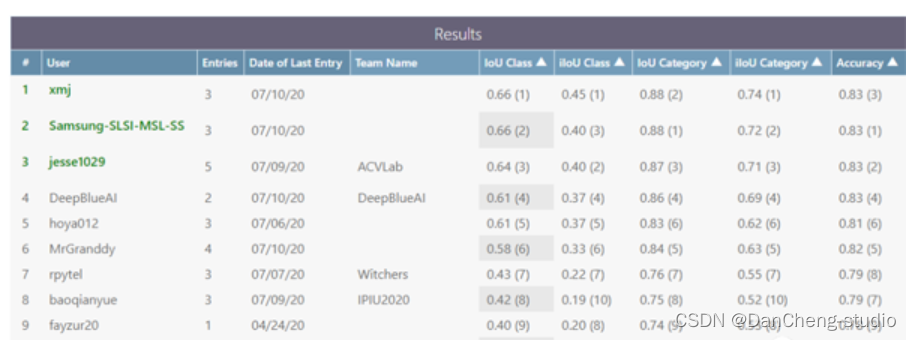

7.2 使用FSM设计存储控制器

单个写、阵发读的存储器控制原理

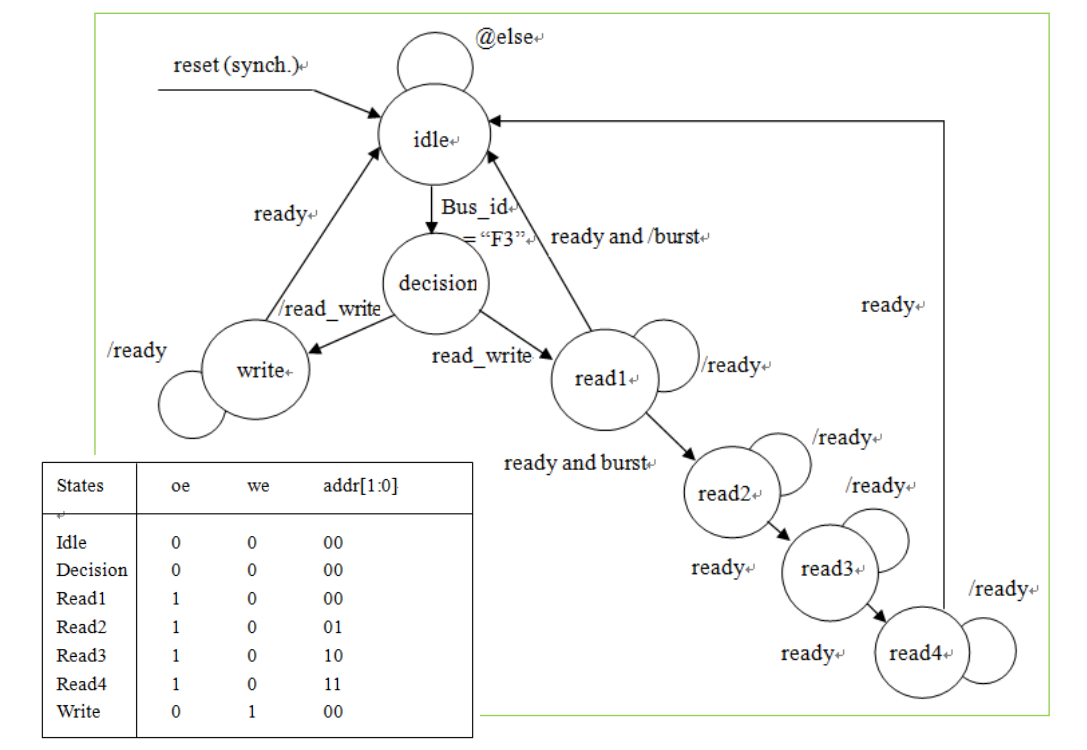

状态机的泡泡图

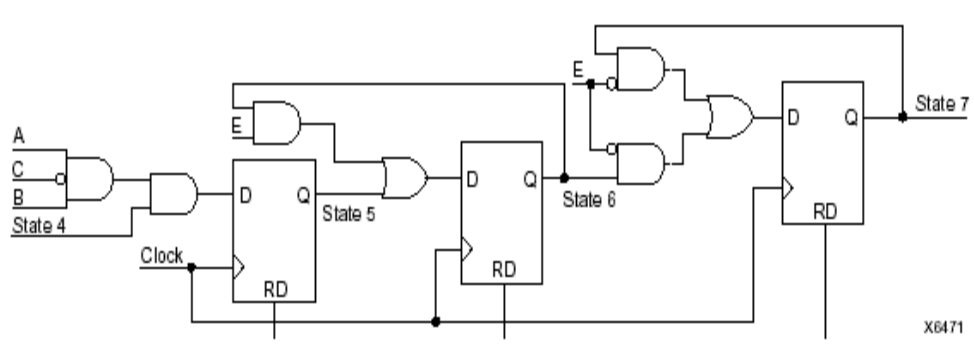

在上面的FSM中,最复杂的是IDLE电路,如下图所示。

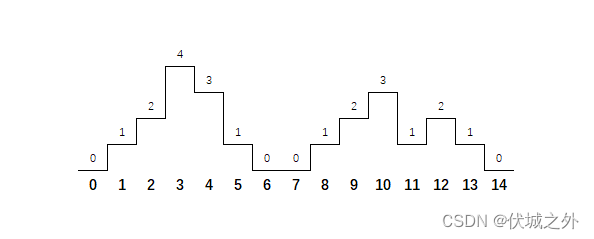

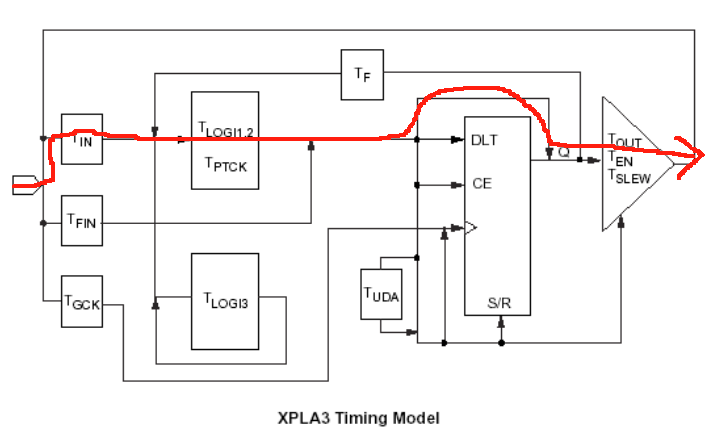

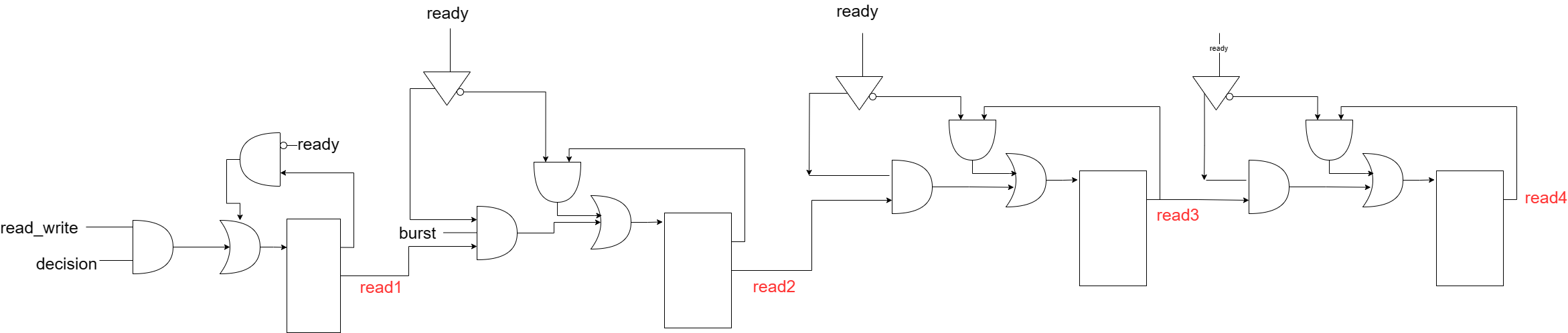

上面的转移图中,能画成移位寄存器的部分如下。

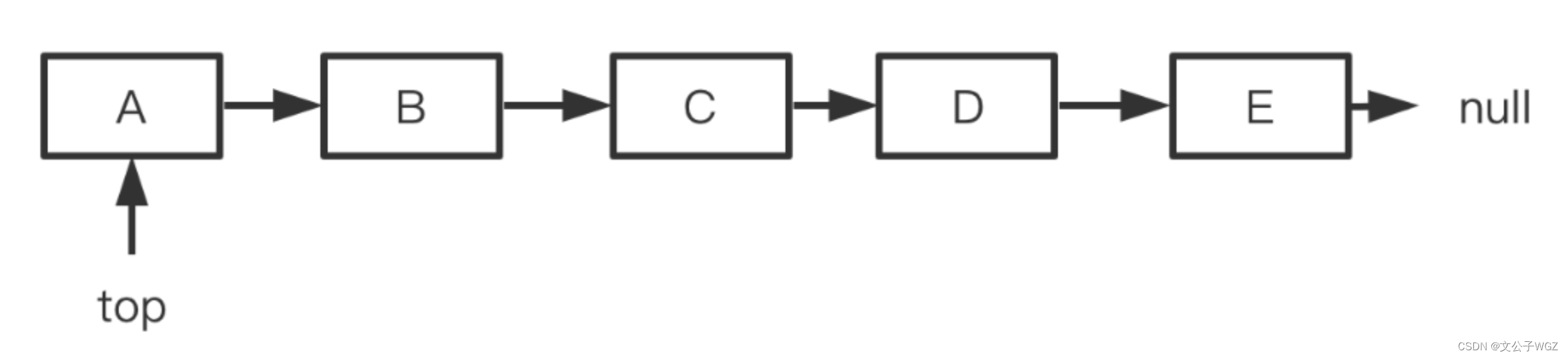

补充:如何寻找状态转移图中能够使用移位寄存器制作的部分

- 找到除自循环只有一个输入的所有状态。

- 把第一个只有一个输出的状态作为第一个寄存器的输入。

- 有自循环的需要写反馈逻辑。

下面来看一个例子

认为其可使用移位寄存器的部分如下红线所示。

画出移位寄存器电路如下。