【写在前面】

电路与电子学好像是从2020级开设的课程,故实际上目前只有2020与2021两个年级考过期末考试。

这门课程主要由所谓的“数电”与“模电”组成。而且先学的“模电”后学的“”数电,故期中考试主要以“模电”为主,期末考试主要以“数电”为主。研究该门课程前身之一的“数电”部分的试卷有很大的意义。

这个系列节选一些往年数电的考题,由于当时自己做的答案未及时整理,已经散佚不可考。故不附答案,读者可以自己试做,整理答案。试卷难度都不是很大,基本上都是PPT上例题的改动。

一、简答题(共 10 分)

1

.请从电路结构和输入输出关系阐述组合电路与时序电路的区别。(

4

分)

2

.请简述状态机图的条件约束。(

6

分)

二、(15 分)

一个比较电路的输入有两个

4

位无符号二进制整数

X

和

Y

,以及一个控制

信号

MIN/MAX

,输出是

4

位无符号二进制整数

Z

。输入与输出之间的关系为:如果

MIN/MAX

=

1

,则

Z

=

min

(

X , Y

);如果

MIN/MAX

=

0

,则

Z

=

max ( X , Y )

。试用

比较器

74x85

和

4

重

2-1

多数复用器实现这个电路。

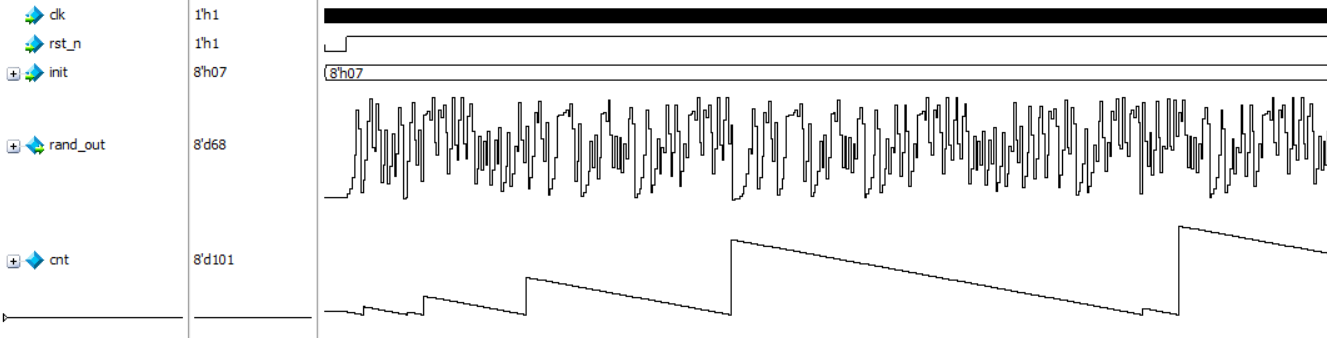

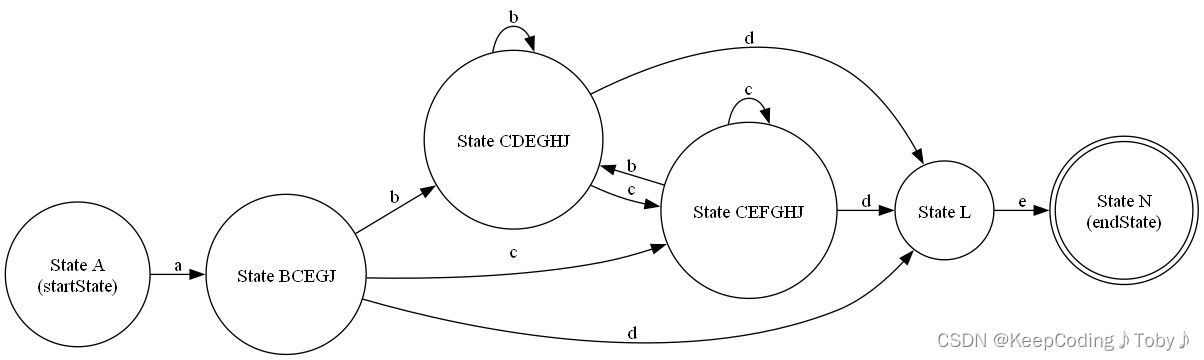

三、(20 分)

试分析下图所示的同步时序电路。

1

.写出状态方程;

2

.做出状态图和状态表;

3

.画出

10

个时钟周期

Q2

、

Q1

、

Q0

的波形图,假设起始状态

Q2Q1Q0=000

;

4

.描述电路的功能。、

四、(15 分)

采用

D

触发器和逻辑门设计一个计数器,该计数器的计数顺序为:

0, 3, 1, 2,

5, 6, 4, 7

。

五、(15 分)

用图(

a

)所示的可编程逻辑块

CLB1

和

CLB2

,实现以下状态表描述的

Moore

机。要求给出

CLB1

和

CLB2

内部(图(

b

)所示)

0-10

各位的逻辑值。

六、(15 分)

已知

6

个寄存器

A

、

B

、

C

、

D

、

E

、

F

,当寄存器的

EN=0

时,其输出为高阻。

如果

LOAD=1

,则当时钟上升沿到来时总线上的数据被装入寄存器中。在信号

C

1

和

C

0

的控制下,可完成如下操作:

如果

C

1

C

0

=00

,则

A

存储到

C

;

如果

C

1

C

0

=01

,则

B

存储到

D

;

如果

C

1

C

0

=10

,则

A

存储到

E

;

如果

C

1

C

0

=11

,则

B

存储到

F

。

请运用相关部件或逻辑门,采用总线方式实现寄存器传输,画出电路图。

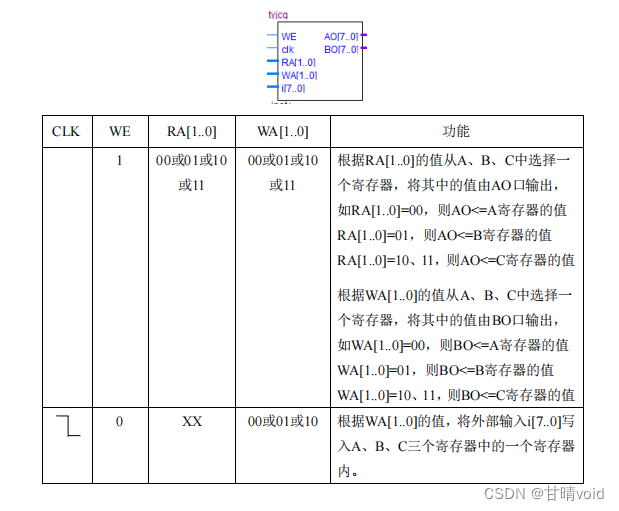

七、(10 分)

试采用 VHDL

设计一个寄存器组,该寄存器组由

3

个

8

位寄存器

A

、

B

、

C

组成,实现对这

3

个寄存器的读写操作。其接口及功能如下: