基本单元:

1.1 与非门

1.2 或非门

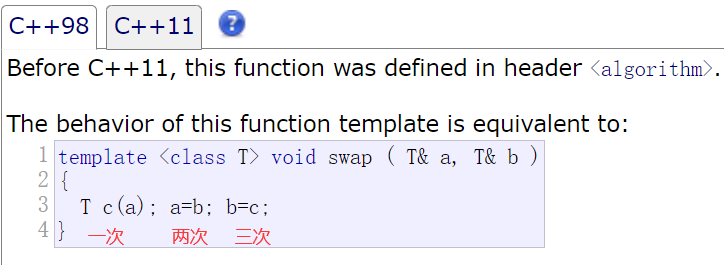

2输入与非门需要4个晶体管(n输入与非门需要2xn个晶体管),非门需要两个晶体管,2输入或非门需要6个晶体管(n输入或非门需要 2xn + 2个晶体管)。

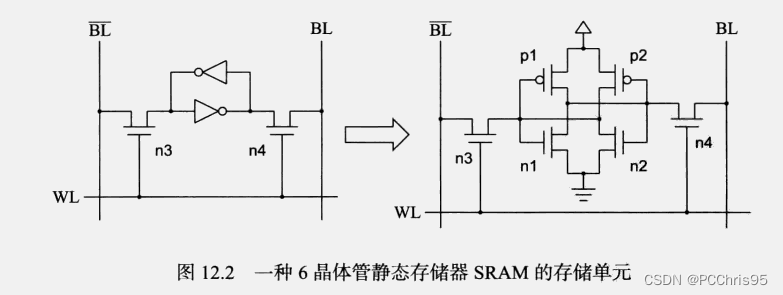

静态存储器

1bit的静态存储由6个晶体管组成,如下图所示:其中WL是地址选择信号,BL是数据线,当WL为高电平时可以对存储单元进行读写;静态存储器接口简单,速度快,耗电量也大,价格高,一般用于做cache和TLB设计。

MUX

1.1 1bit二选一mux

下图是一个一位二选一的MUX,只需要14个晶体管就可以做出来。

1.2 1bit四选一mux

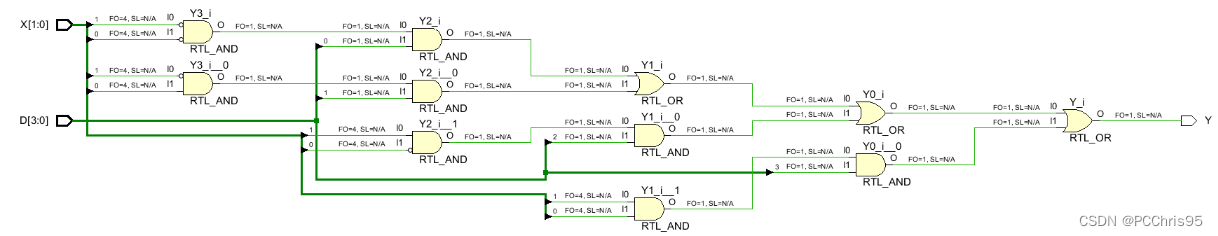

生成的逻辑图如下,需要8个与门,3个或门,总共需要(8x2 + 3 x 2 + 2)24个晶体管。 1.3多bit四选一晶体管

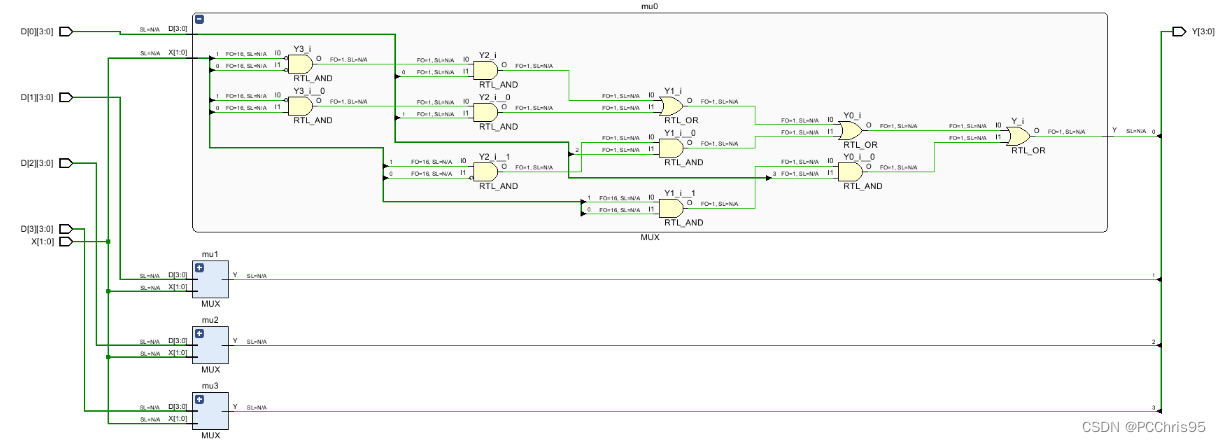

1.3多bit四选一晶体管

对于一个多bit的晶体管,比如n bit,那么就需要n个1bit四选一的mux,此时需要n x 24个晶体管。

对于8选一的MUX,只需要将X的位数变为3位X[2:0],电路逻辑也几乎增加一半,对于16选一,只需要将X的位数变为4位X[3:0]。

对于面积来说,以单bit 2选一MUX作为基准,那么mbit N选一的mux可能大致评估下面积为:m/2 * N/2 * 14(面积肯定会优化,不一定准确,但是可以用来评估面积的大致范围);

移位器

如下图所示是一个32位的全位移位器,可以任意移位(如果是64位全移位那么需要7层电路),

是由5个32位2选一的多路器来组成,当sa全为1时表示移31位,当sa[0]为1时表示移一位,当sa[1]为1时表示移两位,以此类推。

D触发器

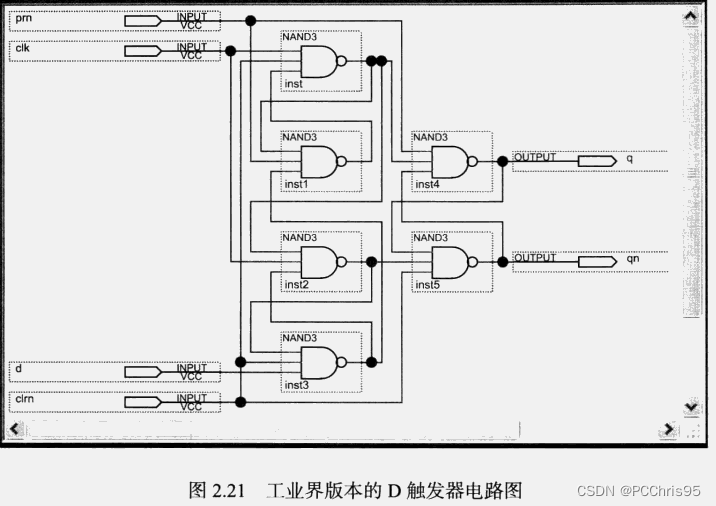

工业界的D触发器由6个NAND组成,如下图所示:

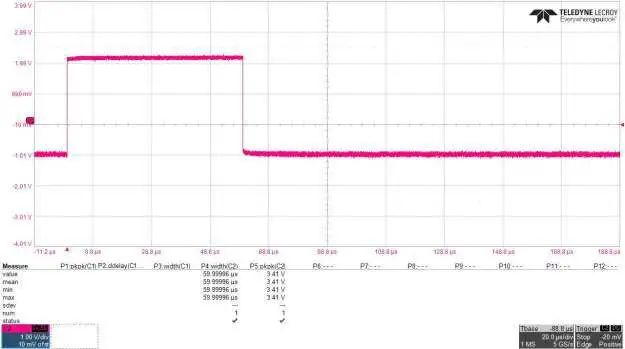

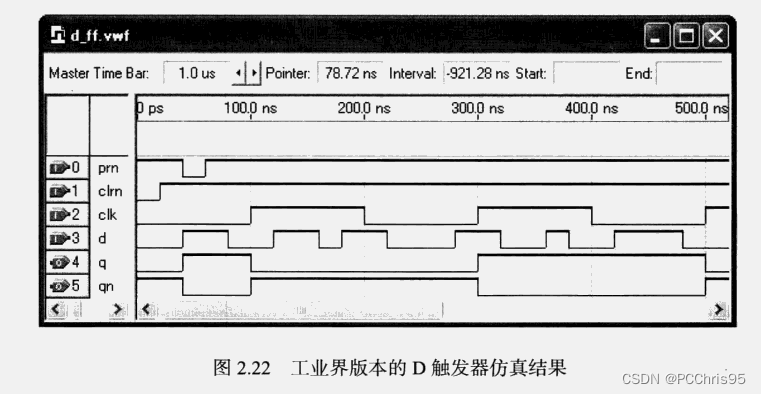

其中时序图为下图所示:在每次始终的上升沿进行采样;

![[附源码]java毕业设计竞价拍卖系统](https://img-blog.csdnimg.cn/c7ba7b9053b74a728d9d6d30719ac6f6.png)