1. RISC-V指令集介绍

RISC-V 念作 “risk-five”,代表着 Berkeley 所研发的第五代精简指令集。

该项目 2010 年始于加州大学伯克利(Berkeley)分校,希望选择一款 ISA用于科研和教学。经过前期多年的研究和选型,最终决定放弃使用现成的X86 和 ARM 等 ISA,而是自己从头研发一款:

- List itemX86:太复杂,IP 问题

- List itemARM:一样的复杂,而且在 2010 年之前还不支持 64 位,以及同样的 IP 问题。

2. 模块化ISA

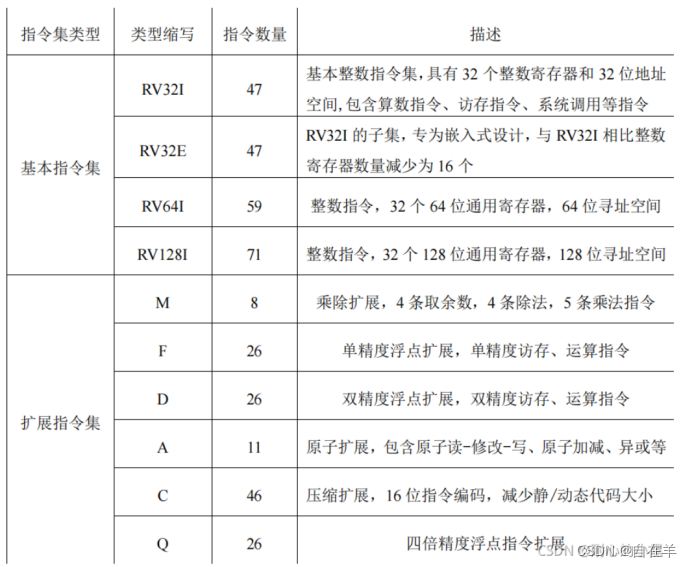

指令集分为基本部分和扩展部分,基本部分的指令集所有硬件实现都必须有这一部分实现,而扩展部分则是可选的。扩展部分又分为标准扩展和非标准扩展。例如,乘除法、单双精度的浮点、原子操作就在标准扩展子集中。

由 1 个基本整数指令集 + 多个可选的扩展指令集组成。基础指令集是固定的,永远不会改变。

RISC ISA = 1个基本整数指令集 + 多个可选的扩展指令集。

“I” 基本整数集,其中包含整数的基本计算、Load/Store和控制流,所有的硬件实现都必须包含这一部分。

“M” 标准整数乘除法扩展集,增加了整数寄存器中的乘除法指令。

“A” 标准操作原子扩展集,增加对储存器的原子读、写、修改和处理器间的同步。

“F” 标准单精度浮点扩展集,增加了浮点寄存器、计算指令、L/S指令。

“D” 标准双精度扩展集,扩展双精度浮点寄存器,双精度计算指令、L/S指令。

I+M+F+A+D 被缩写为 “G” ,共同组成通用的标量指令。

在后续ISA的版本迭代过程中,RV32G和RV64G总是保持不变。

RISC-V指令集架构和X86/ARM相比,一大优势就是支持模块化

RISC-V 指令集架构一改传统增量 ISA 模式,采用模块化 ISA 模式,它被定义为基本的整数指令集架构,以及几个标准的扩展子集,可以自定义指令扩展,如下表所示。

它的核心为RV32I的基础整数指令集,RV32I 是固定的,并保持永远不变,而其扩展是可选择进行实现的。这为编译器、汇编器和操作系统开发人员提供了稳定的研发目标。其扩展包括 M、F、D、A、G、C、V等,开发人员根据实际的应用程序,硬件设计可以选择是否实现这些扩展。这种模块化特性解决了以往指令集增量 ISA 模式和兼容性带来的弊端,并且使得 RISC-V 具有了小型化、低功耗的特点,这对于嵌入式应用至关重要的。

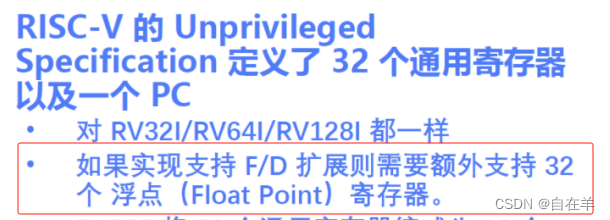

3. RV32I:32个通用寄存器+1个PC寄存器

3.1 通用寄存器的介绍

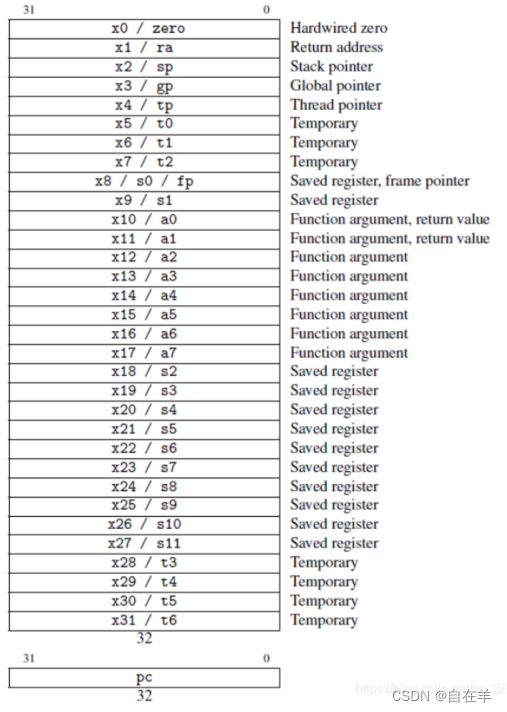

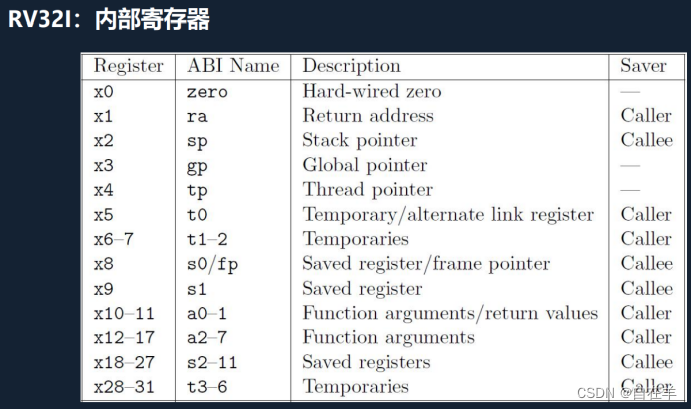

risc-v 有32个通用寄存器(简写 reg),标号为x0 - x31,每个通用寄存器都有各自的用途。

例如 x2是作为sp栈指针、a0 a1用来保存函数参数或返回值。x0寄存器被硬连线为0,就是个0值寄存器。

ABI名称相当于这些通用寄存器的别名,在RISC-V汇编当中,都使用ABI名称来代表这些寄存器。

对于有别名的寄存器,优先使用别名,更达意,更好记。

3.2 为啥通用寄存器只有32个?

寄存器的运算和读取速度是最快的,太少了显然不好,但事实证明,寄存器数目如果太多了会导致访问寄存器的速度下降,也会造成速度下降。32个寄存器是risc-v设计者、实践者的选择。

4. RISCV-CRS寄存器

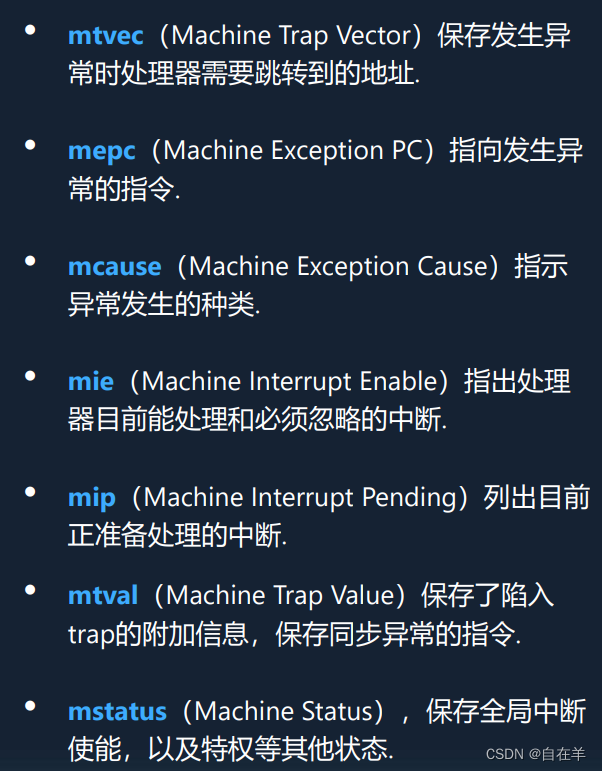

用户级的CSR指令只能访问少数几个只读寄存器。