1、“

Timing Summary Report

”详情

“

Timing Summary Report

”

(

时序汇总报告

)

包含下列部分

:

•

“

General Information

”部分

•

“

Timer Settings

”部分

•

“

Design Timing Summary

”部分

•

“

Clock Summary

”部分

•

“

Methodology Summary

”部分

•

“

Check Timing

”部分

•

“

Intra-Clock Paths

”部分

•

“

Inter-Clock Paths

”部分

•

“

Other Path Groups

”部分

•

“

User-Ignored Paths

”部分

•

“

Unconstrained Paths

”部分

“

Timing Summary Report

”中包含的全面信息类似于

Vivado IDE

中的多项报告

(

时钟交互报告、脉冲宽度报告、时序报告和检查时序)

所提供的信息

,

以及仅限

Tcl

中才可用的某些报告

(

report_clocks

)

。但“

Report Timing Summary”还包含自己特有的信息

,

例如

,

“

Unconstrained Paths

”

(

未约束路径

)

。

2、“

General Information

”部分

“

Timing Summary

”

(

时序汇总

)

报告的“

General Information

”

(

常规信息

)

部分可提供如下内容的相关信息

:

• 设计名称

• 所选器件、封装和速度等级

(

带有速度文件版本

)

•

Vivado Design Suite

版本

• 当前日期

• 为生成报告所执行的等效

Tcl

命令

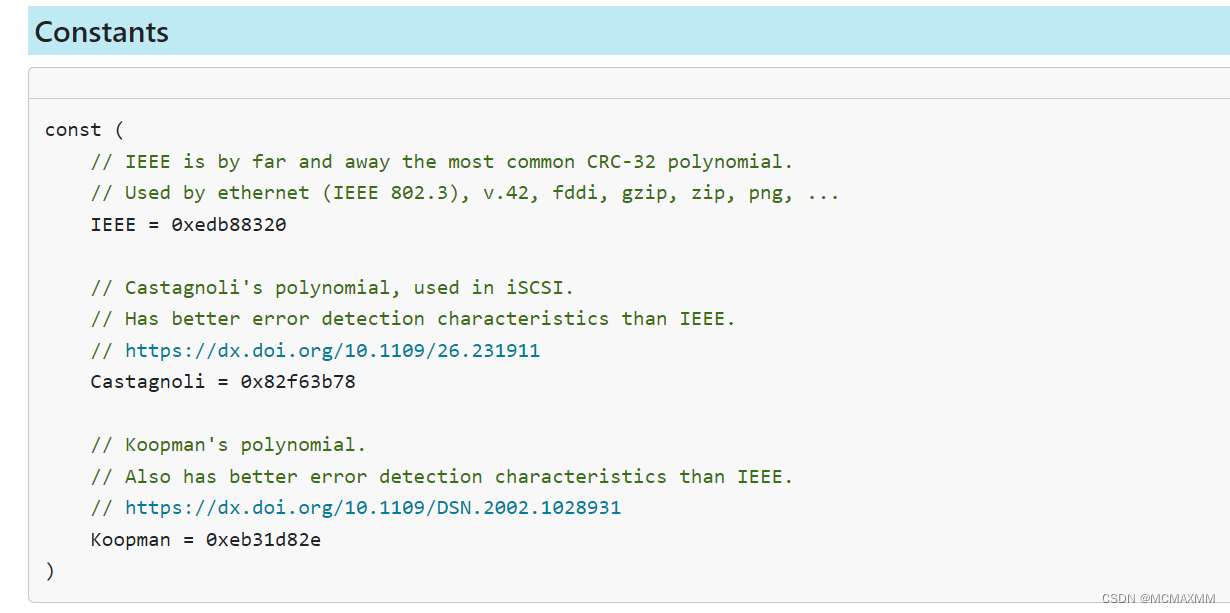

3、“

Timer Settings

”部分

“

Timing Summary

”

(

时序汇总

)

报告的“

Timer Settings

”

(

定时器设置

)

部分包含有关

Vivado IDE

时序分析引擎 设置的详细信息,

这些设置用于在报告中生成时序信息。下图通过示例显示了“

Timer Settings

”部分的默认选项

,

包 括:

• “

Enable Multi-Corner Analysis

”

(

启用多角分析

):

针对每个时序角启用此分析

,

即“

Multi-Corner

Configuration

”

(

多角配置

)

。

• “

Enable Pessimism Removal

”

(

启用消极因素移除

)

和“

Pessimism Removal Resolution

”

(

消极因素移除解决办 法):

确保每条路径的源时钟和目标时钟的报告中均显示其公共节点无偏差。

• “

Enable Input Delay Default Clock

”

(

启用输入延迟默认时钟

):

在无用户约束的输入端口上创建默认空输入延迟约束。默认禁用该选项。

• “

Enable Preset / Clear Arcs

”

(

启用预置

/

清除时序弧

):

启用通过异步管脚进行时序路径传输。默认禁用该选 项,

它不影响恢复

/

移除检查。

• “

Disable Flight Delays

”

(

禁用飞行延迟

):

为

I/O

延迟计算禁用封装延迟。

4、“

Design Timing Summary

”部分

“

Timing Summary

”

(

时序汇总

)

报告的“

Design Timing Summary

”

(

设计时序汇总

)

部分

可提供设

计时序汇总信息

,

并将所有其他部分的结果组合到单一视图内。“Design Timing Summary”部分包含以下内容:

•

“

Setup

”区域

(

最大延迟分析

)

•

“

Hold

”区域

(

最小延迟分析

)

•

“

Pulse Width

”区域

(

管脚开关限制

)

“

Setup

”区域

(

最大延迟分析

)

“

Design Timing Summary

”

(

设计时序汇总

)

部分的“

Setup

”

(

建立时间

)

区域用于显示最大延迟分析相关的所有 检查:

建立、恢复和数据检查。

• “

Worst Negative Slack (WNS)

”

(

最差负时序裕量

):

该值对应于最大延迟分析的所有时序路径的最差裕量。该 值可为正值或负值。

• “

Total Negative Slack (TNS)

”

(

总体负时序裕量

):

所有

WNS

违例的总和

,

前提是仅考量每个时序路径端点的最 差违例。其值为:

0 ns,

前提是针对最大延迟分析满足所有时序约束。

负值,

前提是存在违例。

• “

Number of Failing Endpoints

”

(

故障端点数

):

含违例

(WNS < 0 ns)

的端点总数。

• “

Total Number of Endpoints

”

(

端点总数

):

已分析的端点总数。

“

Hold

”区域

(

最小延迟分析

)

“

Design Timing Summary

”

(

设计时序汇总

)

部分的“

Hold

”

(

保持时间

)

区域用于显示最小延迟分析相关的所有检查:

保持、移除和数据检查。

• “

Worst Hold Slack (WHS)

”

(

最差保持时序裕量

):

对应于最小延迟分析的所有时序路径的最差裕量。该值可为正值或负值。

• “

Total Hold Slack (THS)

”

(

总体保持时序裕量

):

所有

WHS

违例的总和

,

前提是仅考量每个时序路径端点的最差违例。其值为:

0 ns,

前提是针对最小延迟分析满足所有时序约束。 负值,前提是存在违例。

• “

Number of Failing Endpoints

”

(

故障端点数

):

含违例

(WHS < 0 ns)

的端点总数。

• “

Total Number of Endpoints

”

(

端点总数

):

已分析的端点总数。

“

Pulse Width

”区域

(

管脚开关限制

)

“

Design Timing Summary

”

(

设计时序汇总

)

部分的“

Pulse Width

”

(

脉冲宽度

)

区域可显示与管脚开关限制相关的所有检查:

• 最小低脉冲宽度

• 最小高脉冲宽度

• 最小周期

• 最大周期

• 最大偏差

(

例如

,

PCIe

或

GT [

仅限

UltraScale

器件

]

的相同叶节点单元的

2

个时钟管脚之间最大偏差

)

。 报告值为:

• “

Worst Pulse Width Slack (WPWS)

”

(

最差脉冲宽度时序裕量

):

对应于同时使用最小延迟和最大延迟时以上列出的所有时序检查的最差裕量。

• “

Total Pulse Width Slack (TPWS)

”

(

总体脉冲宽度时序裕量

):

仅考量设计中每个管脚的最差违例时

,

所有 WPWS 违例的总和。其值为

:

0 ns,

前提是满足所有相关约束。 负值,前提是存在违例。

• “

Number of Failing Endpoints

”

(

故障端点数

):

含违例

(WPWS < 0 ns)

的管脚总数。

• “

Total Number of Endpoints

”

(

端点总数

):

已分析的端点总数。

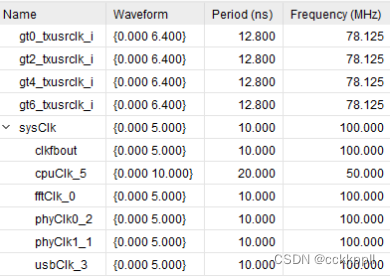

5、“

Clock Summary

”部分

“

Timing Summary

”

(

时序汇总

)

报告的“

Clock Summary

”

(

时钟汇总

)

部分所含信息

report_clocks

所生成的信息相似:

• 设计中的所有时钟

(

包括

create_clock

和

create_generated_clock

创建的时钟以及工具自动创建的时 钟)

。

• 每个时钟的属性

,

如名称、周期、波形和目标频率。

![23111703[含文档+PPT+源码等]计算机毕业设计javaweb商城项目全套电商购物系统](https://img-blog.csdnimg.cn/img_convert/c29addac773c41d1f06f8f8986be6cae.png)