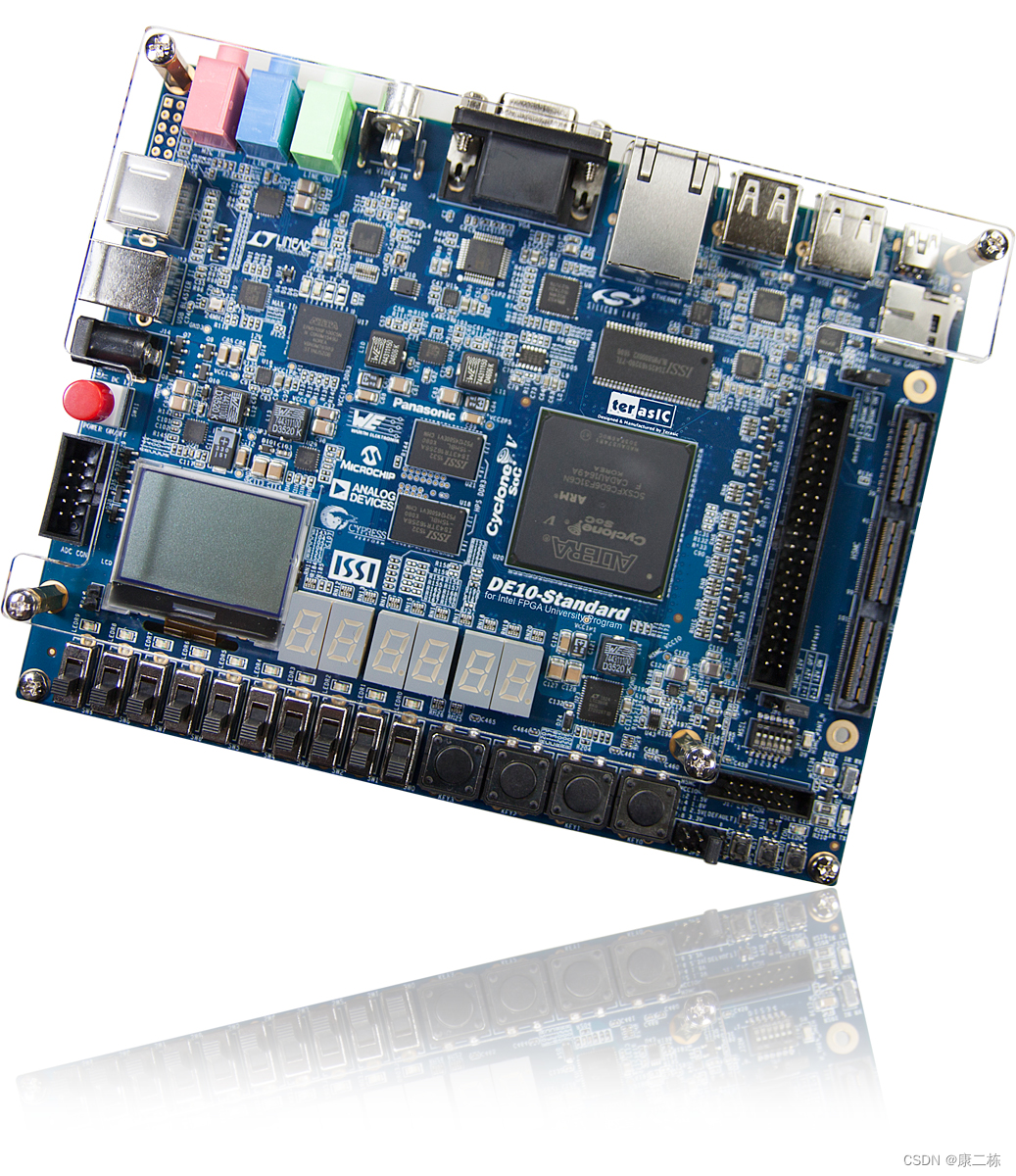

基于DE10-Standard Cyclone V SoC FPGA学习---开发板简介

- 简介

- 产品规格

- 基于 ARM 的 HPS

- 配置与调试

- 存储器件

- 通讯

- 连接头

- 显示器

- 音频

- 视频输入

- 模数转换器

- 开关、按钮、指示器

- 传感器

- 电源

- DE10-Standard 开发板系统框图

- Connect HTG

- 组件配置

- 设计资源

- 其他资源

简介

开发板资料 见 DE10-Standard

DE10-Standard 开发工具包提供了以 Intel System-on-Chip (SoC) FPGA 建立的强大的硬件设计平台,结合了最新的嵌入式双核 Cortex-A9 和业界领先的可编程逻辑以满足终极设计的灵活性。使用者现在可以彻底的利用这个兼具高性能和低功率处理系统的可重构性强大平台。Intel SoC 集成了基于 ARM 的 HPS 架构处理器,周边及内存接口与使用高带宽互联骨干结构的 FPGA 无缝接合。DE10-Standard 开发板包括了诸如高速 DDR3 内存、ADC 功能、以太网络等功能硬件

具体型号为 5CSXFC6D6F31C6N

产品规格

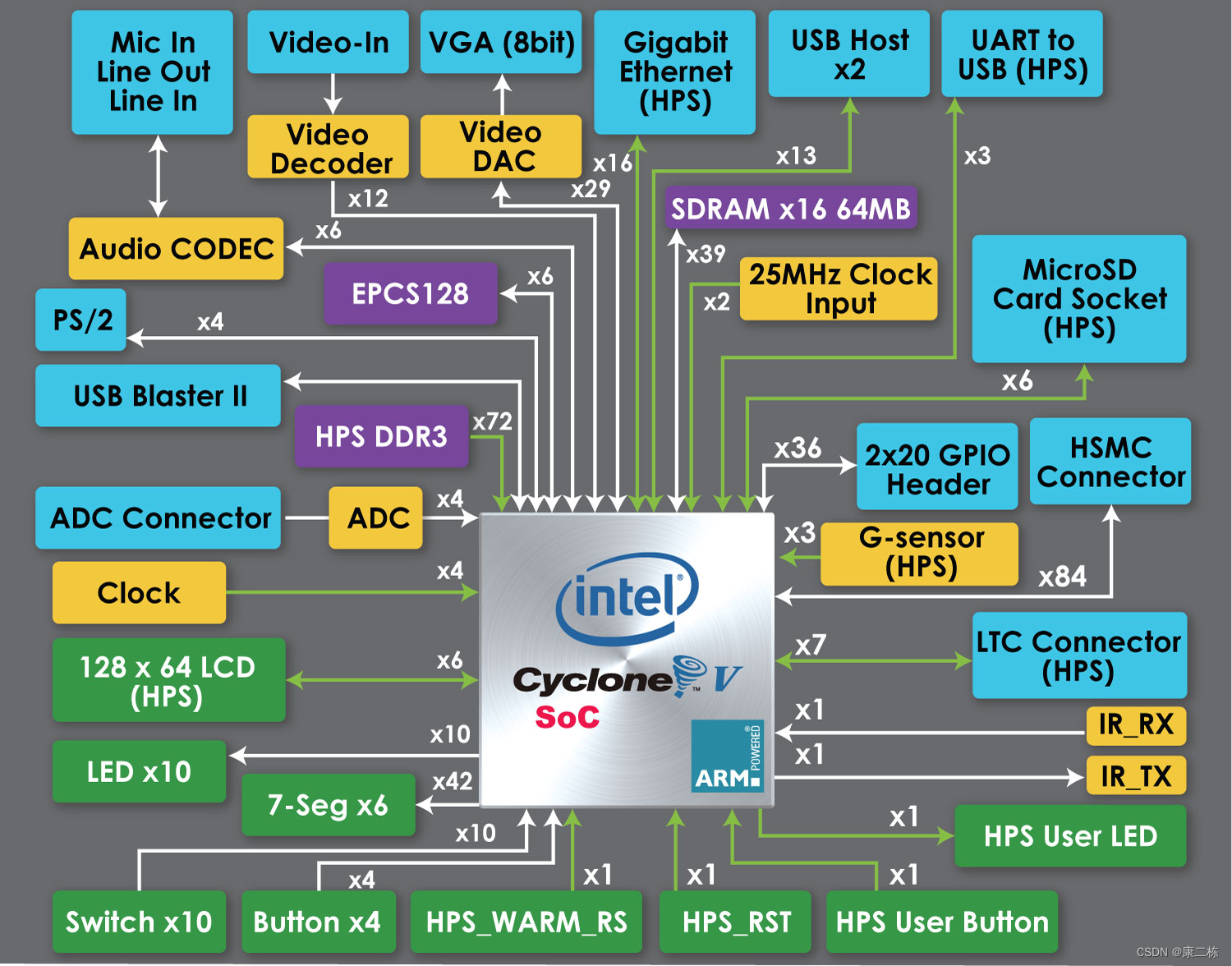

- Cyclone V SX SoC — 5CSXFC6D6F31C6N

- 110,000 个 LE、41,509 个 ALM

- 5,761 Kbits embedded memory

- 6 个 FPGA PLL、3 个 HPS PLL

- 2 个硬件存储控制器

基于 ARM 的 HPS

- 925 MHZ, ARM Cortex-A9 MPCore 双核处理器

- 512 KB 共享 L2 缓存

- 64 KB 可擦写 RAM

- 支持 DDR2、DDR3、LPDDR1 和 LPDDR2 的多埠 SDRAM 控制器

- 8-channel DMA 控制器

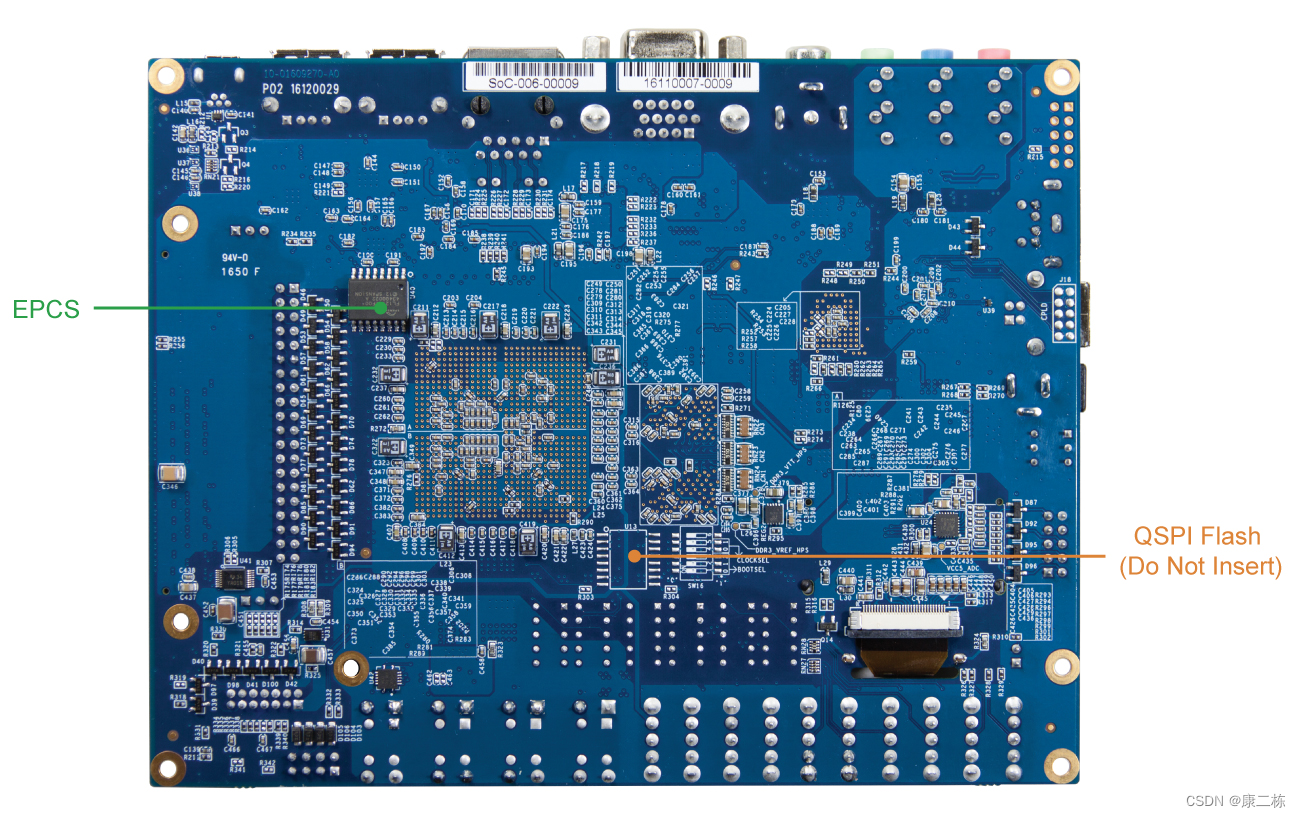

配置与调试

- FPGA 端串行配置晶元 EPCS128

- USB Blaster II,普通 B 型 USB 连接头

存储器件

- FPGA 端 64MB (32Mx16) SDRAM

- HPS 端 1GB (2x256Mx16) DDR3 SDRAM

- HPS 端 Micro SD 卡槽

通讯

- 2 个 USB 2.0 Host 端口 (ULPI 接口配备 USB A 型连接头)

- HPS 端 USB 转 UART(Micro USB B 型连接头)

- HPS 端 10/100/1000 以太网接口

- PS/2 鼠标/键盘连接器

- IR 收发器

连接头

- 1 个 40 引脚扩展界面,电平 3.3V

- 1 个 HSMC 连接头,可配置的 I/O 标准 1.5/1.8/2.5/3.3V

- 1 个 10 引脚 ADC 输入接口

- 1 个 LTC 连接头 ( 1 个 SPI Master,1 个 I2C 和 1 个 GPIO 界面)

显示器

- 24 bit VGA DAC

- HPS 端 128x64 点阵式背光 LCD 显示屏

音频

- 24-bit CODEC,line-in,line-out,microphone插孔

视频输入

- TV 译码器 (NTSC/PAL/SECAM) 和 TV 输入连接头

模数转换器

- 转换速率:500 Ksps

- 8 通道

- 分辨率:12 bits

- 模拟输入范围:0 ~ 4.096 V

开关、按钮、指示器

- 5 个按键 ( 4 个 FPGA, 1个 HPS )

- FPGA 端 10 个开关

- 11 个 LED (FPGA 端 10 个、HPS 端 1 个)

- 2 个 HPS 端重置按钮(HPS_RST_n、HPS_WARM_RST_n)

- 6 个七段数码显示管

传感器

- HPS 端重力传感器

电源

- 12V 直流电源输入

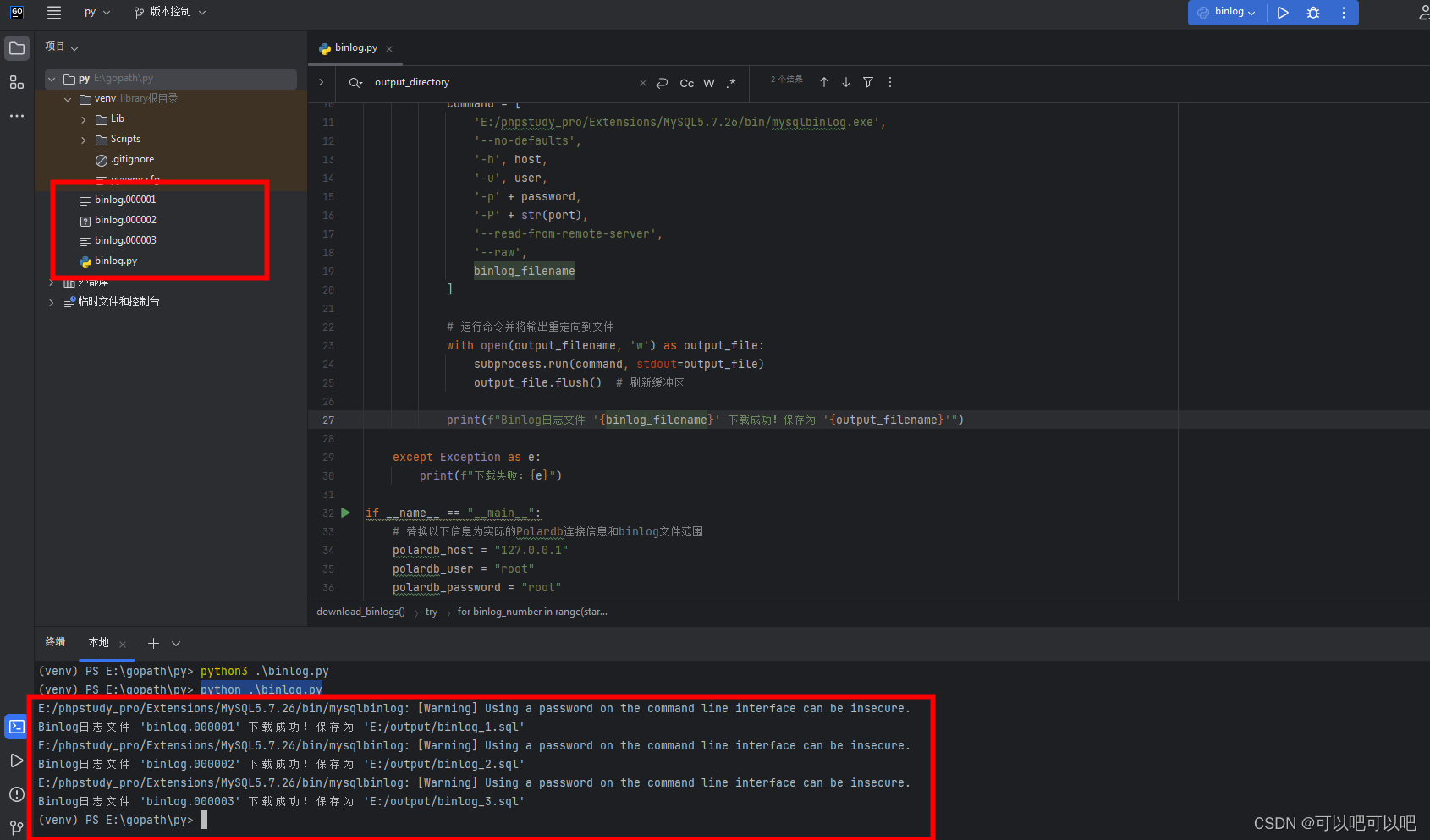

DE10-Standard 开发板系统框图

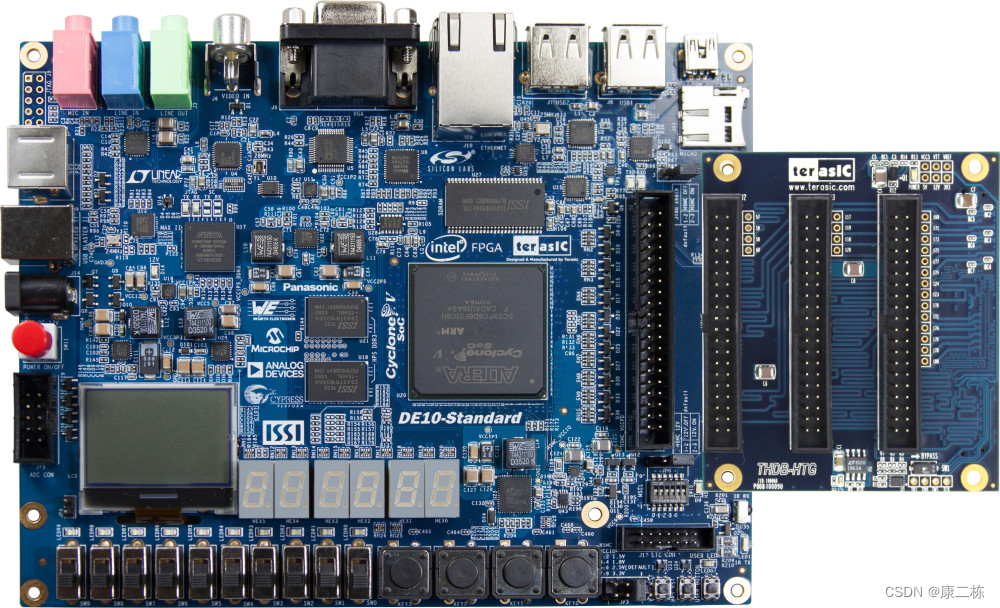

Connect HTG

组件配置

- Size:166*130 mm

设计资源

其他资源

-

DE10-Standard

ECE5760 Advanced Microcontroller Design and system-on-chip [DE2] -

ECE 5760 Simplified Floating Point for DSP [DE2]