晶体管尺寸在3nm时达到临界点,纳米片FET可能会取代finFET来满足性能、功耗、面积和成本目标。同样,正在评估2nm铜互连的重大架构变化,此举将重新配置向晶体管传输电力的方式。

芯片制造商也可能会在2nm节点开始用钌或钼在一定程度上取代铜。其他更温和的变化将使用低电阻通孔工艺、替代衬垫和完全对齐的通孔方法来扩展铜镶嵌互连。

通孔优化

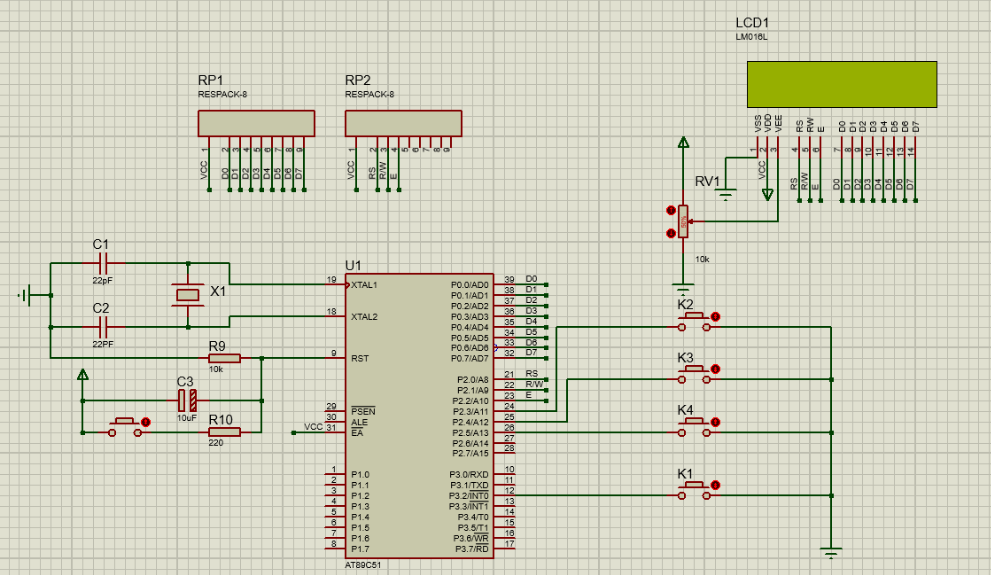

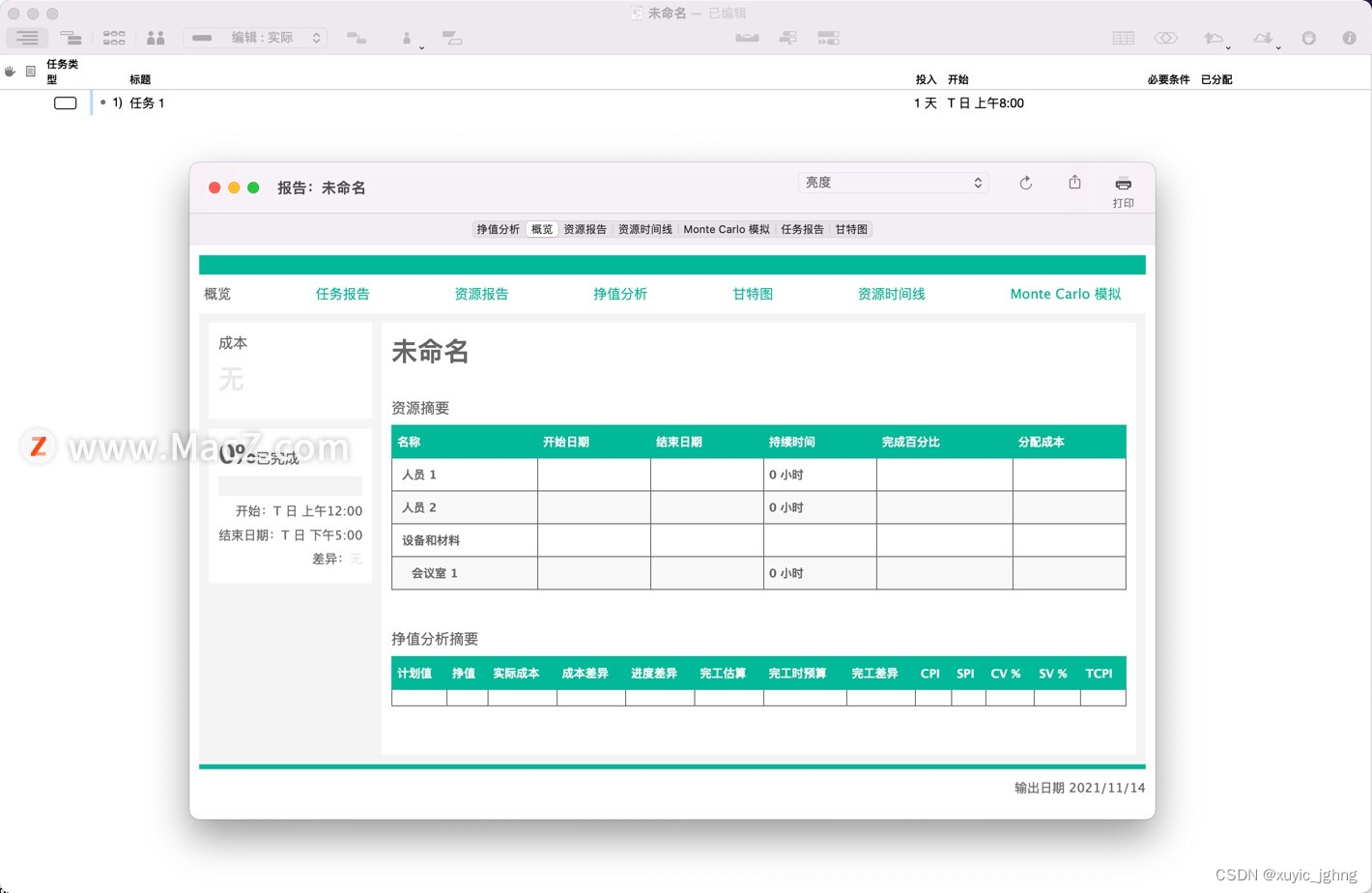

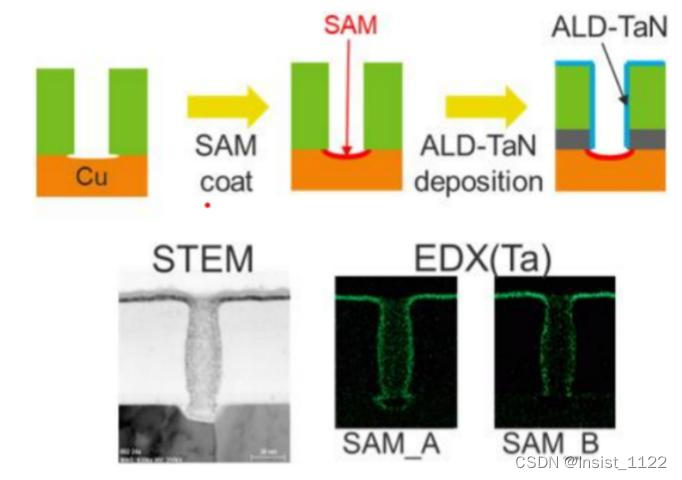

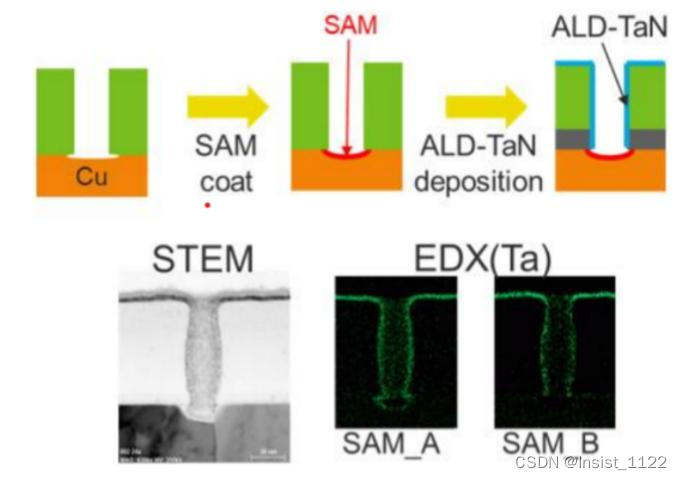

扩展铜技术的一个关键策略是消除铜通孔底部的阻挡金属TaN。实现这一目标的一种方法是选择性沉积自组装单层(SAM)薄膜,通过原子层沉积来沉积TaN(ALD)沿侧壁,去除 SAM并填充铜。在TaN阻挡层ALD之后,蒸发SAM,然后在通孔中进行铜化学沉积(ELD)(图 1)。预填充通孔后,通过CVD在沟槽侧壁上沉积钌衬垫,然后进行铜离子化PVD填充。

另一种减少通孔底部阻挡金属(TaN)体积的策略涉及从PVD TaN到ALD TaN的过渡,这种过渡更加保形,并产生更薄、更连续的薄膜。ALD TaN 预计将在5nm节点上广泛实施,或许采用SAM工艺。

图1

完全对准通孔,选择性沉积

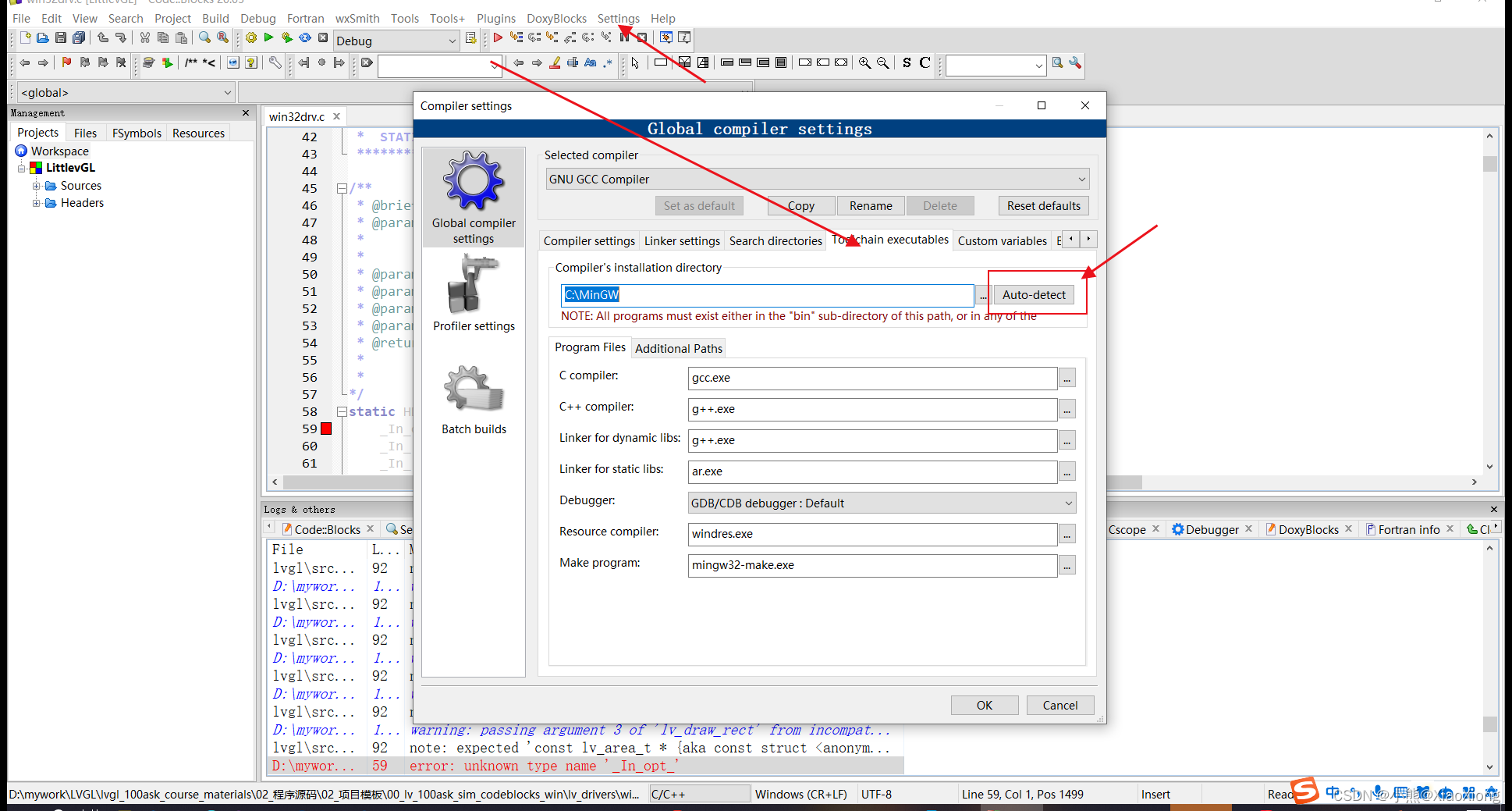

完全对准通孔(FAV)背后的想法是减少通孔和线路之间边缘放置错误的影响,这些错误会导致器件故障和长期可靠性问题。自32nm节点以来,一直采用自对准方法,使用TiN硬掩模将互连对齐到以下水平。在完全对齐的通孔中,下方和上方的通孔被注册。有两种方法可以实现 FAV:从下面的线路蚀刻一些铜,然后图案化并沉积通孔,或者通过在低 k 电介质上选择性地沉积电介质薄膜,然后进行通孔图案化。

凹槽蚀刻与蚀刻选择性介电盖结合使用时,可充当通孔引导图案,从而减轻覆盖和临界尺寸(CD)引起的边缘放置错误。通过CVD在低k材料上沉积选择性氧化铝薄膜,并充当部分蚀刻停止层。该工艺成功的关键是高选择性,介电薄膜的横向过度生长有限,并且与标准FAV工艺相比,电阻没有降低或变化。

图2

埋置电源轨

BPR和背面配电(BPD)的组合本质上采用电源线和地线,这些线之前是通过整个多层金属互连布线的,并在晶圆背面为它们提供了专用网络。通过将电源布线到背面,那里将会有很高、相对较宽的互连,而前面的信号和时钟则带有相对较细的电阻线,并且可以显着获得布线能力。

虽然这种在晶圆正面和背面建立晶体管接入的转变将需要许多工艺和设计创新,但背面电源仍将采用平面逐层结构这一事实建立在现有行业技术的基础上。

从晶圆减薄的角度来看,HBM存储器的多芯片堆叠和现在逻辑的背面供电都推动晶圆减薄至10微米,但人们对变薄有着巨大的兴趣。高密度堆叠正在推动这一需求,设计人员想要比目前可用的硅更薄的硅。从需要某些东西的那一刻起,技术人员就会扩展功能,这就是芯片堆叠所发生的情况。

结论

目前,正在评估5nm及以上工艺的许多工艺变化,包括通孔电阻优化、完全对齐的通孔、钴帽和触点,以及电源线和信号线的分离以释放拥挤的互连层。半导体行业总是更愿意尽可能地进行渐进的工艺修改,而不是大规模的材料和结构变化。

新的衬垫可以提高可靠性,消除通孔底部的障碍并完全对齐通孔,似乎正在提供解决方案。选择性沉积已进入钴帽工厂,并且可能会在未来的其他应用中获得接受。