1.SSD基础知识

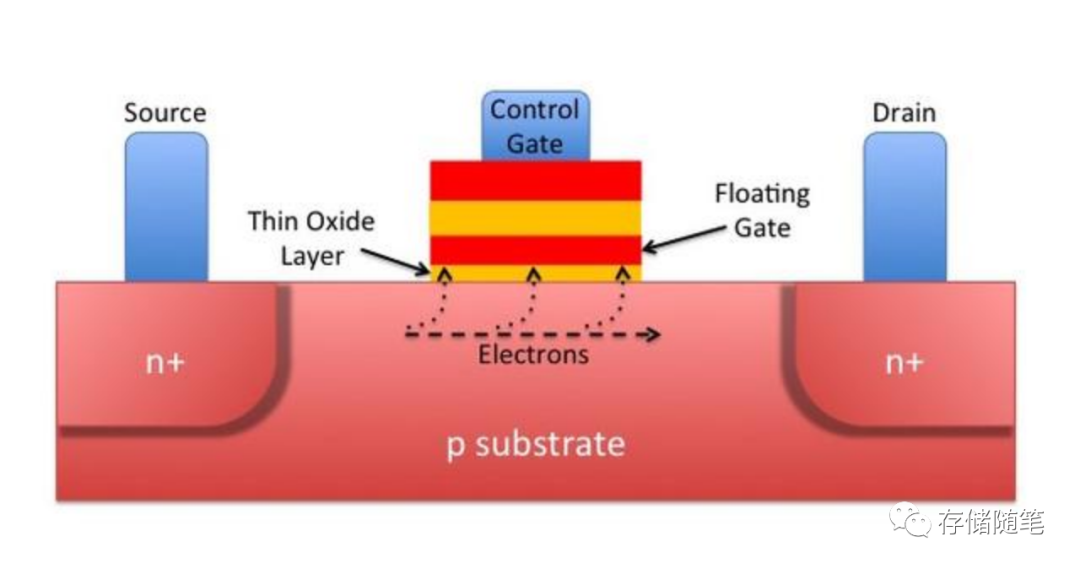

SSD的存储介质是什么,它就是NAND闪存。那你知道NAND闪存是怎么工作的吗?其实,它就是由很多个晶体管组成的。这些晶体管里面存储着电荷,代表着我们的二进制数据,要么是“0”,要么是“1”。NAND闪存原理上是一个CMOS管,有两个栅极,一个是控制栅极(Control Gate), 一个是浮栅(Floating Gate). 浮栅的作用就是存储电荷,而浮栅与沟道之间的氧化层(Oxide Layer)的好坏决定着浮栅存储电荷的可靠性,也就是NAND闪存的寿命。

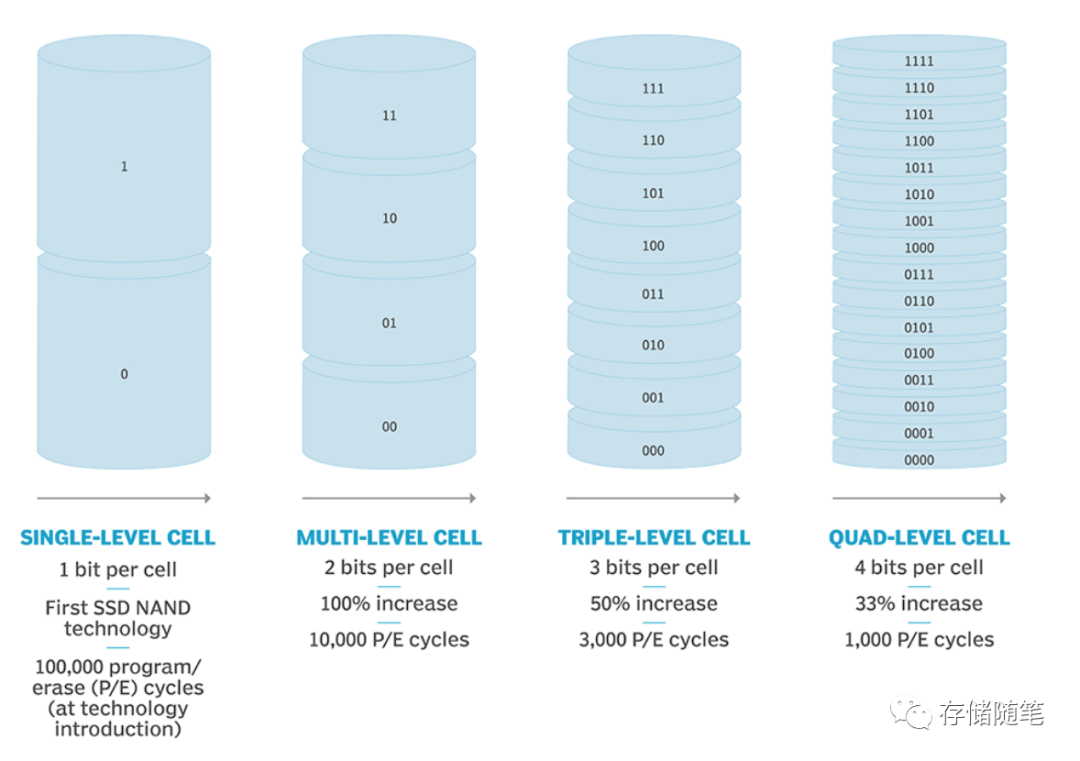

目前市面上主要流通的就是4种NAND类型:SLC、MLC、TLC、QLC。随着每个寿命从高到低依次是SLC>MLC>TLC>QLC.

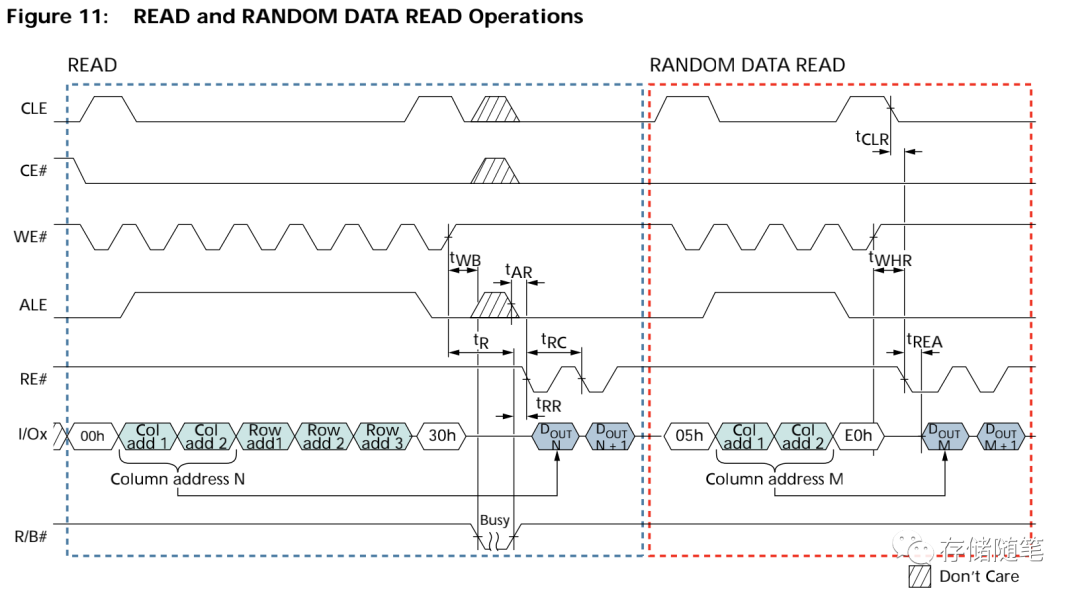

Host从SSD读数据,最终数据的来源也是要从NAND die上读取,对NAND die发送Read Page操作,数据返回。这个过程的耗时直接决定了SSD读性能的好坏。下图是某个比较老的NAND SPEC相关读操作的示意图,仅供参考。

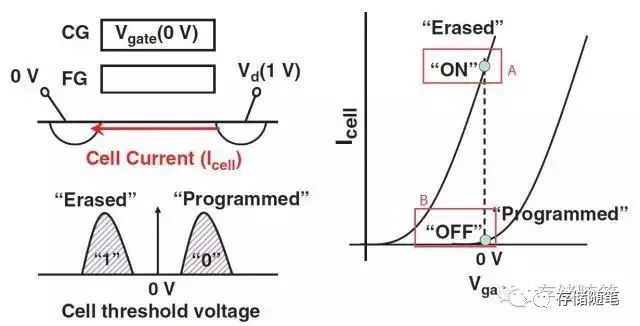

NAND Page Read实现的基本原理如下:

如上图所示,这是对单一cell进行read的基本操作。在控制栅极(CG, 也是WL)加上0V的电压,源极(Source)端加上0V以及漏极(Drain, 也是BL)加上1V,然后通过源极与漏极之间电流Icell的大小来判断cell的状态(0或者1)。

-

A点的状态代表存在Icell,所以Cell处于“开态”(ON),称为Erased;

-

B点的状态代表不存在Icell或者Icell很小且可忽略,所以Cell处于“关态”(OFF),称为Programmed。

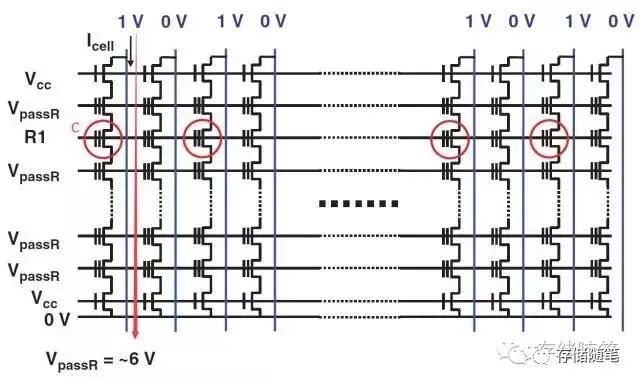

如果对NAND cell阵列操作,原理图如下:

在需要read的target Page的WL上面加一个R1(一个较小的电压),其他WL的加VpassR, BL方向加1V,

-

如果Cell C处于Erased, 对应BL的Sense电路会感应到有电流;

-

如果Cell C处于Programmed, 对应BL的Sense电路不会感应到有电流。

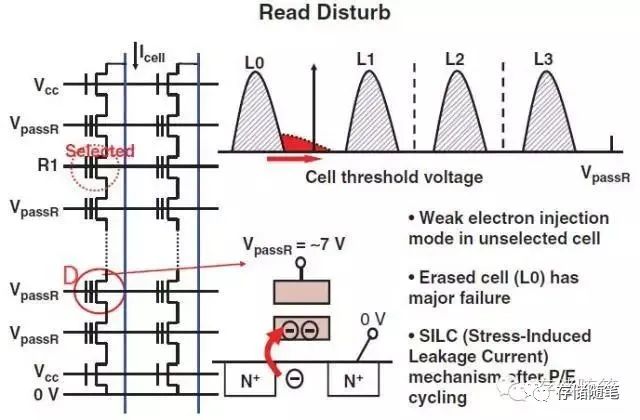

如前面讲述,Read过程中,需要在Non-Target WL上加一个VpassR, 如果对一个Block里面的Page连续Read很多次的话,就相当于在某一WL一直会有VpassR的Stress。

如下图,Cell D 由于VpassR长时间的Stress, 会引起浮栅FG弱的电子注入,因为Read disturb主要影响Erased状态的cell,进而表现在Vt图中L0向右飘移。

在SSD中,针对Read disturb有优化措施,就是尽量避免持续读同一Block的Page,如果在进行了长时间的读操作之后,会加入Erase/Program操作,减小Read stress。这个为防止读干扰的数据搬迁动作也性能有一定的影响,

2.Vpass对读干扰与性能的影响

近期小编在查阅Vpass相关资料的时候,翻阅到了华东师范大学石亮教授团队于2017年发表的一篇关于Vpass的论文,思路挺好的,这里节选核心的内容分享给大家。详细论文获取链接,公众号后台回复关键字【Vpass论文】即可。

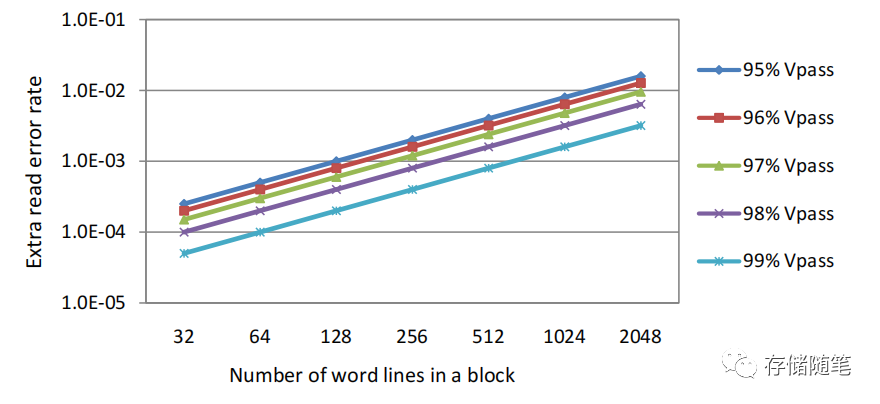

从读干扰的原理来看,如果同一个block内的wordline被读的次数越多,那么读干扰的影响将越大。随着3D NAND的堆叠发展,单个block的容量越来越大,那么单个block的Read Count也会相应的不断升高,呈现了指数级别的增长。3D NAND读干扰的问题,比之前2D NAND更加严重。

之前有研究表明,拉低Vpass电压可以有效降低读干扰的发生。但是,也会造成另外一个问题,也可能会产生额外的读错误。

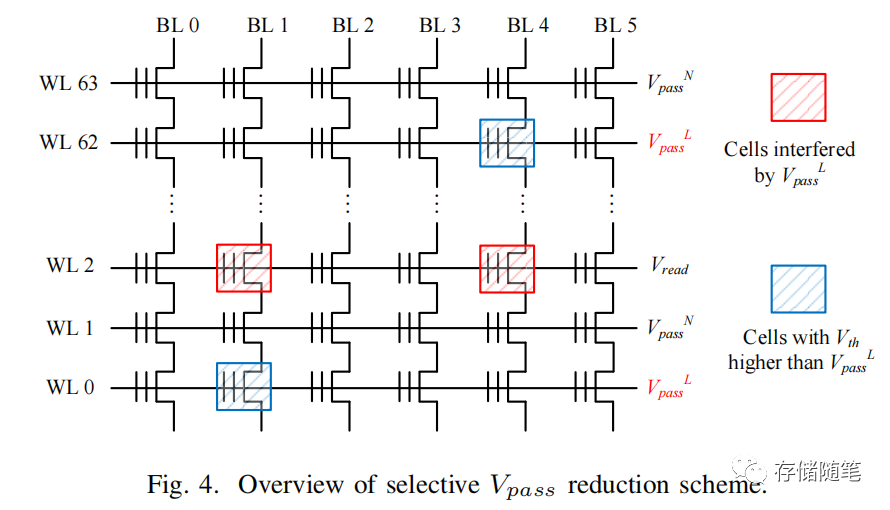

论文中,提出一种选择特定的wordline施加低电压Vpass的方案。比如下图示例WL2正在进行Read操作,在WL0/WL62施加了低VpassL。这样的话,就降低了WL0/WL62的读干扰,同时会对WL2产生额外的读错误也会显著降低。

接下来,核心问题是,如何选择哪些WL施加低电压VpassL?

为了解决这个问题,论文中提出了2个核心点:

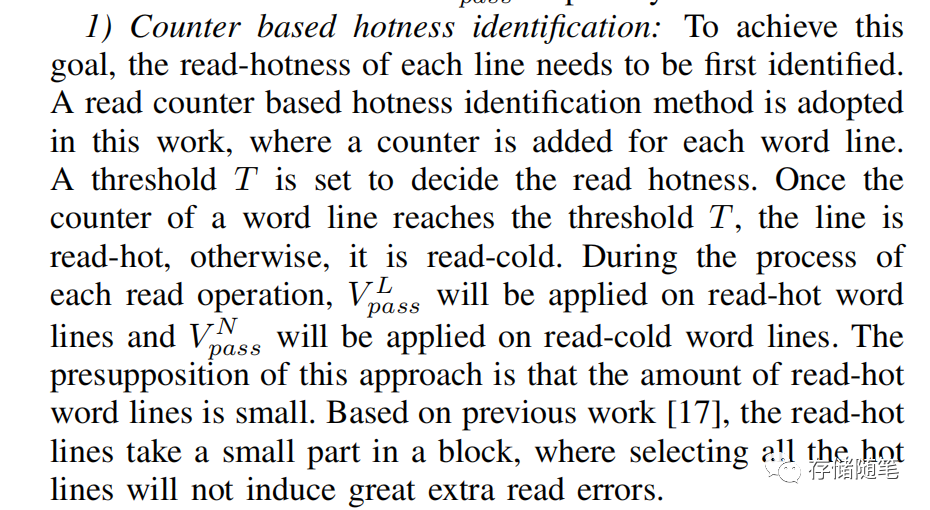

1.给每个Wordline增加了一个热点计数器

通过读热点与阈值T比较:

-

低于T,属于冷数据,施加正常VpassN;

-

大于等于T,属于热数据,施加低电压VpassL。

2.结合LDPC RBER和热点访问综合判断

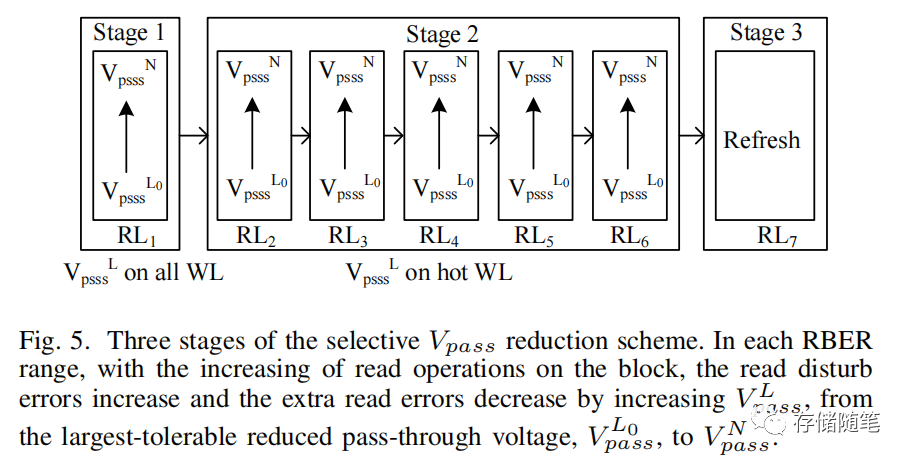

LDPC有7个level感应电压,对应7个RBER范围。论文中将LDPC的7个level分为3组:

-

Stage1: Read Level 1,这个阶段,读错误最小,所有的wordline都施加低电压VpassL。

-

Stage2: Read Level 2-6,这个阶段,读错误有所增加,只针对热点读wordline施加低电压VpassL

-

Stage3: Read Level 7,这个阶段读干扰导致的错误已经很严重了,需要执行数据搬迁动作。

在Stage1和Stage2,论文中还设置一个参数,Page read的延迟参数F,如果下次读的延迟增加,则选择升高VpassL电压,从VpassL0可以逐渐升高到正常电压VpassN。

大家看完上面两个步骤,是不是觉得很复杂。的确是,我们就需要考虑到,上面两个策略增加了FW设计复杂性(决策热点数据)和硬件复杂性(电路实现不同的Vpass),同时增加了额外的开销。以单个block(包含1024 pages,单个page大小4KB)为例:

-

记录Stage:需要1bit

-

记录6个VpassL:需要3bit

-

记录7个读延迟基准:需要3bit

-

记录热点阈值:需要2bit

这样来计算,对于512GB的die,就需要8MB的额外存储空间。

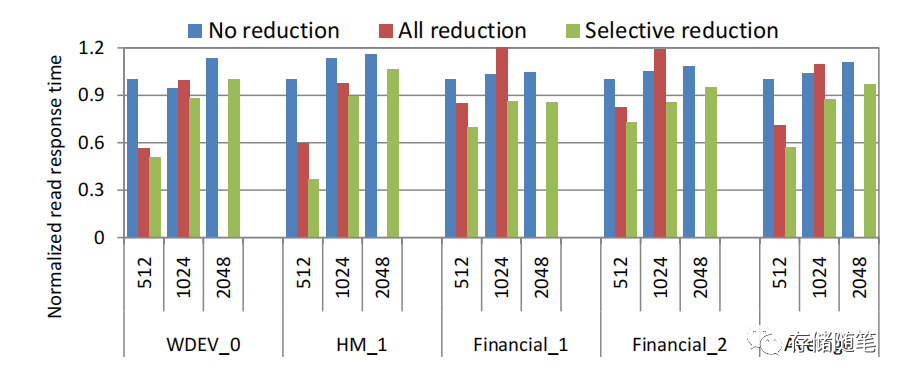

最后的模拟效果如何呢?

-

对于单个block 512 WLs:选择性降低Vpass的方案可以有效降低读延迟,提升读性能。

-

对于单个block 1024 WLs:全部降低Vpass的方案,由于产生了额外的读错误数据,还会导致性能下降。

-

对于单个block 2048 WLs: 全部降低Vpass的方案完全就不能工作了,因为产生的额外错误太多,超过了ECC纠错能力。

-

从平均数据来看,论文提出的“选择性降低Vpass”的策略可以有效提升20%读性能。