我将uart_done(出问题的信号)的变量类型设为reg了,也就是我是reg uart_done这个信号的,这样做是错误的,哪怕你在接收模块确实定义的是reg类型,但是在顶层模块的时候,它可以视为是一条单纯的线而已,所以应该用wire,

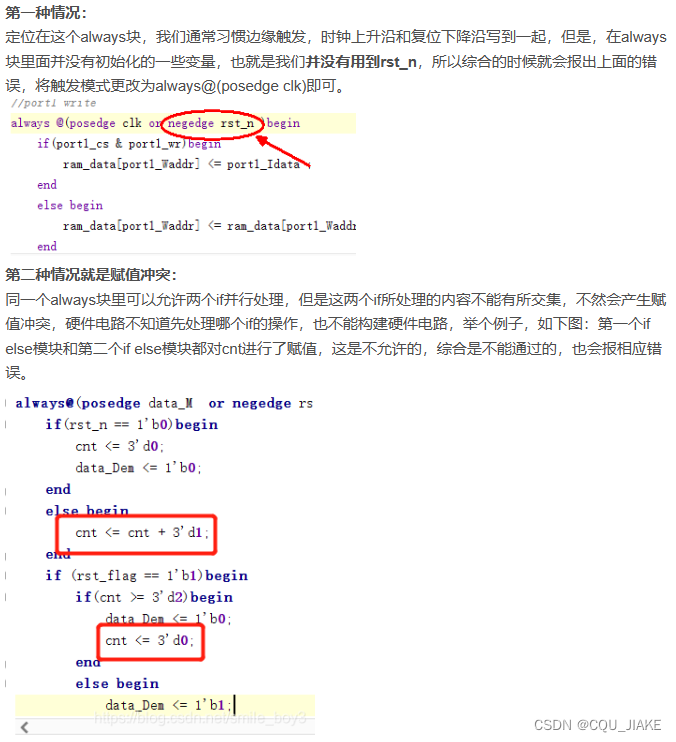

Vivado综合时出现[Synth 8-91] ambiguous clock in event control

操作复位时,必须要保持读使能开关打开,不然复位后依然显示的上一个数

我将uart_done(出问题的信号)的变量类型设为reg了,也就是我是reg uart_done这个信号的,这样做是错误的,哪怕你在接收模块确实定义的是reg类型,但是在顶层模块的时候,它可以视为是一条单纯的线而已,所以应该用wire,

操作复位时,必须要保持读使能开关打开,不然复位后依然显示的上一个数

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1185789.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!