PCIe寄存器信息读取、分析、配置

- 1.获取bdf (bus:device.function)地址

- 2.根据bdf地址抓取pci信息

- 3.结合PCIe Spec对读到的信息进行分析

- 使用setpci修改

1.获取bdf (bus:device.function)地址

在Linux系统下使用命令:

ls -l /sys/block | grep nvme 可以得到nvme硬盘的bdf地址:其中 0000:00:02.1为root port

0000:01:00.0为 endpoint,我们下面使用setpci时会需要涉及到

lrwxrwxrwx. 1 root root 0 Nov 4 15:25 nvme0n1 -> ../devices/pci0000:00/0000:00:02.1/0000:01:00.0/nvme/nvme0/nvme0n1

2.根据bdf地址抓取pci信息

使用lspci -vvvxxx -s $bdf 可以抓取pci寄存器的讯息

我的电脑下抓到的信息如下:

硬盘的bdf:

[root@localhost ~]# lspci -vvvxxx -s 01:00.0

01:00.0 Non-Volatile memory controller: Samsung Electronics Co Ltd NVMe SSD Controller SM981/PM981/PM983 (prog-if 02 [NVM Express])

Subsystem: Samsung Electronics Co Ltd Device a801

Control: I/O- Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx+

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 64 bytes

Interrupt: pin A routed to IRQ 48

NUMA node: 0

Region 0: Memory at c0800000 (64-bit, non-prefetchable) [size=16K]

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0-,D1-,D2-,D3hot-,D3cold-)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [50] MSI: Enable- Count=1/32 Maskable- 64bit+

Address: 0000000000000000 Data: 0000

Capabilities: [70] Express (v2) Endpoint, MSI 00

DevCap: MaxPayload 256 bytes, PhantFunc 0, Latency L0s unlimited, L1 unlimited

ExtTag- AttnBtn- AttnInd- PwrInd- RBE+ FLReset+ SlotPowerLimit 0.000W

DevCtl: Report errors: Correctable+ Non-Fatal+ Fatal+ Unsupported+

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+ FLReset-

MaxPayload 256 bytes, MaxReadReq 512 bytes

DevSta: CorrErr- UncorrErr- FatalErr- UnsuppReq- AuxPwr- TransPend-

LnkCap: Port #0, Speed 8GT/s, Width x4, ASPM L1, Exit Latency L0s unlimited, L1 <64us

ClockPM+ Surprise- LLActRep- BwNot- ASPMOptComp+

LnkCtl: ASPM L1 Enabled; RCB 64 bytes Disabled- CommClk+

ExtSynch- ClockPM+ AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 8GT/s, Width x4, TrErr- Train- SlotClk+ DLActive- BWMgmt- ABWMgmt-

DevCap2: Completion Timeout: Range ABCD, TimeoutDis+, LTR+, OBFF Not Supported

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR+, OBFF Disabled

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete+, EqualizationPhase1+

EqualizationPhase2+, EqualizationPhase3+, LinkEqualizationRequest-

Capabilities: [b0] MSI-X: Enable+ Count=33 Masked-

Vector table: BAR=0 offset=00003000

PBA: BAR=0 offset=00002000

Capabilities: [100 v2] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr-

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr+

AERCap: First Error Pointer: 00, GenCap+ CGenEn- ChkCap+ ChkEn-

Capabilities: [148 v1] Device Serial Number 00-00-00-00-00-00-00-00

Capabilities: [158 v1] Power Budgeting <?>

Capabilities: [168 v1] #19

Capabilities: [188 v1] Latency Tolerance Reporting

Max snoop latency: 1048576ns

Max no snoop latency: 1048576ns

Capabilities: [190 v1] L1 PM Substates

L1SubCap: PCI-PM_L1.2+ PCI-PM_L1.1+ ASPM_L1.2+ ASPM_L1.1+ L1_PM_Substates+

PortCommonModeRestoreTime=10us PortTPowerOnTime=10us

Kernel driver in use: nvme

Kernel modules: nvme

00: 4d 14 08 a8 06 04 10 00 00 02 08 01 10 00 00 00

10: 04 00 80 c0 00 00 00 00 00 00 00 00 00 00 00 00

20: 00 00 00 00 00 00 00 00 00 00 00 00 4d 14 01 a8

30: 00 00 00 00 40 00 00 00 00 00 00 00 04 01 00 00

40: 01 50 03 00 08 00 00 00 00 00 00 00 00 00 00 00

50: 05 70 8a 00 00 00 00 00 00 00 00 00 00 00 00 00

60: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

70: 10 b0 02 00 c1 8f 00 10 3f 28 00 00 43 78 47 00

80: 42 01 43 10 00 00 00 00 00 00 00 00 00 00 00 00

90: 00 00 00 00 1f 08 00 00 00 04 00 00 0e 00 00 00

a0: 03 00 1f 00 00 00 00 00 00 00 00 00 00 00 00 00

b0: 11 00 20 80 00 30 00 00 00 20 00 00 00 00 00 00

c0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

d0: 03 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

root port端的信息:

[root@localhost ~]# lspci -vvvxxx -s 00:02.1

00:02.1 PCI bridge: Advanced Micro Devices, Inc. [AMD] Renoir PCIe GPP Bridge (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx+

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 64 bytes

Interrupt: pin ? routed to IRQ 26

Bus: primary=00, secondary=01, subordinate=01, sec-latency=0

I/O behind bridge: 0000f000-00000fff

Memory behind bridge: c0800000-c08fffff

Prefetchable memory behind bridge: 00000000fff00000-00000000000fffff

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR- NoISA- VGA- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [50] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst- PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [58] Express (v2) Root Port (Slot+), MSI 00

DevCap: MaxPayload 512 bytes, PhantFunc 0

ExtTag+ RBE+

DevCtl: Report errors: Correctable- Non-Fatal- Fatal- Unsupported-

RlxdOrd+ ExtTag+ PhantFunc- AuxPwr- NoSnoop+

MaxPayload 256 bytes, MaxReadReq 512 bytes

DevSta: CorrErr- UncorrErr- FatalErr- UnsuppReq- AuxPwr- TransPend-

LnkCap: Port #1, Speed 8GT/s, Width x4, ASPM L1, Exit Latency L0s unlimited, L1 <64us

ClockPM- Surprise- LLActRep+ BwNot+ ASPMOptComp+

LnkCtl: ASPM L1 Enabled; RCB 64 bytes Disabled- CommClk+

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 8GT/s, Width x4, TrErr- Train- SlotClk+ DLActive+ BWMgmt+ ABWMgmt-

SltCap: AttnBtn- PwrCtrl- MRL- AttnInd- PwrInd- HotPlug- Surprise-

Slot #0, PowerLimit 0.000W; Interlock- NoCompl+

SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-

Control: AttnInd Unknown, PwrInd Unknown, Power- Interlock-

SltSta: Status: AttnBtn- PowerFlt- MRL- CmdCplt- PresDet+ Interlock-

Changed: MRL- PresDet- LinkState+

RootCtl: ErrCorrectable- ErrNon-Fatal- ErrFatal- PMEIntEna+ CRSVisible+

RootCap: CRSVisible+

RootSta: PME ReqID 0000, PMEStatus- PMEPending-

DevCap2: Completion Timeout: Range ABCD, TimeoutDis+, LTR+, OBFF Not Supported ARIFwd+

DevCtl2: Completion Timeout: 65ms to 210ms, TimeoutDis-, LTR+, OBFF Disabled ARIFwd-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete+, EqualizationPhase1+

EqualizationPhase2+, EqualizationPhase3+, LinkEqualizationRequest-

Capabilities: [a0] MSI: Enable+ Count=1/1 Maskable- 64bit+

Address: 00000000fee00000 Data: 0000

Capabilities: [c0] Subsystem: Advanced Micro Devices, Inc. [AMD] Device 1453

Capabilities: [c8] HyperTransport: MSI Mapping Enable+ Fixed+

Capabilities: [100 v1] Vendor Specific Information: ID=0001 Rev=1 Len=010 <?>

Capabilities: [270 v1] #19

Capabilities: [2a0 v1] Access Control Services

ACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl- DirectTrans+

ACSCtl: SrcValid+ TransBlk- ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl- DirectTrans-

Capabilities: [370 v1] L1 PM Substates

L1SubCap: PCI-PM_L1.2+ PCI-PM_L1.1+ ASPM_L1.2+ ASPM_L1.1+ L1_PM_Substates+

PortCommonModeRestoreTime=10us PortTPowerOnTime=150us

Capabilities: [380 v1] Downstream Port Containment

DpcCap: INT Msg #0, RPExt+ PoisonedTLP+ SwTrigger+ RP PIO Log 6, DL_ActiveErr+

DpcCtl: Trigger:0 Cmpl- INT- ErrCor- PoisonedTLP- SwTrigger- DL_ActiveErr-

DpcSta: Trigger- Reason:00 INT- RPBusy- TriggerExt:00 RP PIO ErrPtr:1f

Source: 0000

Capabilities: [400 v1] #25

Capabilities: [410 v1] #26

Capabilities: [440 v1] #27

Kernel driver in use: pcieport

00: 22 10 34 16 07 04 10 00 00 00 04 06 10 00 81 00

10: 00 00 00 00 00 00 00 00 00 01 01 00 f1 01 00 00

20: 80 c0 80 c0 f1 ff 01 00 00 00 00 00 00 00 00 00

30: 00 00 00 00 50 00 00 00 00 00 00 00 ff 00 00 00

40: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

50: 01 58 03 c8 00 00 00 00 10 a0 42 01 22 80 00 00

60: 30 29 00 00 43 78 73 01 42 00 43 70 00 00 04 00

70: 00 00 40 01 18 00 01 00 00 00 00 00 bf 19 70 00

80: 06 04 00 00 0e 00 00 00 03 00 1f 00 00 00 00 00

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

a0: 05 c0 81 00 00 00 e0 fe 00 00 00 00 00 00 00 00

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

c0: 0d c8 00 00 22 10 53 14 08 00 03 a8 00 00 00 00

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

e0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

f0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

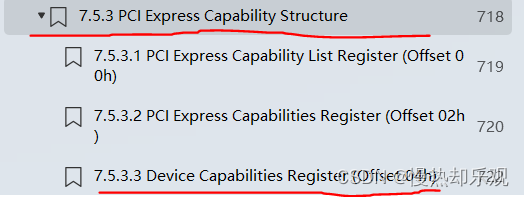

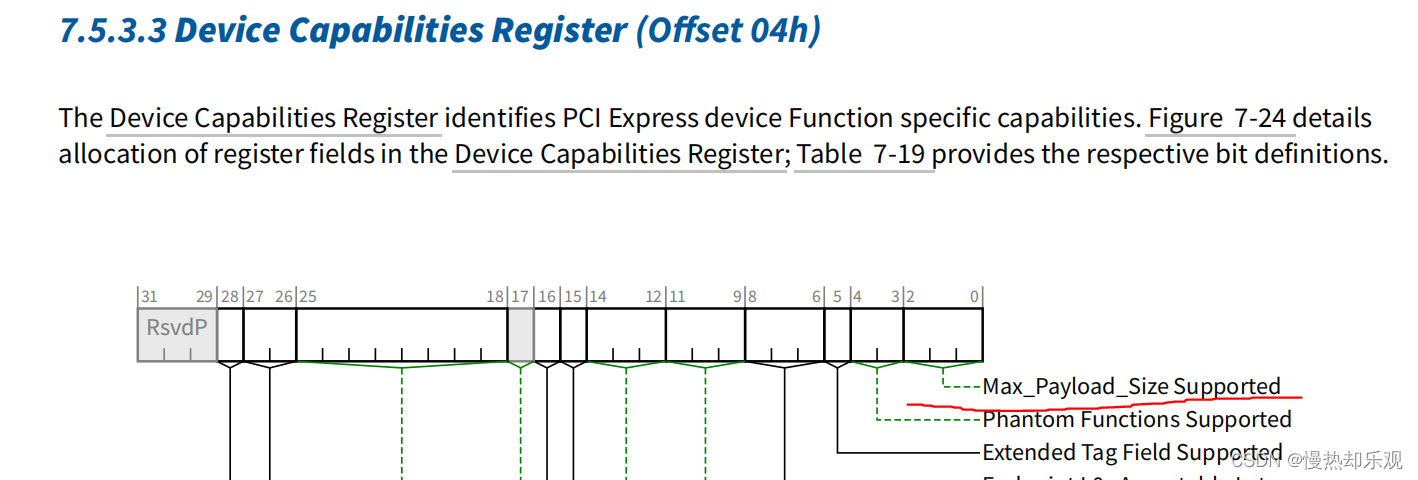

3.结合PCIe Spec对读到的信息进行分析

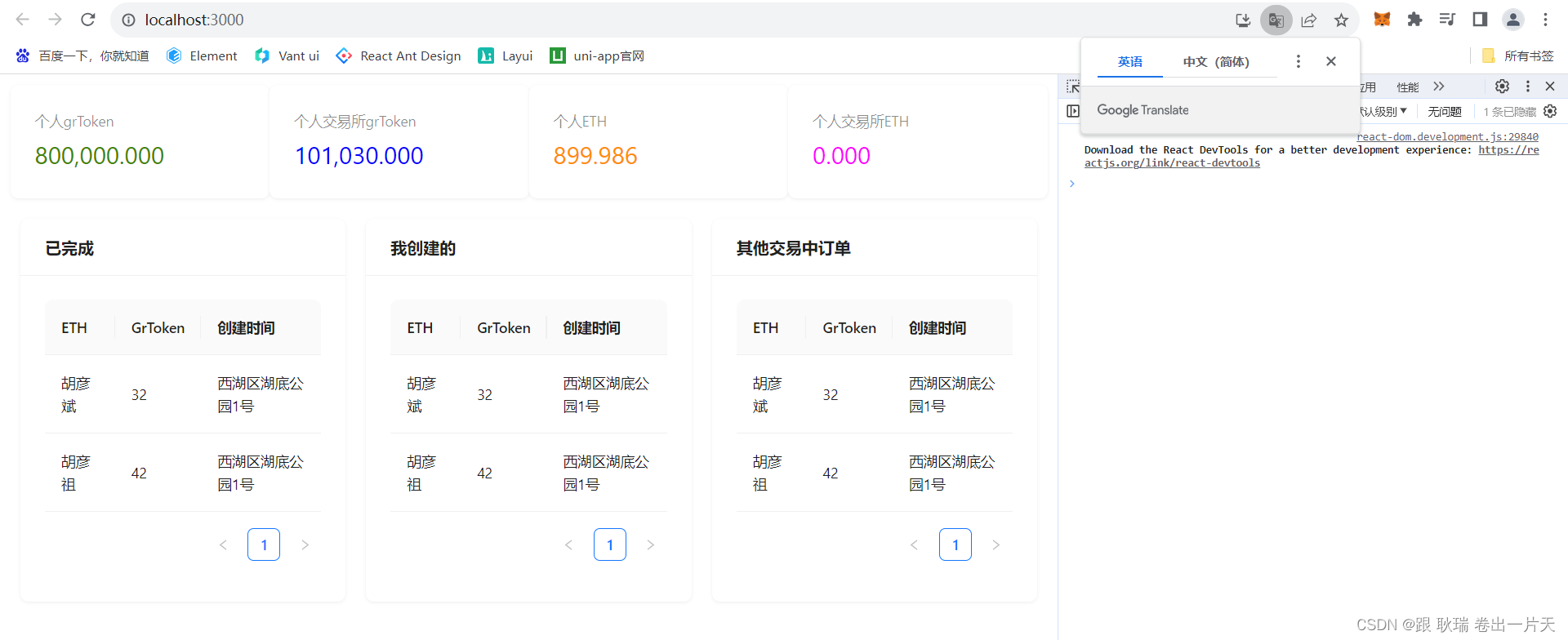

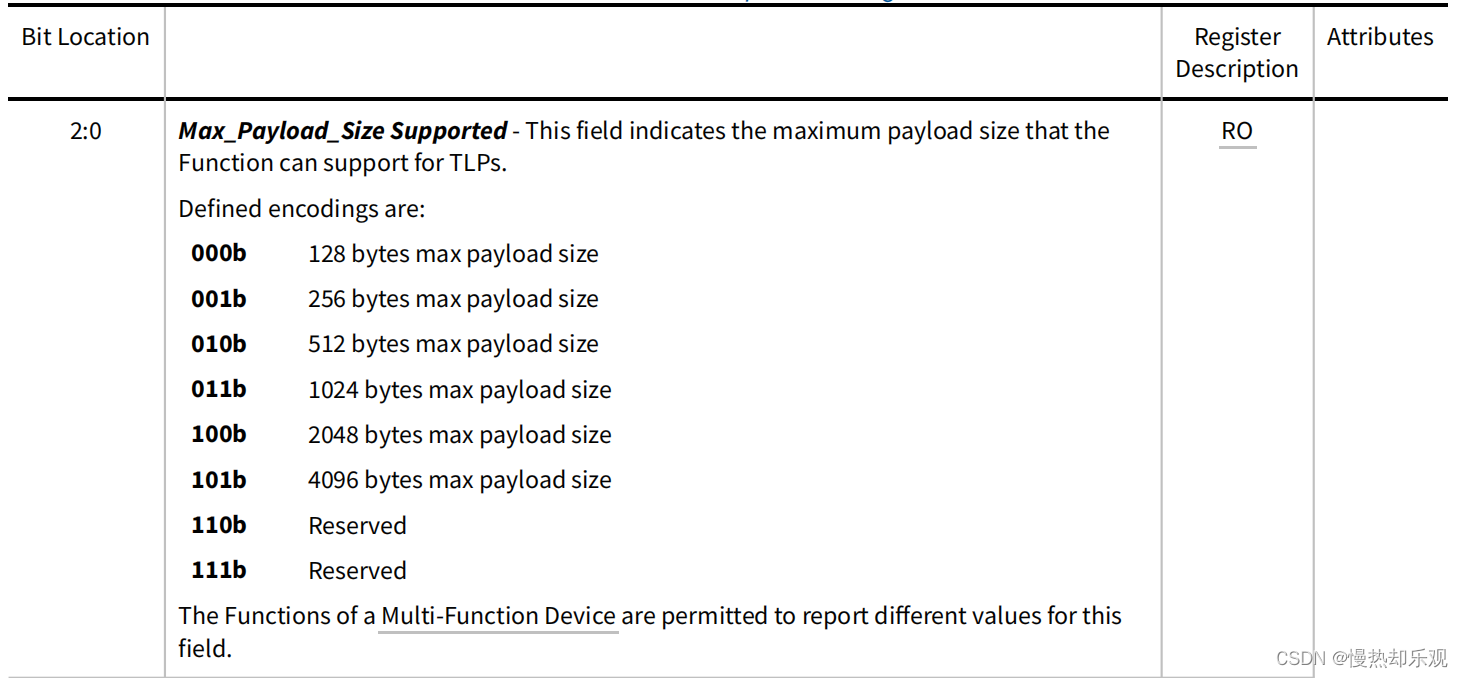

比如我需要抓取盘端的MaxPayload值,lspci下可以看到如下讯息:

Capabilities: [70] Express (v2) Endpoint, MSI 00

DevCap: MaxPayload 256 bytes, PhantFunc 0, Latency L0s unlimited, L1 unlimited

ExtTag- AttnBtn- AttnInd- PwrInd- RBE+ FLReset+ SlotPowerLimit 0.000W

使用setpci也可以抓到:

[root@localhost ~]# setpci -s 01:00.0 70+04.w

8fc1

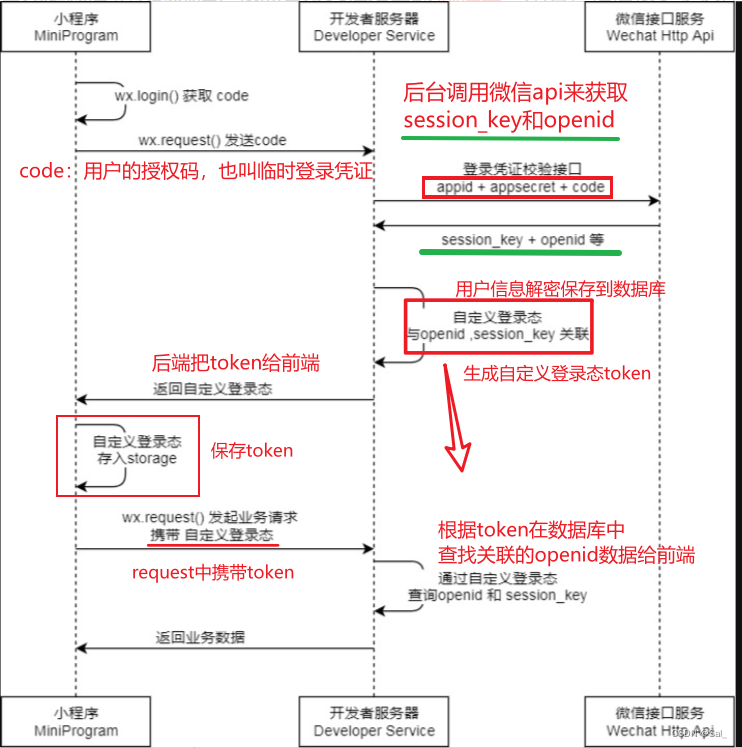

可以看到, -s 01:00.0 是盘的bdf,那么后面的 70+04.w是什么意思呢?

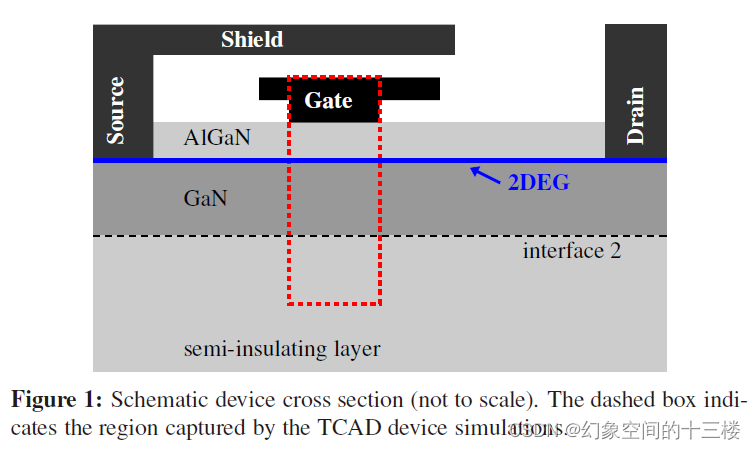

70对应 lspci读到的 Capabilities的起始位, +04 代表偏移量,这里的偏移量取自PCIe Spec的规定

w 代表两个字节

如上,我们抓到的值为 8fc1,16进制,转换为2进制为 1000 1111 1100 0001 ,参考上图:Max_Payload_Size Supported 对应 0-2 bit,因此这里得到的值为 1000 1111 1100 0001,此处001再参照PCIe Spec,得到值为256

这个就是如何去参考lspci信息和Spec去抓取我们想要的信息。注意上图中 register Description 栏下的 RO 代表 read only,即此处的值是不可被修改的,后续我们再将如何对可以修改的项目进行修改

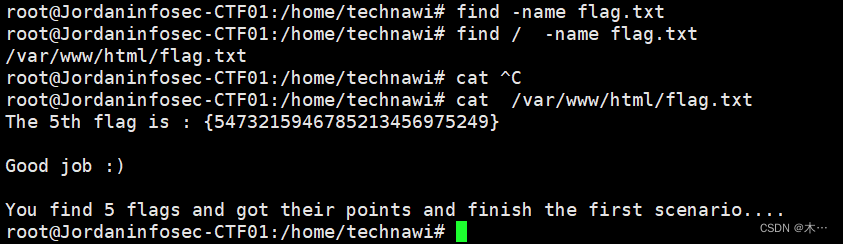

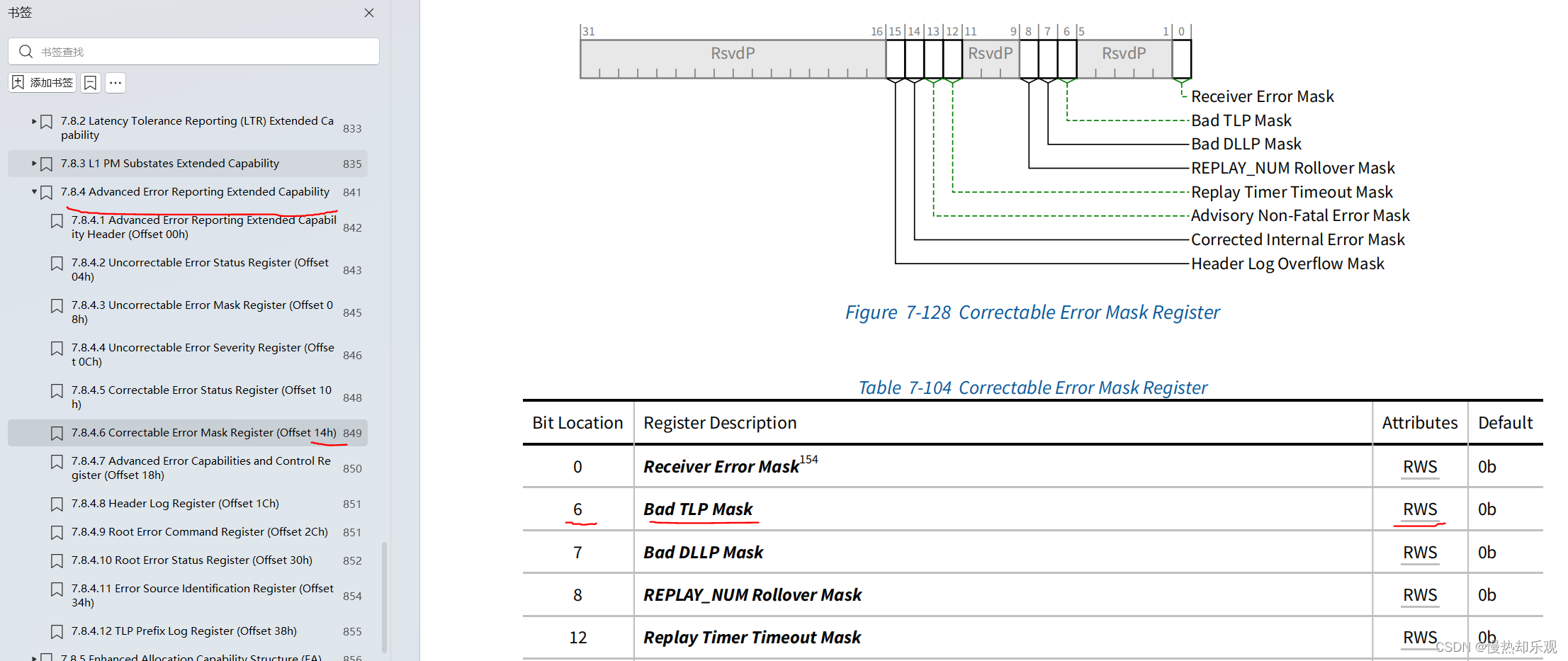

使用setpci修改

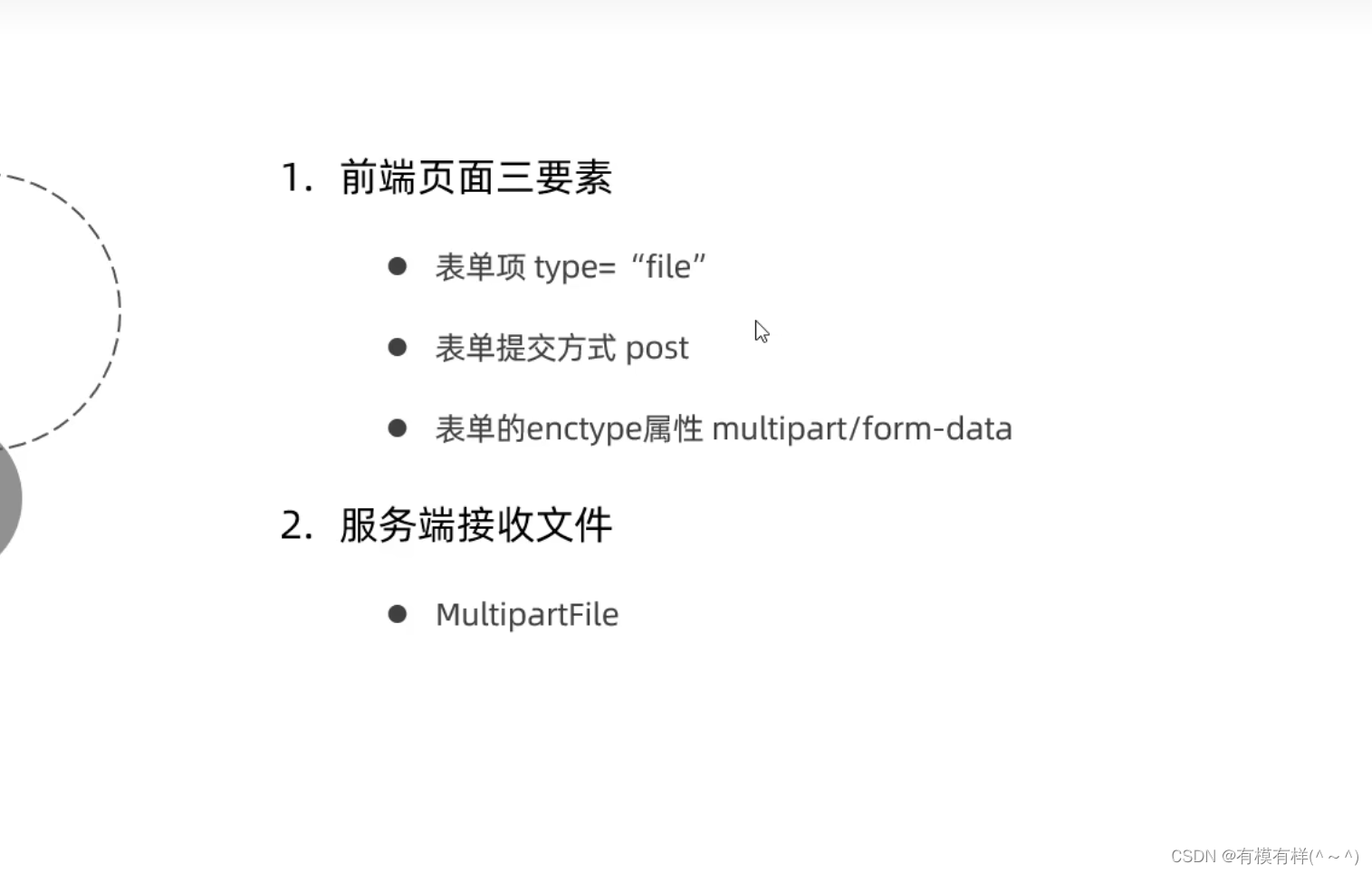

如上图,我们准备对此项进行修改,对照Spec,知道偏移量为 14h

参考lspci信息,起始位为100

Capabilities: [100 v2] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr-

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- NonFatalErr+

AERCap: First Error Pointer: 00, GenCap+ CGenEn- ChkCap+ ChkEn-

下命令抓取现在的值:

[root@localhost ~]# setpci -s 01:00.0 100+14.w

e000

转为2进制 1110 0000 0000 0000, spec定义第6位,默认为0

我们将第6位置为1,得到 1110 0000 0100 0000,16进制为e040

于是命令如下:

直接再后面加=e040赋值即可修改,修改完成后,再次读回来,返回生效

[root@localhost ~]# setpci -s 01:00.0 100+14.w=e040

[root@localhost ~]# setpci -s 01:00.0 100+14.w

e040

[root@localhost ~]#

我们再lspci -vvvxxx -s bdf看一下现在显示是怎么样的

CEMsk: RxErr- BadTLP+ BadDLLP- Rollover- Timeout- NonFatalErr+

可以看到原来 CEMsk是 BadTLP-,我们将其置一后,现在是BadTLP+,修改生效

此方法同样适用于修改LinkSpeed及LinkDisable等项,用法和参照方法是一样的