1.原理

并串转化是指的是完成串行传输和并行传输两种传输方式之间的转换的技术,通过移位寄存器可以实现串并转换。

串转并,将数据移位保存在寄存器中,再将寄存器的数值同时输出;

并转串,将数据先进行移位,再讲寄存器中的最高位或者最低位的数据串行输出。

关键点:

(1)串并转换的关键是在于触发器链,通过依次移位,输出最终结果。

(2)串并转换的思想是在设计中平衡面积和速度的要求,并行速度快,串行面积小。

(3)串并转换常常在接口中出现,将高速并行转为串行数据输出,或将低速的串行数据转为并行数据后高速计算。

2.牛客网练习实例1

VL62 序列发生器

- 题目

- 题解(29)

- 讨论(26)

- 排行

中等 通过率:20.64%

描述

编写一个模块,实现循环输出序列001011。

模块的接口信号图如下:

要求使用Verilog HDL实现,并编写testbench验证模块的功能。

输入描述:

clk:时钟信号

rst_n:复位信号,低电平有效

输出描述:

data:输出数据

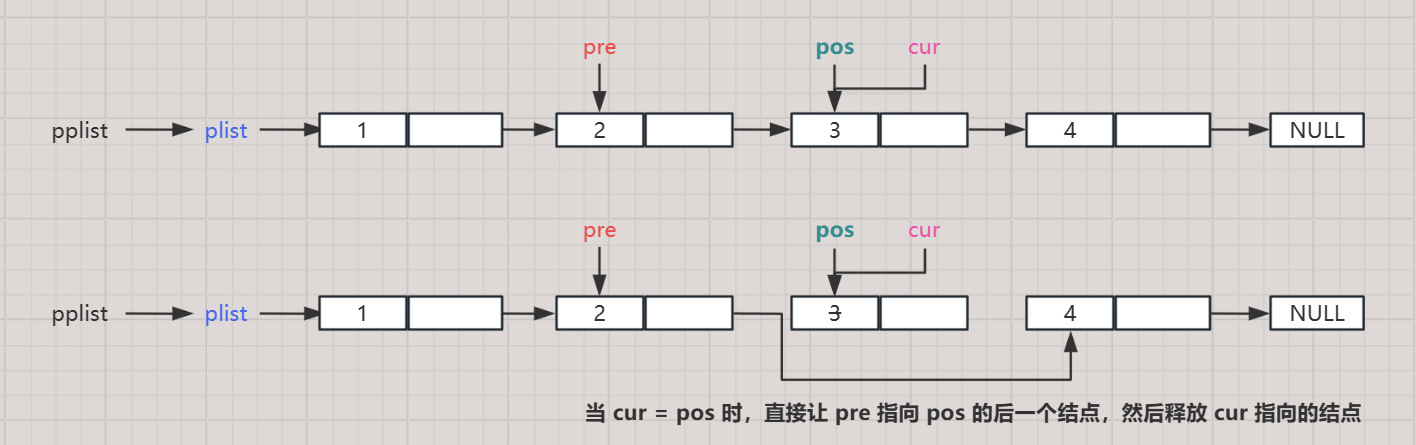

本题可以用状态机来写但是有点杀鸡用牛刀的操作,实际上可以理解为一个并行输入,转换成串行输出,MSB输出。先移位,然后再输出MSB位

`timescale 1ns/1ns

module sequence_generator(

input clk,

input rst_n,

output reg data

);

reg [5:0 ] data_left_reg ;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

data_left_reg <= 6'b001_011 ;

end

else

data_left_reg <= {data_left_reg[4 :0], data_left_reg[5]} ; //循环向左移动

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

data <= 1'd0 ;

end

else

data <= data_left_reg[5] ;

end

endmodule3牛客网练习实例2 ——并串转换

VL63 并串转换

- 题目

- 题解(17)

- 讨论(24)

- 排行

中等 通过率:10.78%

描述

题目描述:

设计一个模块进行并串转换,要求每四位d输为转到一位dout输出,输出valid_in表示此时的输入有效

信号示意图:

clk为时钟

rst为低电平复位

valid_in 表示输入有效

d 信号输入

dout 信号输出

波形示意图:

输入描述:

clk为时钟

rst为低电平复位

d 信号输入

输出描述:

dout 信号输出

valid_in 表示输入有效

`timescale 1ns/1ns

module huawei5(

input wire clk ,

input wire rst ,

input wire [3:0]d ,

output wire valid_in ,

output wire dout

);

//*************code***********//

reg [1 : 0] cnt ;

reg valid_in_reg ;

reg [3:0 ]data_out ;

wire rst_n ;

assign rst_n = ~rst ;

always@ (posedge clk or posedge rst_n) begin

if (rst_n )

cnt <= 2'b0 ;

else if (cnt == 2'd3)

cnt <= 2'd0 ;

else

cnt <= cnt + 1 ;

end

always@ (posedge clk or posedge rst_n)begin

if (rst_n)

valid_in_reg <= 1'b0 ;

else if (cnt == 2'd3)

valid_in_reg <= 1'b1 ;

else

valid_in_reg <= 1'b0;

end

always@(posedge clk or posedge rst_n) begin

if (rst_n)

data_out <= 4'b0000 ;

else if (cnt == 3 )

data_out <= d ;

else

data_out <= data_out << 1;

end

assign valid_in = valid_in_reg ;

assign dout = data_out[3] ;

//*************code***********//

endmodule

![[AndroidStudio]_[初级]_[修改虚拟设备镜像文件的存放位置]](https://img-blog.csdnimg.cn/04cebe41940c400ebae57bcfd902240a.png)