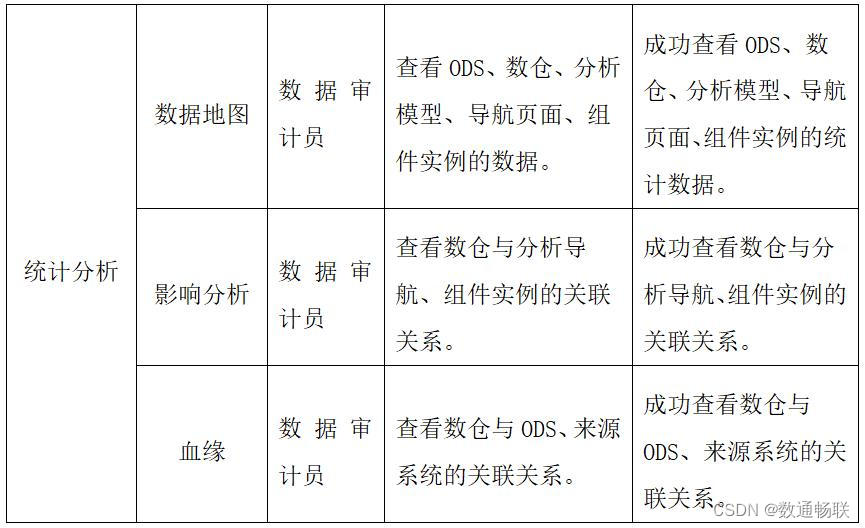

文章目录

- 一、文件导入

- 二、VCS仿真(使用可视化界面)

- 三、VCS仿真(使用Maefile文件)

- 3.1 Makefile文件编写

- 3.2 仿真文件编写规范

- 3.3 Makefile文件使用

一、文件导入

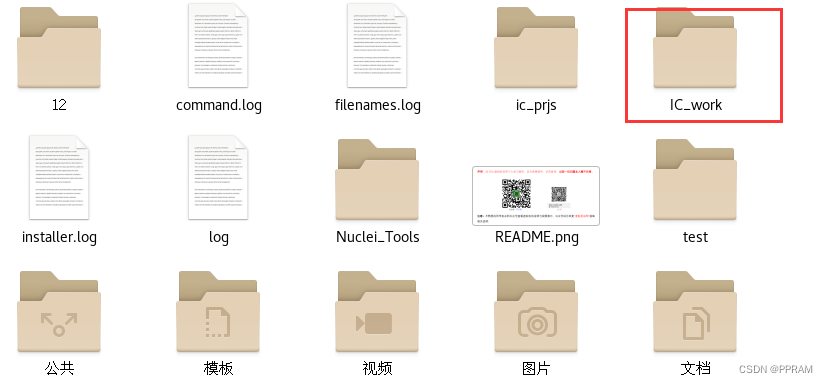

新建一个文件夹新建一个文件夹(图中IC_work)

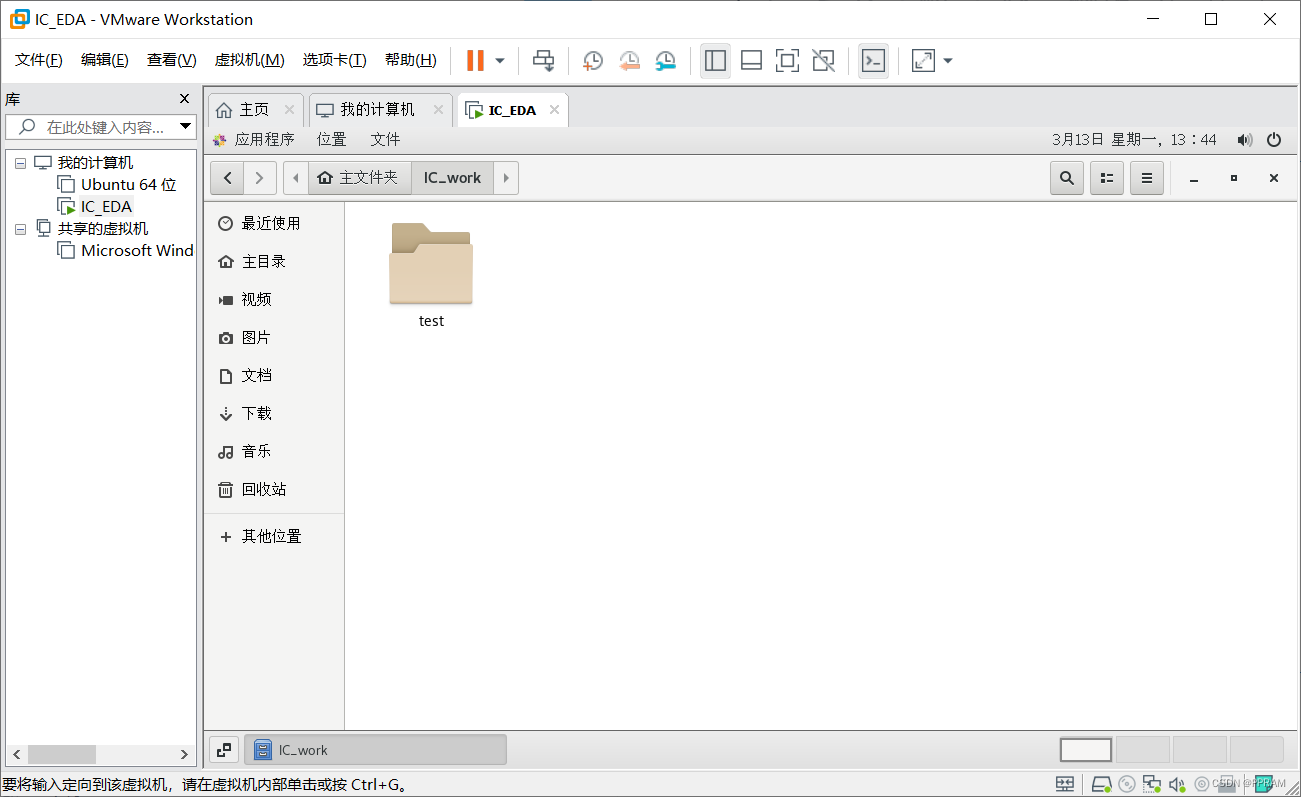

创建一个目录,用来存放文件(图中test)

创建一个目录,用来存放文件(图中test)

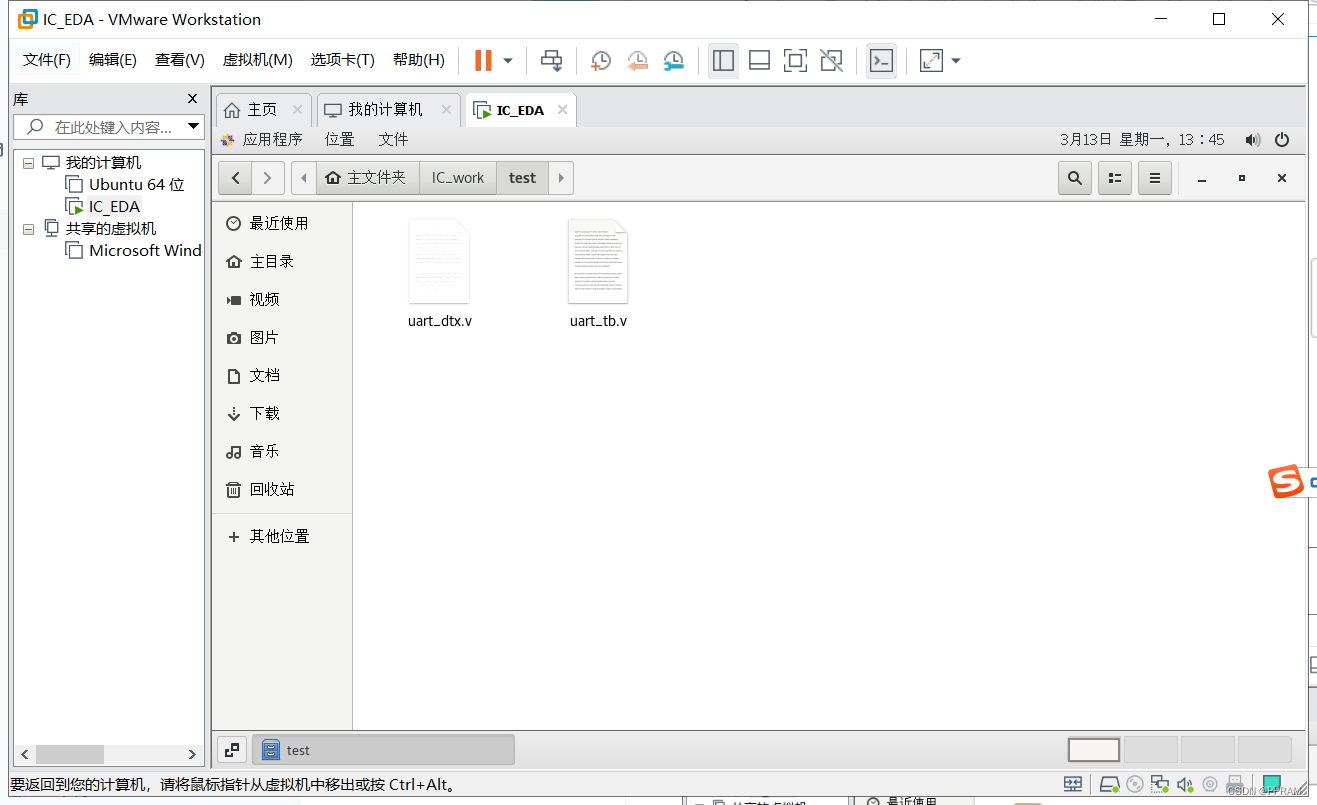

将要操作的文件复制到文件夹下:

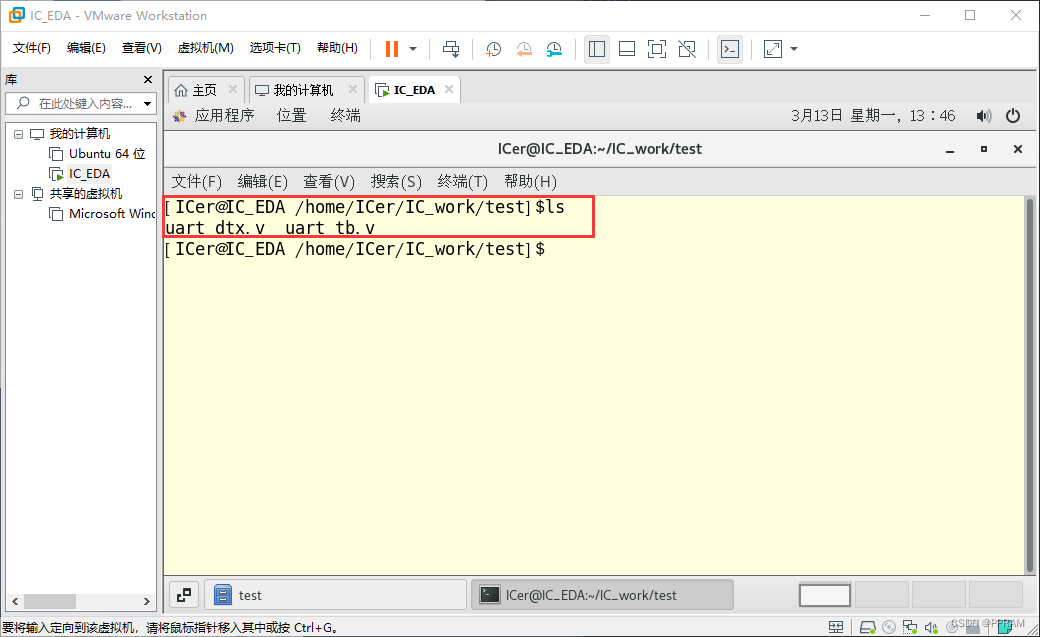

将要操作的文件复制到文件夹下: 此时打开终端,输入命令ls可以查看文件是否存在。

此时打开终端,输入命令ls可以查看文件是否存在。

二、VCS仿真(使用可视化界面)

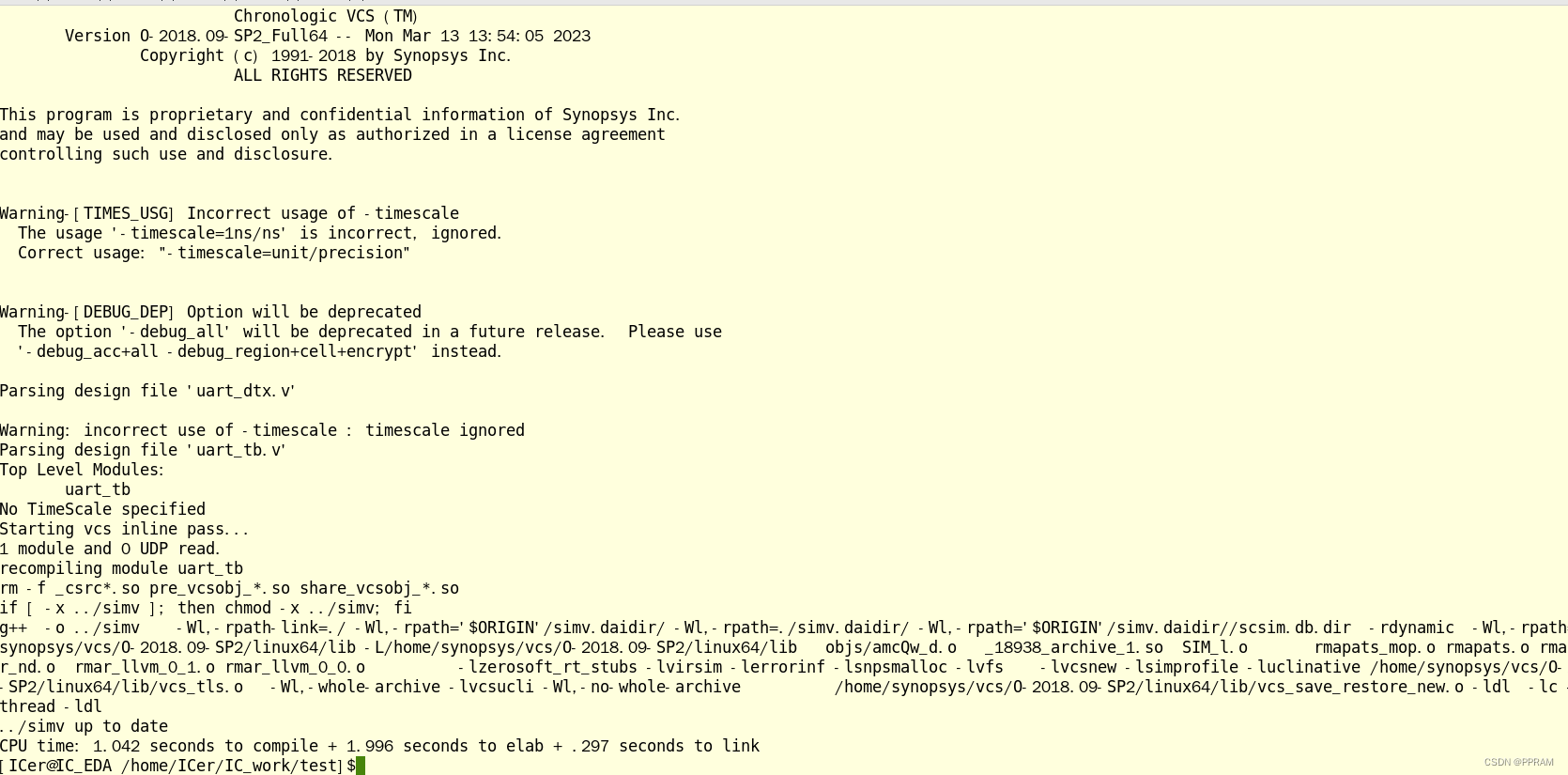

输入下面指令,对设计文件进行编译:

vcs -full64 -sverilog -debug_all -timescale=1ns/ns uart_dtx.v uart_tb.v -l com.log

输入后终端显示如下:

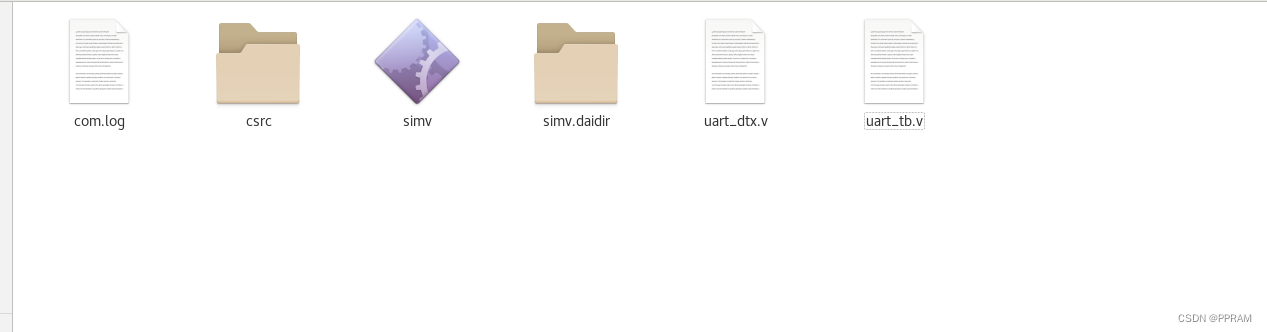

目标文件夹下会多出一些文件

目标文件夹下会多出一些文件

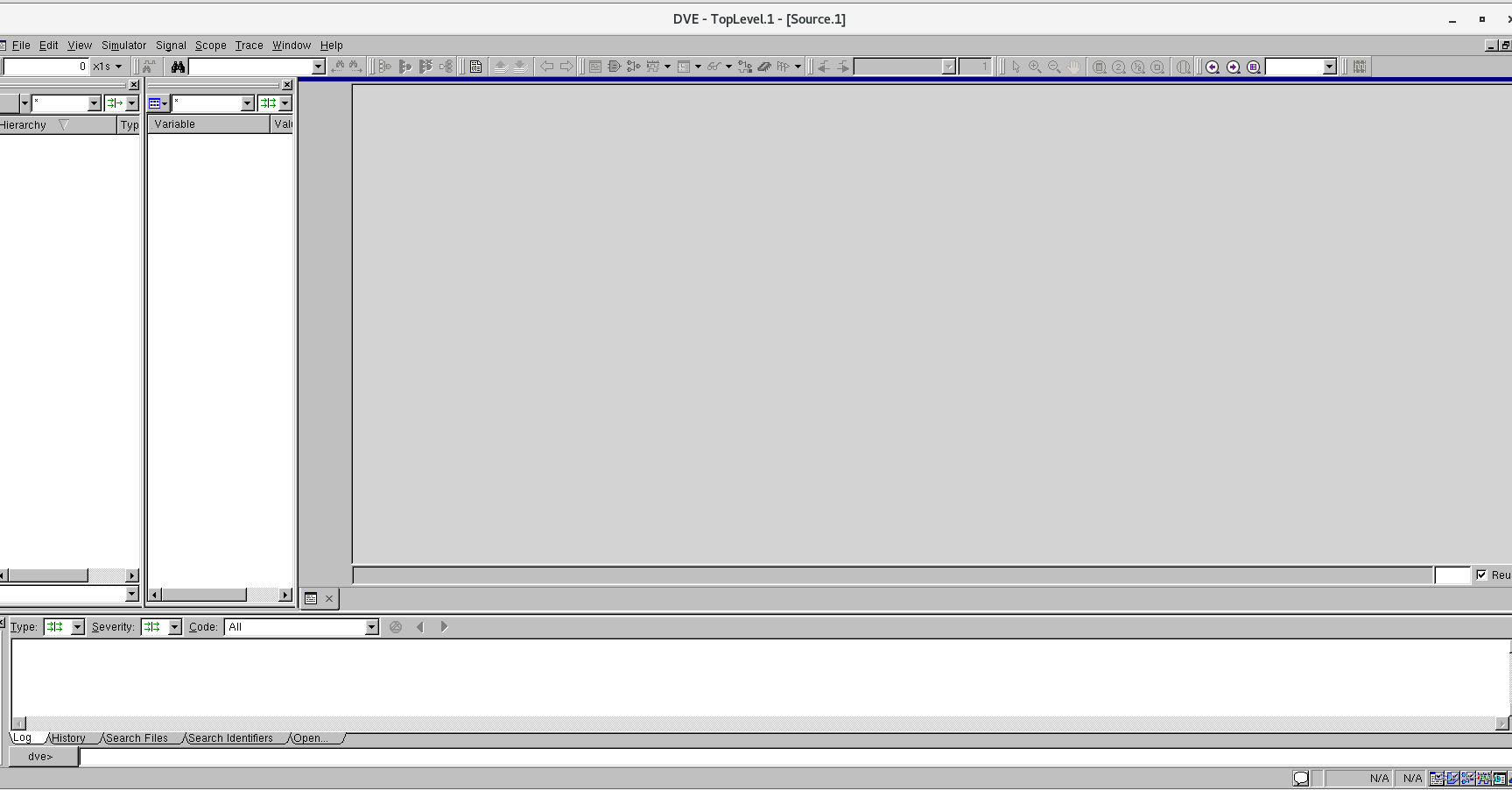

输入以下指令,打开VCS可视化界面:

输入以下指令,打开VCS可视化界面:

dve &

点击simulate -> set up

点击simulate -> set up

选择simv文件,点击ok

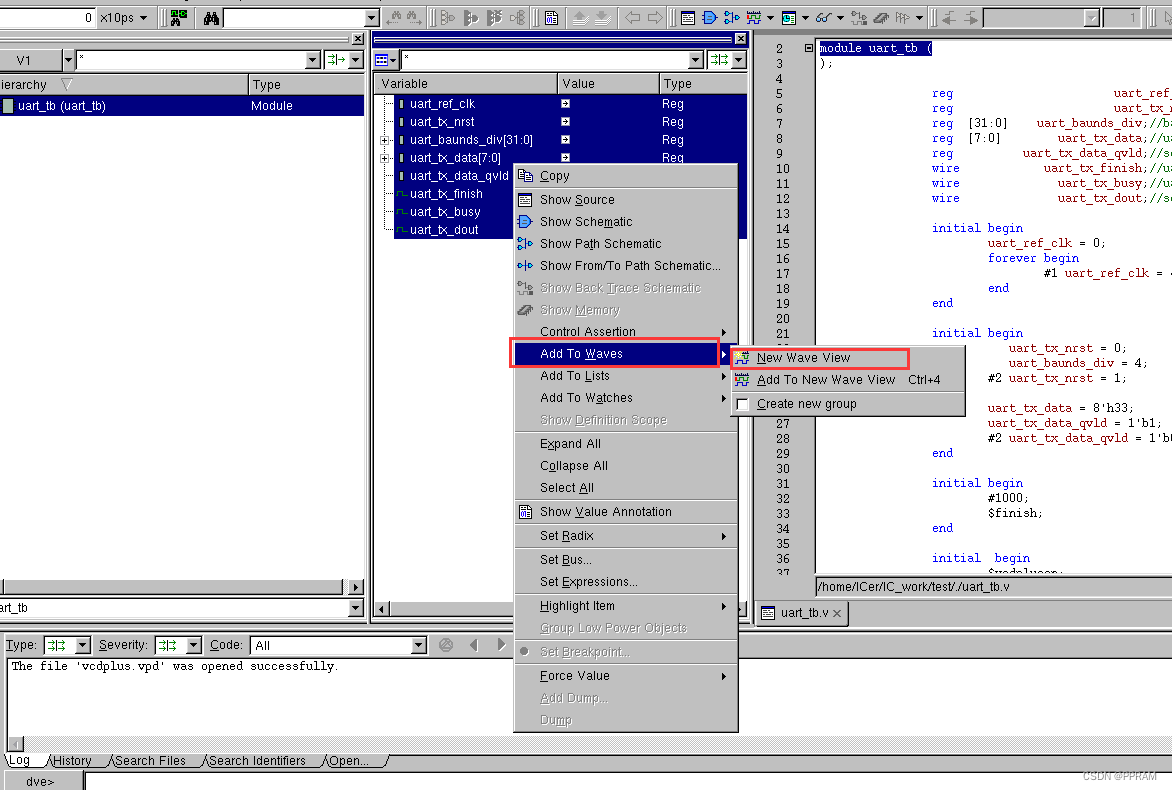

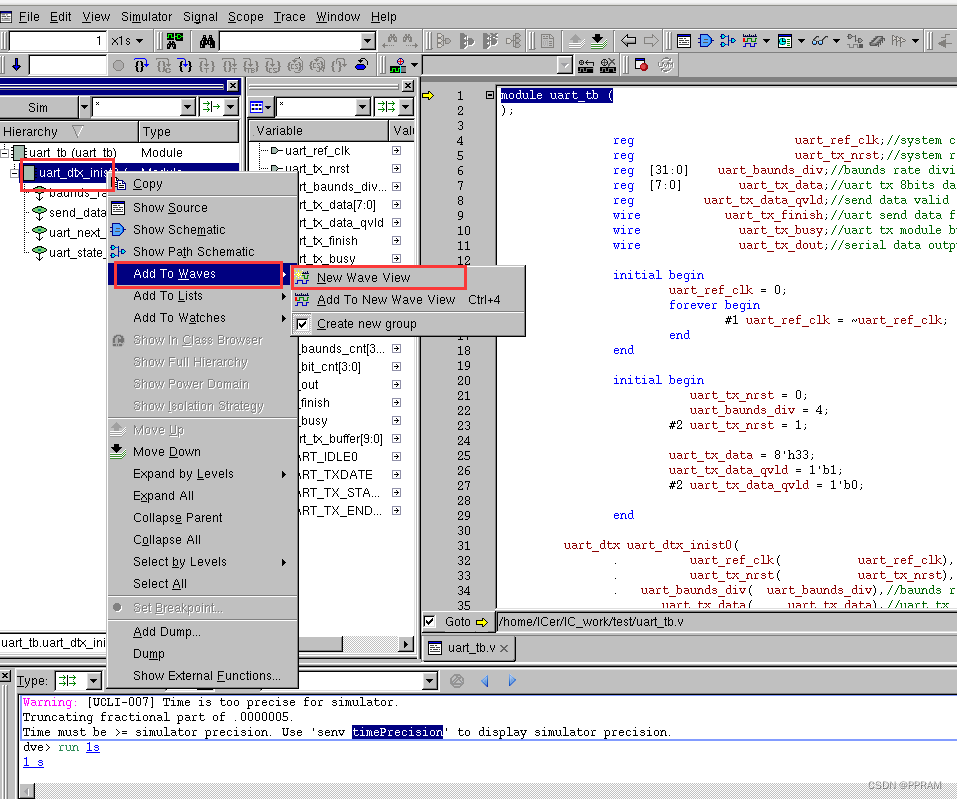

右击文件,选择Add to Waves->creat new group

右击文件,选择Add to Waves->creat new group

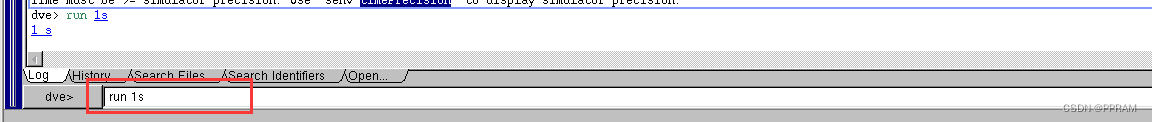

在dve终端输入run 1s表示总共跑1s

在dve终端输入run 1s表示总共跑1s

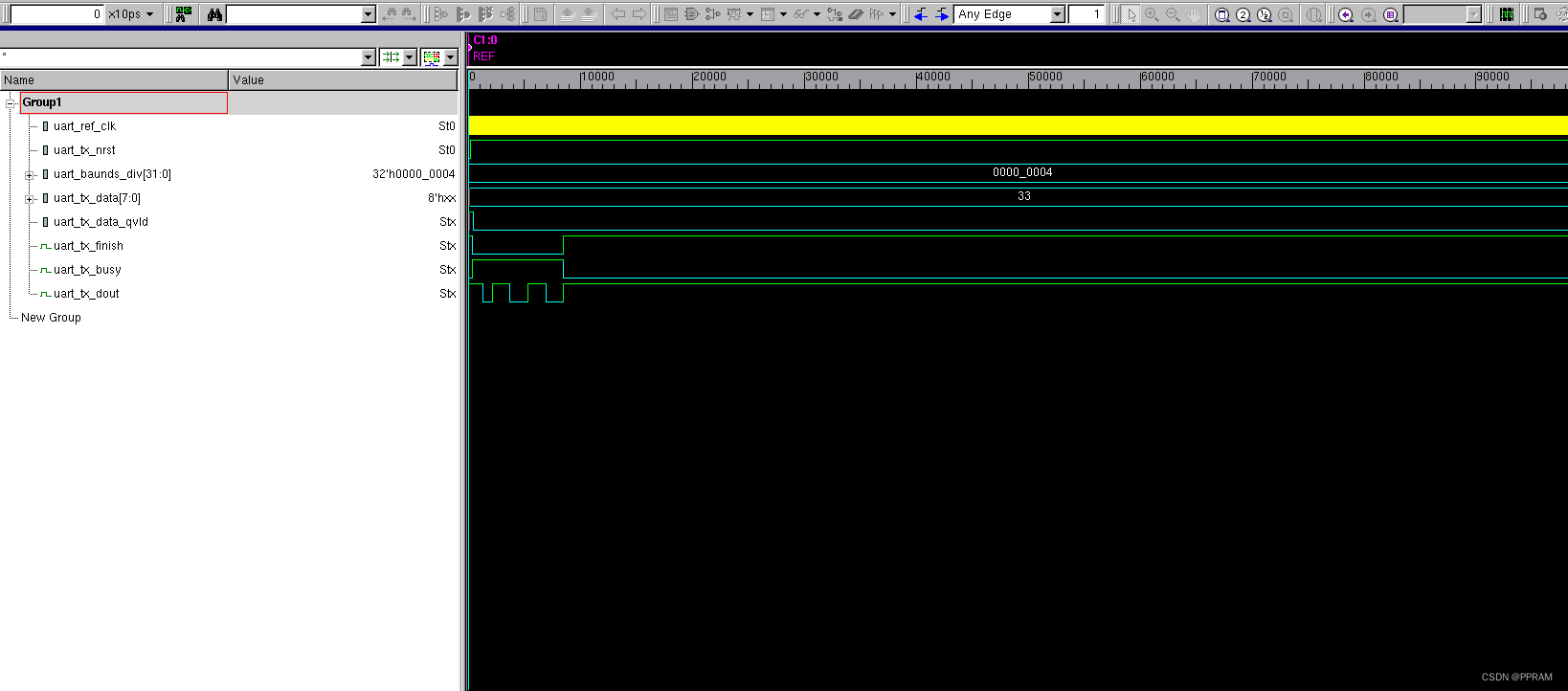

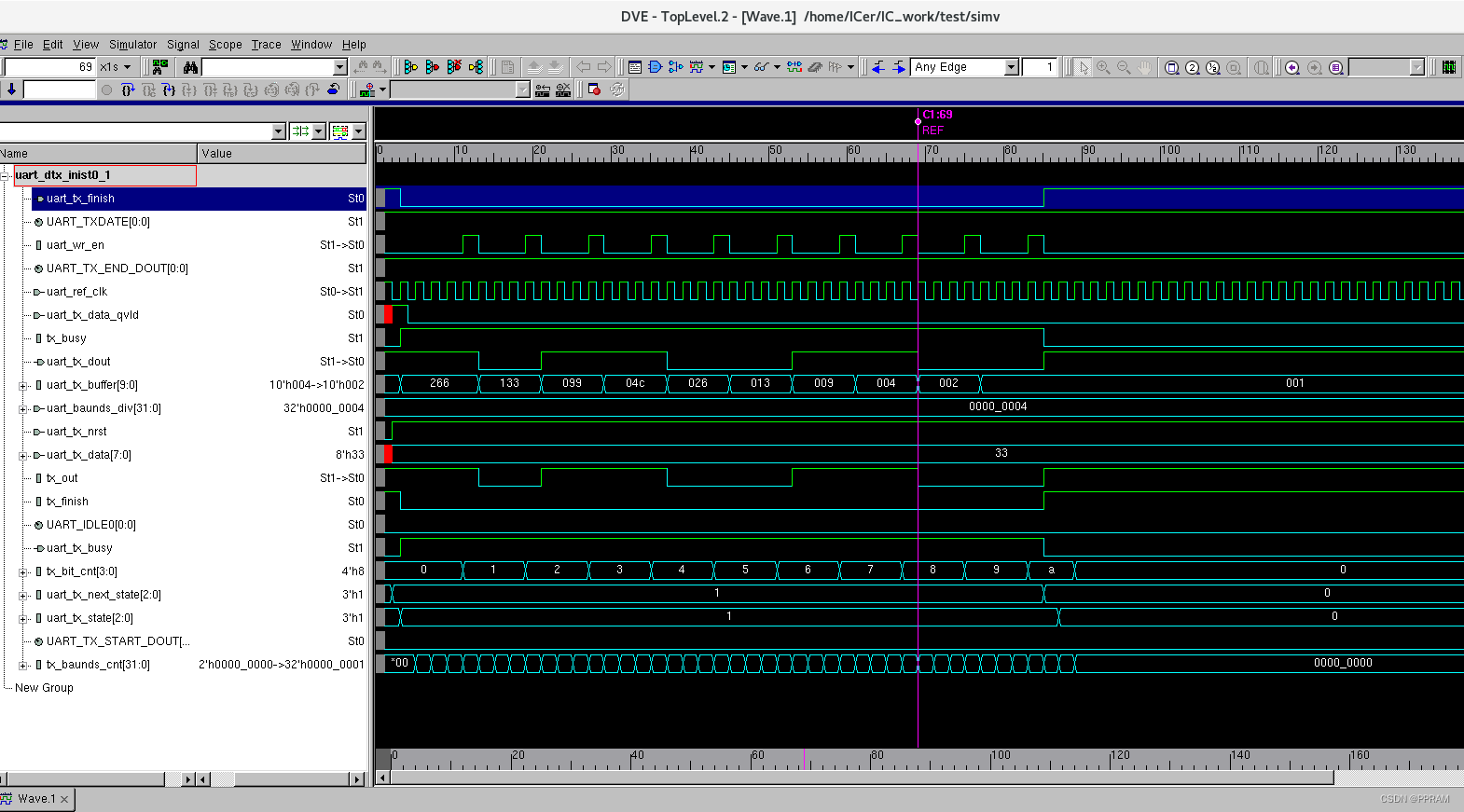

即可看到仿真波形;

即可看到仿真波形;

三、VCS仿真(使用Maefile文件)

3.1 Makefile文件编写

c编写Makefile文件可以让上述过程变得更简单。

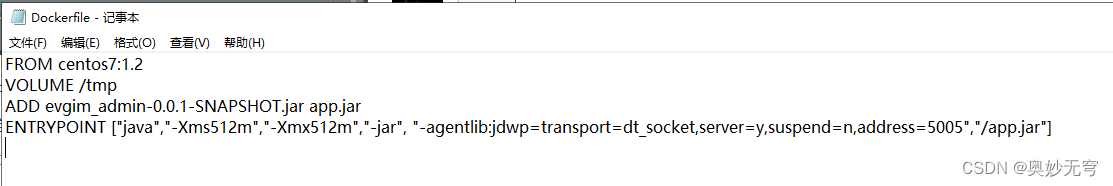

输入gvim Makefile编辑Makefile文件,在其中写入以下内容。

Makefile文件内容:

all:find com sim run_dve

find:

find -name "*.v" > file.list

com:

vcs -full64 +vcs+vcdpluson -sverilog -debug_all -f file.list -l vcs.log

sim:

./simv -l vcs.log

run_dve:

dve -full64 -vpd vcdplus.vpd &

clean:

rm -rf *.vpd csrc *.log *.key *.vpd simv* DVE*

find:

执行 find -name “*.v” > file.list 指令,将目录下的所有.v文件名写入file.list文件中。

com:

执行 vcs -full64 +vcs+vcdpluson -sverilog -debug_all -f file.list -l vcs.log 指令,对file.list列出的设计文件进行编译。其中+vcs+vcdpluson必须,可生成接下来的vcdplus.vpd文件。

sim:

执行./simv -l vcs.log 命令,对设计文件进行仿真。

run_dve:

执行dve -full64 -vpd vcdplus.vpd & 命令,启动可视化界面,并读入波形文件。

3.2 仿真文件编写规范

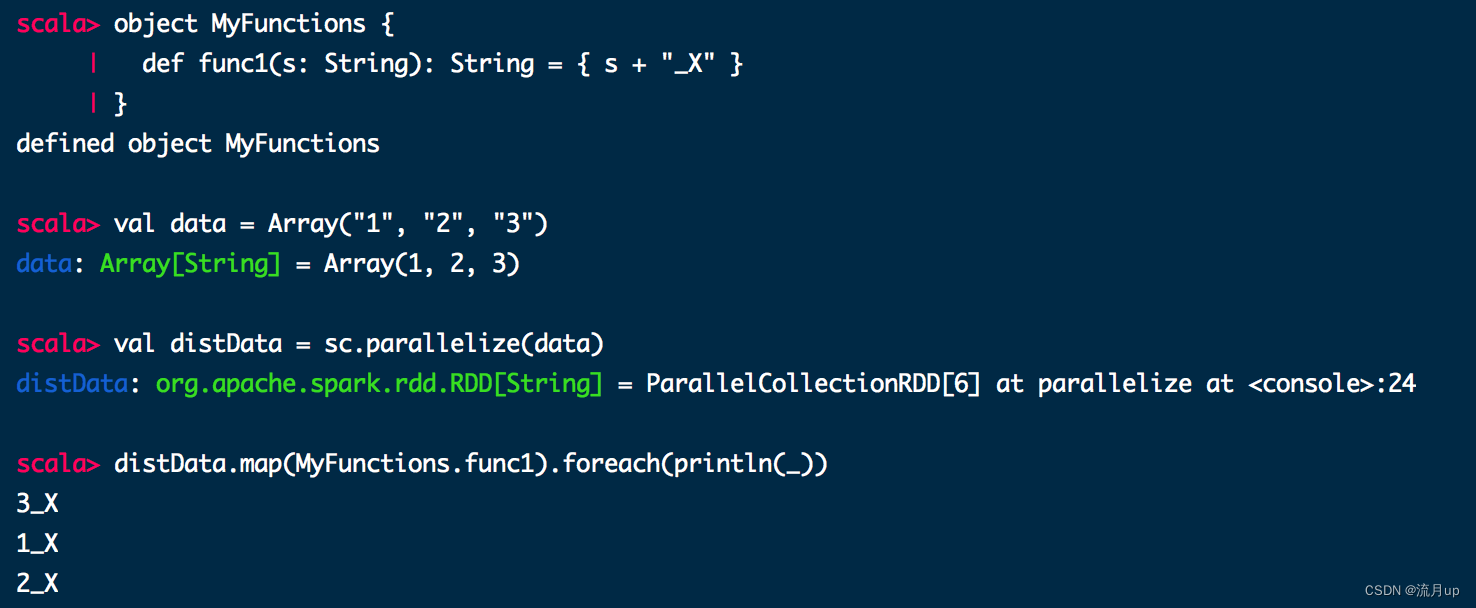

使用Makefile进行仿真时,测试文件的编写需要满足一定的规范。

示例的测试文件如下:

`timescale 1ns/10ps

module uart_tb (

);

reg uart_ref_clk;//system clock reference

reg uart_tx_nrst;//system reset signal

reg [31:0] uart_baunds_div;//baunds rate division

reg [7:0] uart_tx_data;//uart tx 8bits data input

reg uart_tx_data_qvld;//send data valid signal

wire uart_tx_finish;//uart send data finish flag

wire uart_tx_busy;//uart tx module busy flag

wire uart_tx_dout;//serial data output

initial begin

uart_ref_clk = 0;

forever begin

#1 uart_ref_clk = ~uart_ref_clk;

end

end

initial begin

uart_tx_nrst = 0;

uart_baunds_div = 4;

#2 uart_tx_nrst = 1;

uart_tx_data = 8'h33;

uart_tx_data_qvld = 1'b1;

#2 uart_tx_data_qvld = 1'b0;

end

initial begin

#1000;

$finish;

end

initial begin

$vcdpluson;

end

uart_dtx uart_dtx_inist0(

. uart_ref_clk( uart_ref_clk),//system clock reference

. uart_tx_nrst( uart_tx_nrst),//system reset signal

. uart_baunds_div( uart_baunds_div),//baunds rate division

. uart_tx_data( uart_tx_data),//uart tx 8bits data input

. uart_tx_data_qvld(uart_tx_data_qvld),//send data valid signal

. uart_tx_finish( uart_tx_finish),//uart send data finish flag

. uart_tx_busy( uart_tx_busy),//uart tx module busy flag

. uart_tx_dout( uart_tx_dout) //serial data output

);

endmodule

其中需注意,在第1行要添加`timescale 1ns/10ps仿真时间;

第31-34行添加整个仿真结束命令&finish,当仿真文件执行到此处,则退出仿真。若缺少该语句,则Makefile会卡死在sim过程(vcs仿真过程)。也可以不使用KaTeX parse error: Expected 'EOF', got '&' at position 25: …须在命令中指出仿真结束时间。 &̲emsp; 第36-…vcdpluson来产生vpd文件。

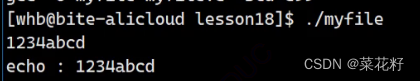

3.3 Makefile文件使用

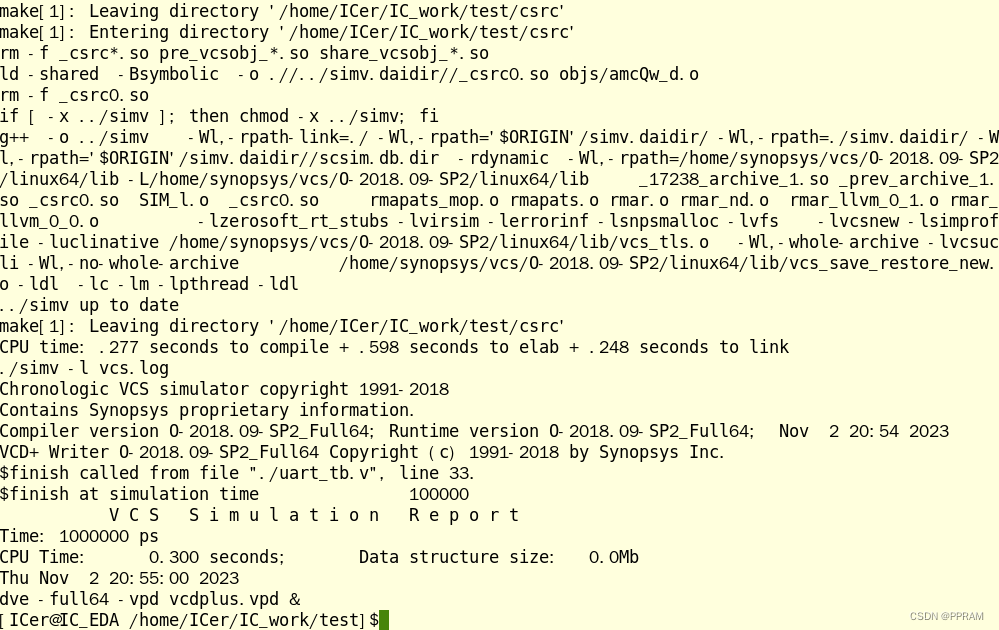

使用Makefile文件来进行仿真,只需要打开终端,写入make all指令即可,输入命令后,终端显示如下说明仿真成功:

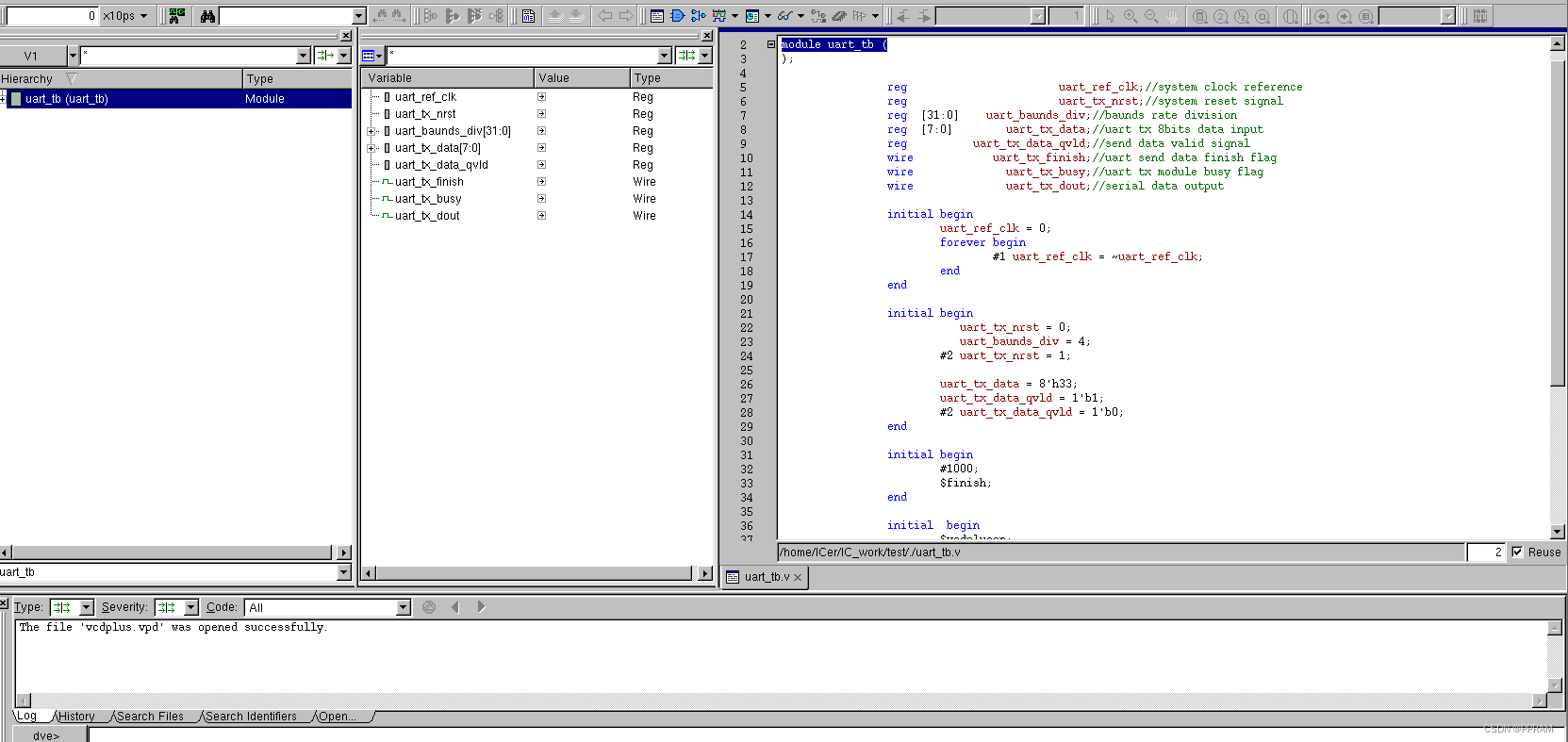

等待片刻后,会打开VCS可视化界面。

等待片刻后,会打开VCS可视化界面。

选中需要查看的信号,右击选择Add To Waves -> New Wave View即可观察波形。

选中需要查看的信号,右击选择Add To Waves -> New Wave View即可观察波形。