在Verilog中,#parameter用于指定延迟时间。下面是一个全面的Demo:

```

module demo;

parameter DELAY = 10;

reg clk;

initial begin

clk = 0;

#DELAY $display("Delay time is %d", DELAY);

#DELAY $display("Clock is %b", clk);

#DELAY $finish;

end

always #5 clk = ~clk;

endmodule

```

在这个Demo中,我们定义了一个DELAY参数,并将其设置为10。

然后,我们定义了一个时钟信号clk,并使用always块来生成一个时钟信号。

在initial块中,我们使用#DELAY指定了延迟时间,并在每个延迟时间后打印一些信息。

最后,我们使用#DELAY $finish来结束仿真。

#parameter【FPGA】

news2026/2/14 21:27:13

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1156324.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

【QT开发笔记-基础篇】| 第四章 事件QEvent | 4.11 小案例-无边框窗口

本节对应的视频讲解:B_站_链_接 【QT开发笔记-基础篇】 第4章 事件 4.11 小案例-无边框窗口 本章要实现的整体效果如下: 本节课,来实现一个非常精简的无边框窗口,支持拖动4个边和4个角来缩放窗口

整体效果如下: 整体效…

【红蓝攻防鸿篇巨著】ATTCK视角下的红蓝对抗实战指南

【文末送书】今天推荐一本网安领域优质书籍《ATT&CK视角下的红蓝对抗实战指南》,本文将从其亮点与内容出发,详细阐发其对于网安从业人员的重要性与益处。 文章目录 背景简介内容文末送书 背景

根据中国互联网络信息中心(CNNIC࿰…

“2024杭州智慧城市展“汇集全球领先的智慧城市解决方案和前沿技术

2024杭州智慧城市展览会,将于2024年4月份在杭州国际博览中心盛大召开。此次展览会以智慧城市为主题,涵盖了智慧城市、信息安全、数据中心与通信、人工智能、公共安全、会议广播视讯、智慧社区与智能家居、智慧停车等八个模块,旨在推动互联网、…

基于英伟达NVIDIA Jetson Xavier nx的Ubuntu系统安装nginx,mysql, java8

记录一下基于英伟达NVIDIA Jetson Xavier nx的Ubuntu系统安装nginx,mysql, java8(非docker方式)

nx系统主要用于开发ai边缘人工智能视觉计算,人脸识别,车辆识别等,同样的也可以部署一些常见的程序应用

nx系统界面 …

x3daudio1 7.dll丢失怎么修复?多种x3daudio1 7.dll修复方法对比

x3daudio1_7.dll是Windows操作系统中的一个动态链接库文件,它主要负责处理音频相关的功能。当这个文件缺失或损坏时,可能会导致一些音频播放问题,如无声、杂音等。那么,x3daudio1_7.dll缺失的原因是什么呢?又该如何修复…

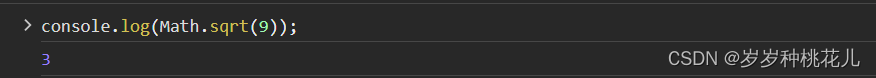

JavaScript从入门到精通系列第二十六篇:详解JavaScript中的Math对象

大神链接:作者有幸结识技术大神孙哥为好友,获益匪浅。现在把孙哥视频分享给大家。 孙哥连接:孙哥个人主页 作者简介:一个颜值99分,只比孙哥差一点的程序员 本专栏简介:话不多说,让我们一起干翻J…

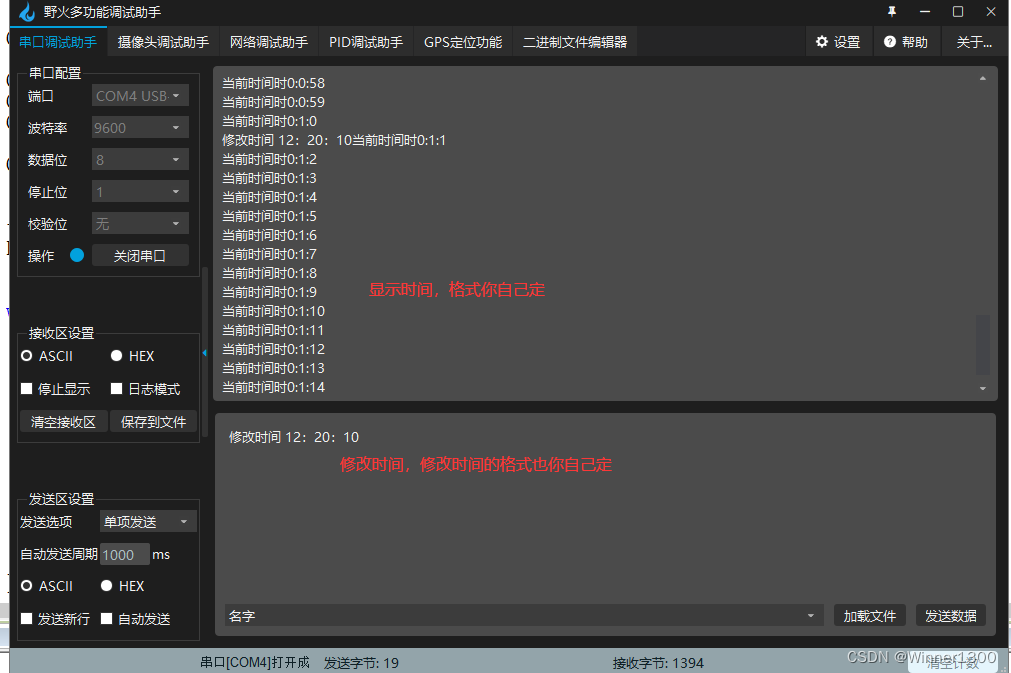

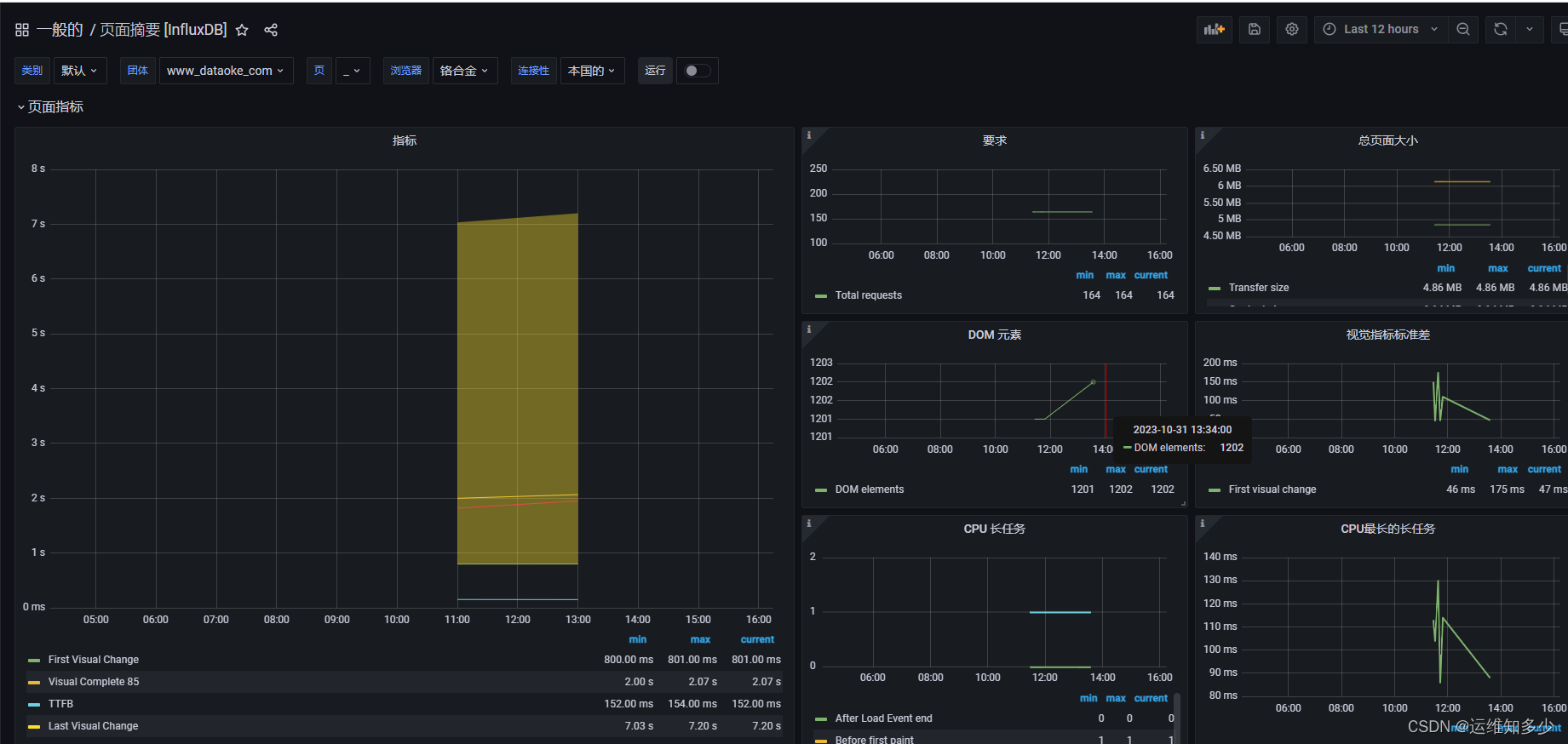

sitespeedio.io 前端页面监控安装部署接入influxdb 到grafana

1.docker部署influxdb,部署1.8一下,不然语法有变化后面用不了grafana模板

docker run -d -p 8086:8086 --name influxdb -v $PWD/influxdb-data:/var/lib/influxdb influxdb:1.7.11-alpine

docker exec -it influxdb_id bash

#influx

create user admin with pass…

基于供需算法的无人机航迹规划-附代码

基于供需算法的无人机航迹规划 文章目录 基于供需算法的无人机航迹规划1.供需搜索算法2.无人机飞行环境建模3.无人机航迹规划建模4.实验结果4.1地图创建4.2 航迹规划 5.参考文献6.Matlab代码 摘要:本文主要介绍利用供需算法来优化无人机航迹规划。 1.供需搜索算法

…

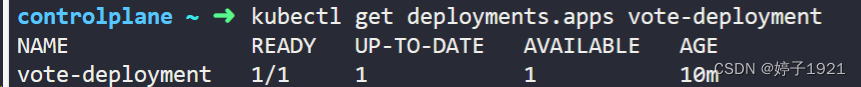

kubernetes实验挑战三(| Vote App | Redis | Postgresql DB | Deployment | service)

Deploy the given architecture to vote namespace. 1、Create a new namespace: name ‘vote’

kubectl create ns vote2、

Create new deployment. name: ‘worker’image: ‘kodekloud/examplevotingapp_worker’status: ‘Running’

kubectl create deployment worker…

感觉嵌入式嵌入式单片机太难了,该不该放弃?

今日话题,感觉嵌入式单片机太难了,该不该放弃?嵌入式和单片机开发可能是一项具有挑战性但也非常有前景的领域。虽然它的学习曲线可能陡峭,但只要你克服了一开始的难度,你可能会发现它非常有趣且有价值。不要轻易放弃&a…

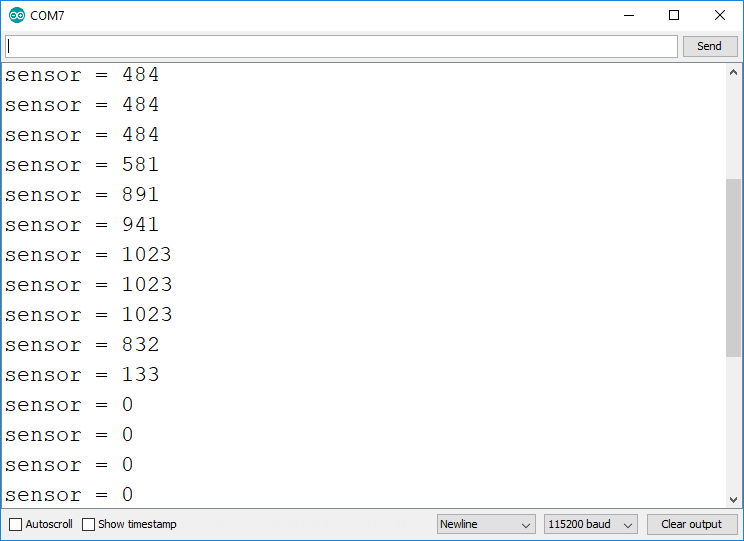

NodeMCU ESP8266 操作ADC读取外部模拟信号教程详解

文章目录 前言原理介绍准备知识ADC分辨率输入电压范围Analog Pin 电路搭建示例代码结论 前言

NodeMCU ESP8266 上有一个引脚可以快速采集模拟信号,并将其转成数字信号。

这就是我们经常听到的模数转换器(ADC, Analog-to-Digital Converter )…

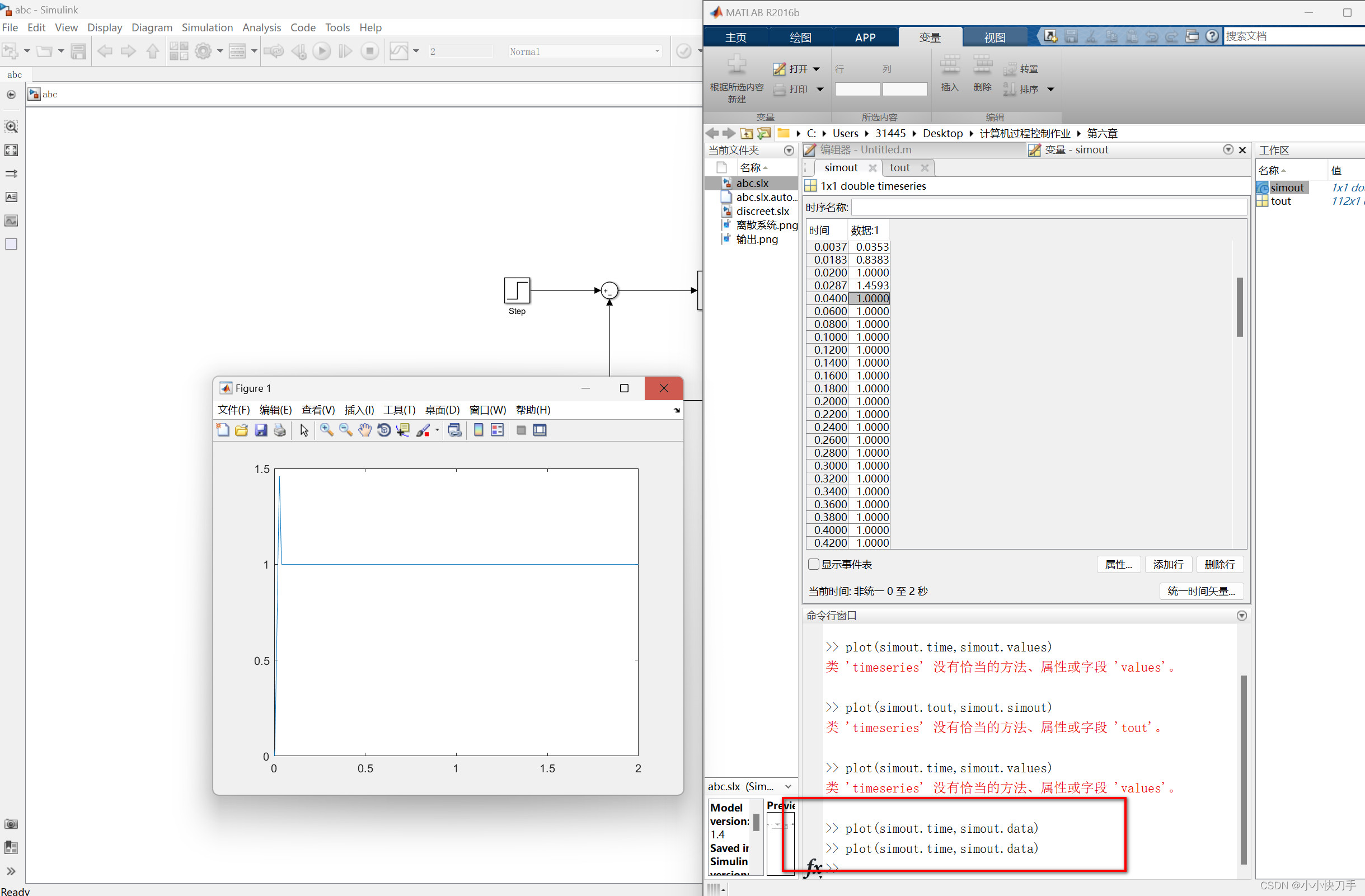

Simulink的To Workspace

To Workspace模块将Simulink产生的数据存储到matlab的工作区。 用To Workspace模块中的数据进行绘图。 参见Matlab/simulink/simscape multibody-to wotkspace模块使用_to workspace模块_五VV的博客-CSDN博客

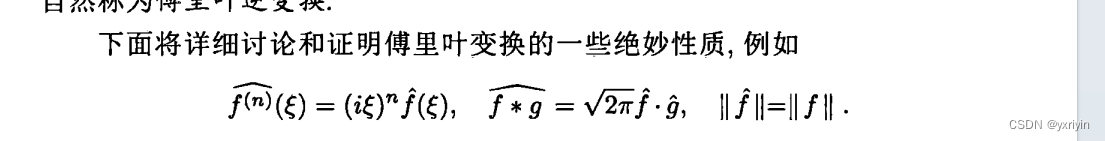

数学分析:傅里叶变换(完结撒花)

这里我觉得老师讲的更好。首先我们已经知道了周期函数的傅里叶级数,接下来对于非周期函数,其实可以看成周期无穷大的函数。我们把周期经过一个换元,重新看这个傅里叶级数。 这里要注意,我们发现这个无限周期的傅里叶级数ÿ…

【WinForm详细教程四】WinForm中的ProgressBar 、ImageList和ListView控件

文章目录 1.ProgressBar2. ImageList3.ListView控件 1.ProgressBar

用于显示某个操作的进度。

属性:

Value: 表示当前进度条的值,其范围由Min和Max决定。Step: 设置每次调用PerformStep()方法时增加的步长。MarqueeAnimationSpeed: 在Style设置为Marq…

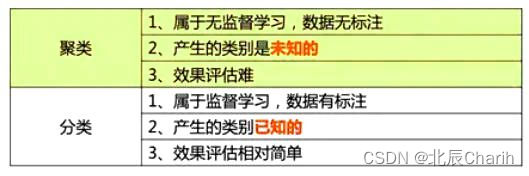

K-means(K-均值)算法

K-means(k-均值,也记为kmeans)是聚类算法中的一种,由于其原理简单,可解释强,实现方便,收敛速度快,在数据挖掘、聚类分析、数据聚类、模式识别、金融风控、数据科学、智能营销和数据运…

[架构之路-249/创业之路-80]:目标系统 - 纵向分层 - 企业信息化的呈现形态:常见企业信息化软件系统 - 产品(数据)管理

目录

前言:

一、企业信息化的结果:常见企业信息化软件

1.1 产品数据管理

1.1.1 什么是产品数据管理What

1.1.1.1 常见工具

1.1.1.2 软件企业的产品数据管理系统

1.1.2 为什么需要产品数据管理系统Why?

1.1.3 谁需要产品数据管理系统w…

STM32基本定时器中断

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、STM32定时器的结构?1. 51定时器的结构1.1如何实现定时1s的功能? 2. stm32定时器的结构2.1 通用定时器 二、使用步骤1.开启时钟2.初始…

![[架构之路-249/创业之路-80]:目标系统 - 纵向分层 - 企业信息化的呈现形态:常见企业信息化软件系统 - 产品(数据)管理](https://img-blog.csdnimg.cn/656209d4340349deabae69ad49750e8b.png)