续【AD9361 数字接口CMOS &LVDS&SPI】C 并行数据之LVDS

不同于CMOS的传输方式,lvds只能工作在双端口全双工模式下。

一、 双端口全双工模式 (LVDS)代称 DFL

DUAL PORT FULL DUPLEX MODE

DFL 模式通过写入SPI寄存器实现。在此模式下,P0 和 P1 均作为 LVDS 信号使能,数据总线 (D[11:0]) 被拆分为单独的子总线 (Rx_D[5:0] 和 Tx_D[5:0])。每个子总线同时工作,允许BBP和AD9361之间实现发送和接收数据的全双工。

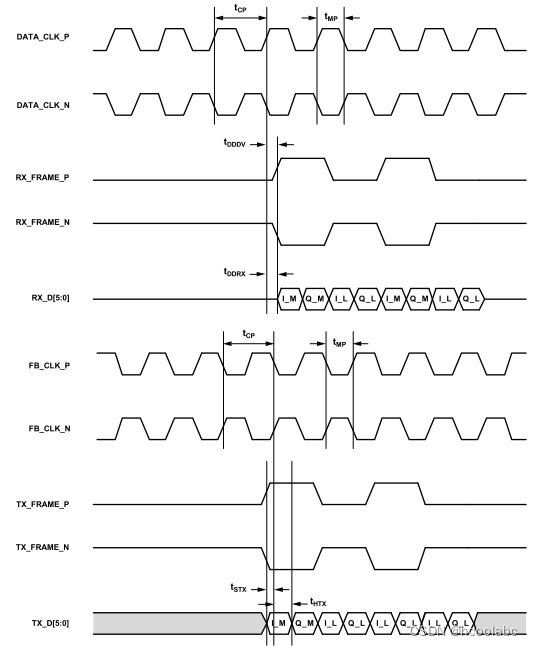

发送数据(Tx_D[5:0])、FB_CLK和Tx_FRAME由BBP驱动,因此FB_CLK、Tx_D[5:0]和Tx_FRAME之间的建立和保持时间允许AD9361使用FB_CLK捕获Tx_D[5:0]和Tx_FRAME。Tx_D[5:0] 总线上的数据样本由Tx_FRAME信号成帧,如时序图所示。传输数据样本以二进制补码格式传输,每个数据包中的第一个 6 bit包含 MSB,第二个 6 bit包含 LSB。最大值是0x7FF,第一个6bit是0x1F,第二个6bit是0x3F,最小值是0x800,第一个6bit是0x20,第二个6bit是0x00。Tx_D[5]是每个6bit中最高有效位,Tx_D[0]是最低有效位。

接收数据(Rx_D[5:0])、DATA_CLK和Rx_FRAME由AD9361驱动,因此DATA_CLK、Rx_D[5:0]和Rx_FRAME之间的建立和保持时间允许BBP使用DATA_CLK捕获Rx_D[5:0]和Rx_FRAME。

Rx_D[5:0] 总线上的数据样本由Rx_FRAME信号成帧,如时序图所示。接收数据样本以二进制补码格式传输,每个数据包中的第一个 6 bit包含 MSB,第二个 6 bit包含 LSB。最大值是0x7FF,第一个6bit是0x1F,第二个6bit是0x3F,最小值是0x800,第一个6bit是0x20,第二个6bit是0x00。Tx_D[5]是每个6bit中最高有效位,Tx_D[0]是最低有效位。

请注意,与CMOS模式一样,FB_CLK必须从DATA_CLK产生,以便保持相同的频率和占空比。两个时钟信号之间没有相位关系要求。

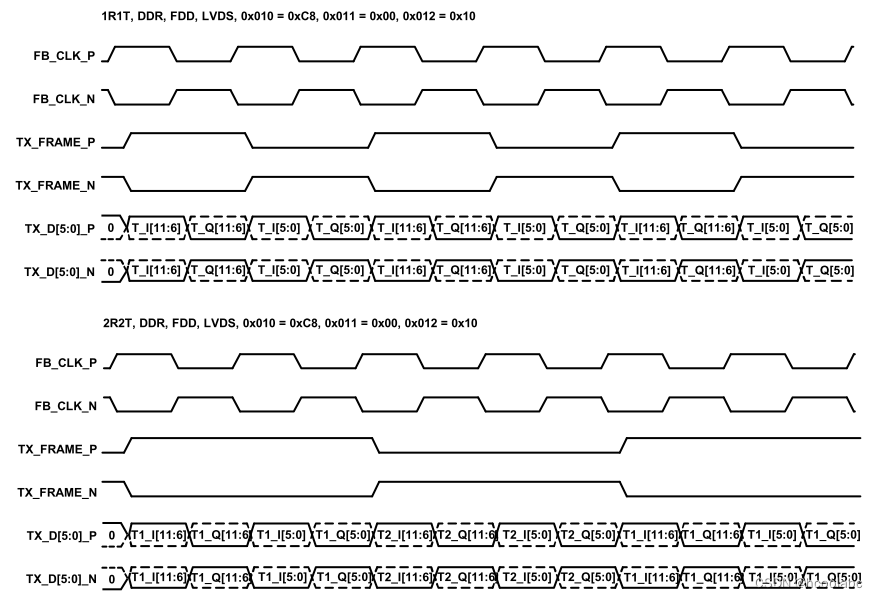

如前所述,I 和 Q 数据样本在每个数据总线上是时间交错的。对于 1R1T 系统,I 和 Q 采样数据以 4 路交错方式传输:

IMSB , QMSB, ILSB, QLSB, …

在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换重合。当启用 50% 占空比成帧时,I MSB 和 Q MSB 均处于高电平状态,I LSB 和 Q LSB 均处于低电平状态。然后,这些信号再次以I MSB切换为高电平,以指示新帧的开始。

对于 2R2T 系统,来自 RF 路径 1 和 2 的 I 和 Q 样本以 8 路交错方式传输:

I1MSB, Q1MSB, I1LSB, Q1LSB, I2MSB, Q2MSB, I2LSB, Q2LSB, …

在这种情况下,Tx_FRAME和Rx_FRAME信号与数据切换重合。每个都处于 I1MSB 的高电平状态,

Q1MSB、I1LSB、Q1LSB 和 I2MSB、Q2MSB、I 2LSB 和 Q2LSB 的低电平状态

启用 50% 占空比成帧时。然后,这些信号再次切换为高电平,并带有 IAMSB,以指示新帧的开始。

对于具有 2R1T 或 1R2T 配置的系统,时钟频率、总线传输速率和采样周期以及数据捕获时序与为 2R2T 系统配置的时钟频率相同。

但是,在仅使用单个通道的路径中,每个数据组中禁用通道的 I-Q 对未使用。AD9361忽略这些未使用的插槽。例如,对于使用 Tx 通道 1 的 2R1T 系统,发射突发将有四个未使用的时隙:

I 1MSB, Q 1MSB , I1LSB , Q1LSB,X,X,X,X,X , …

在这种情况下,Tx_FRAME和Rx_FRAME与数据切换一致,I1MSB、Q1MSB、I1LSB、Q1LSB为高电平,未使用时隙为低电平。然后,这些信号通过I1MSB再次切换为高电平,以指示新帧的开始。BBP 可能会用任意数据值填充未使用的 X 通道。这些值可以是常量值,也可以重复前面的数据采样值,以降低总线开关系数,从而降低功耗。

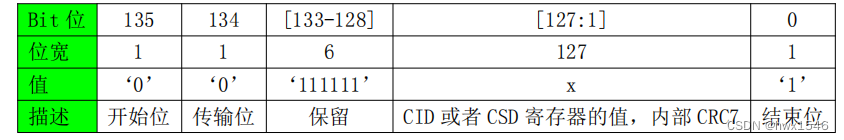

二、数据通路功能时序 (LVDS)

下图时序图说明了双端口FDD LVDS模式下总线信号之间的关系。时序图中的差分数据用实线和虚线绘制,以说明数据线的差分性质。正腿的实线与差分对的负腿的实线匹配,正腿对的虚线与负腿的虚线匹配。请注意,由于 2R1T 和 1R2T 系统遵循 2R2T 时序图,因此省略了它们。

注意:

LVDS 模式不支持以下位配置:

交换端口 — 在LVDS模式下,P0为Tx,P1为Rx。无法更改此配置。

单端口模式 — 两个端口均在LVDS模式下启用。

FDD全端口 — LVDS不支持。

FDD Alt Word Order - LVDS不支持。

FDD 交换位 — LVDS 不支持。

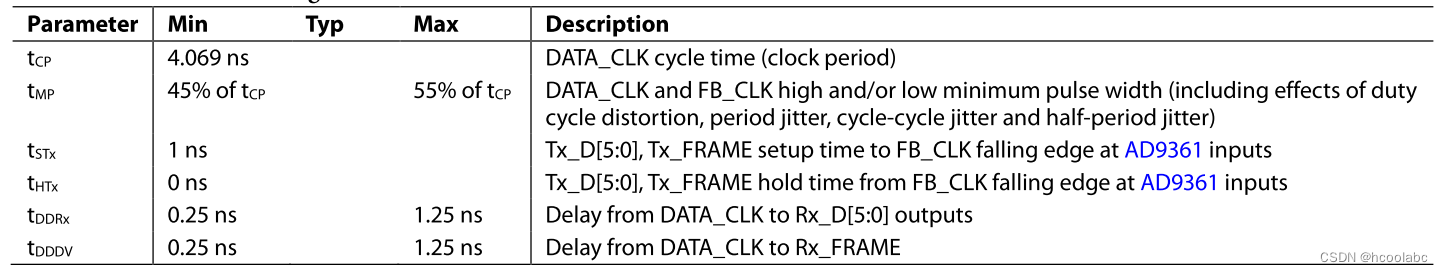

三、数据路径时序参数(LVDS)

DATA PATH TIMING PARAMETERS

下表列出了LVDS数据总线的时序约束。

参考源文件 :《UG-570 AD9361 Reference Manual 》

参考源文件 :《UG-671 AD9361 Register Map Reference Manual》

![[ASP]青辰网络考试管理系统NES X3.5](https://img-blog.csdnimg.cn/96f81143a4454aea8a37adcedd40540a.png)