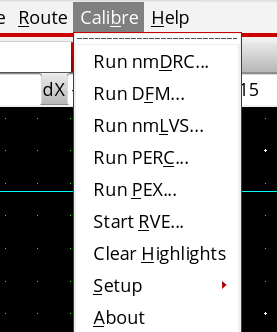

Mentor calibre

软件

版图物理验证主要包括:

①设计规则检查(

DRC

)

②电学规则检查(

ERC

)

③版图与电路图一致性检查

( LVS)

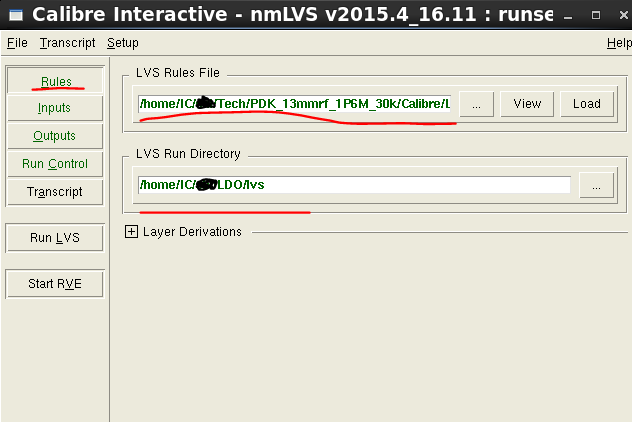

LVS

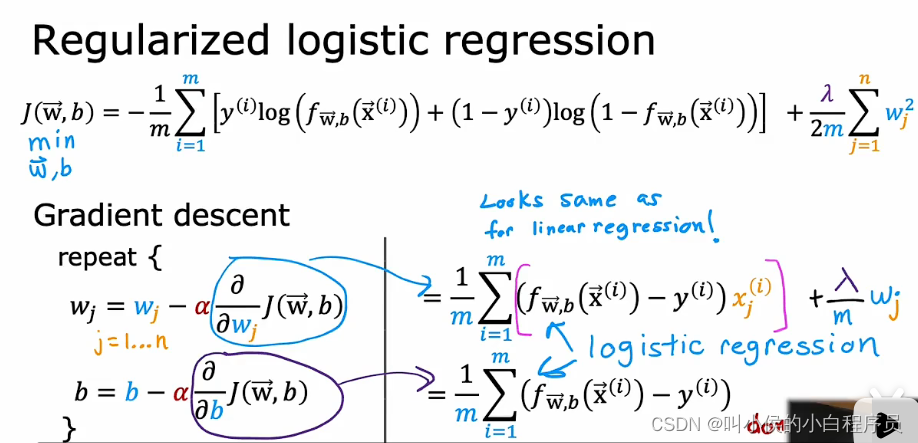

版图与电路图一致性检查 ( Layout Versus Schematic, LVS) 的目的在于检查人工绘制的版图是否和电路结构相符。

在 Mentor calibre LVS 的基本流程中,首先根据元器件定义规则对元器件及连接关系从版图 (Layout ) 中提取相应的网表 ( Layout Netlist), 其次读入电路网表 ( Source Netlist), 再根据一定的算法对从版图中提取的网表与电路网表进行比对,最后输出比对结果 ( LVS Compare Output )。

LVS 检查主要包括元器件属性、元器件尺寸及连接关系等一致性 比对检查,同时还包括电学规则检查(ERC ) 等。

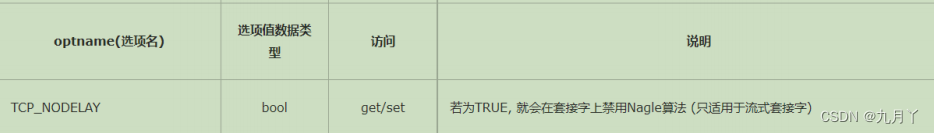

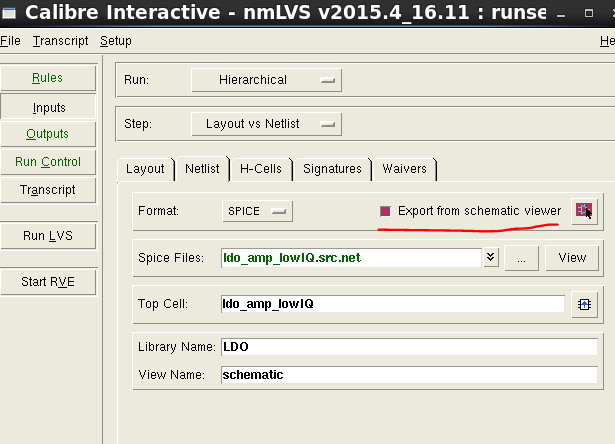

在 Calibre LVS 主界面中的工具选项栏中,

红色

字

栏代表对应的选项尚未填写完整,

绿色

字栏代表对应的选项已经填写完整。

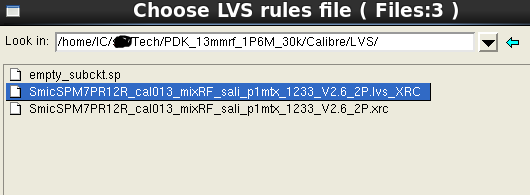

lvs rule file

选择 LVS 规则文件的位置

lvs run directory

选择 Calibre LVS的执行目录(lvs过程中会产生很多过程文件,最好建一个文件夹存放,便于删除)

DRC过程同理,此处不再赘述。