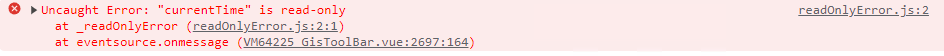

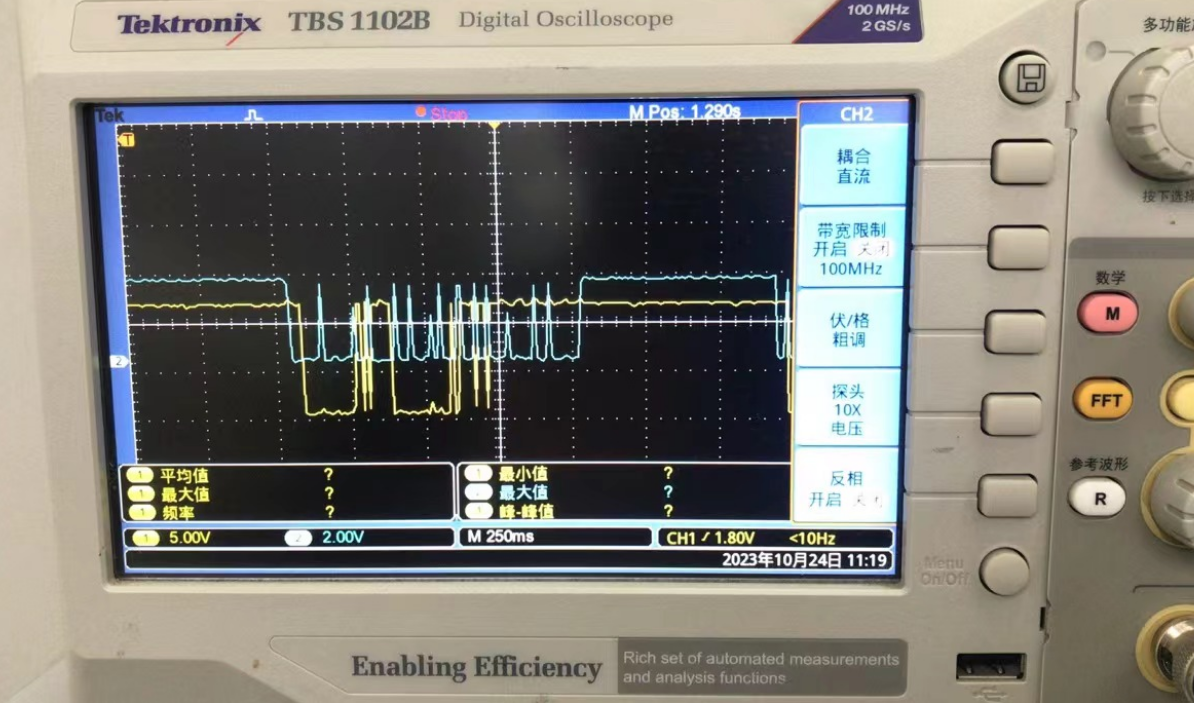

问题描述:MAX3232串口通讯芯片的输出引脚上存在干扰电平,通过示波器可以看到干扰电平,PC端的串口程序表现为接收到乱码。如下图,环回测试中发了一串字符数据AT+CIPSEND后,除了收到环回的AT+CIPSEND字符外,还有一大堆乱数据。

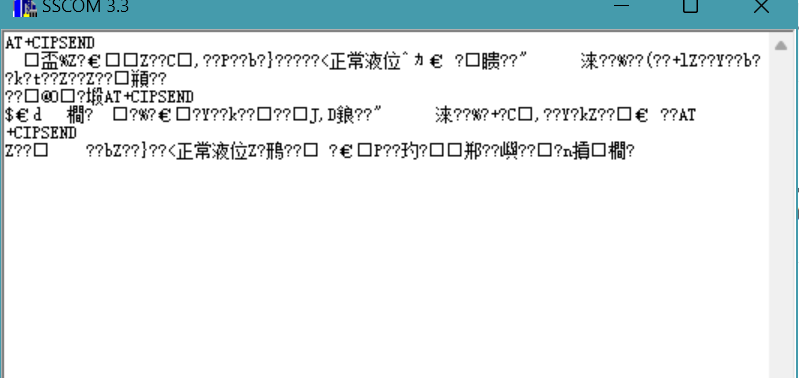

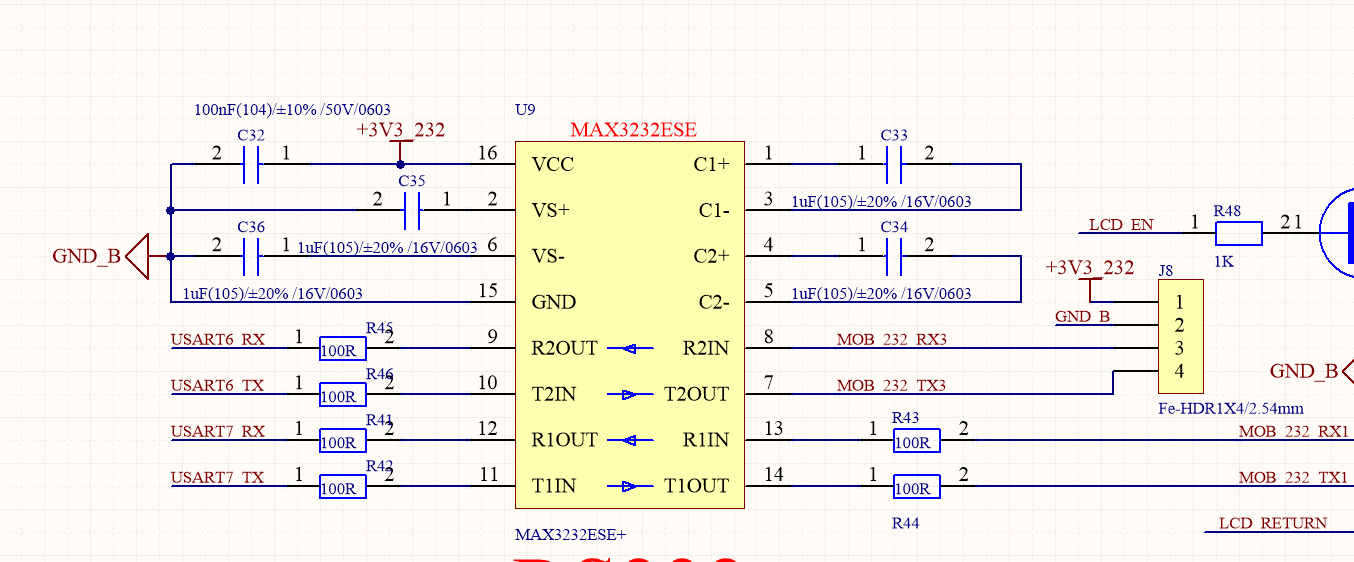

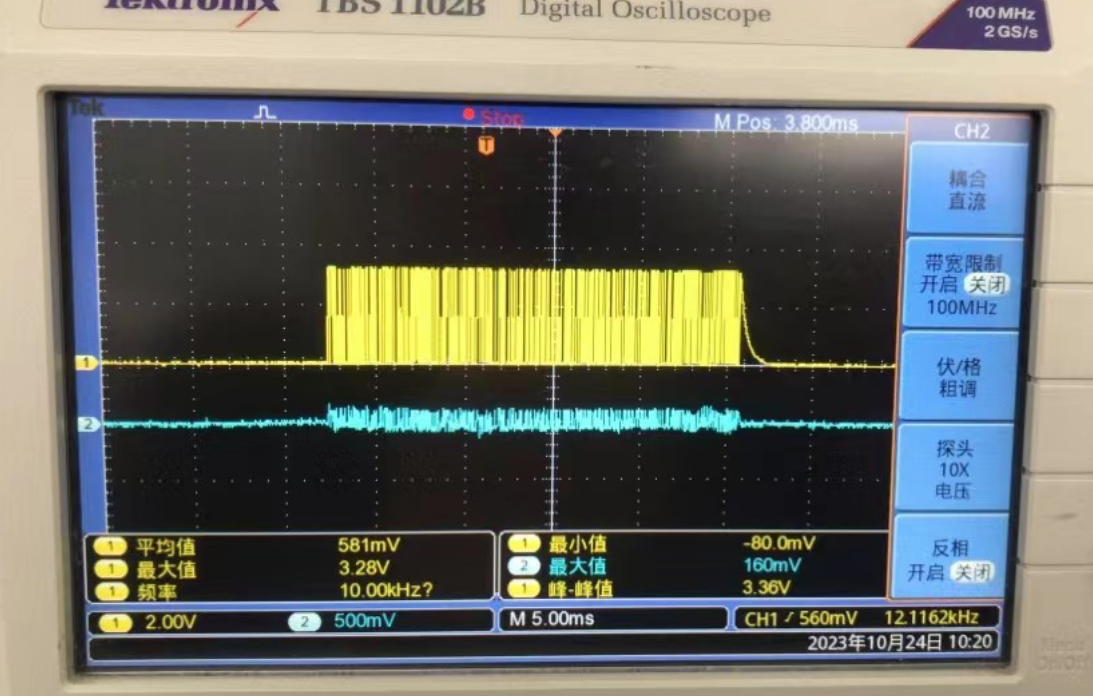

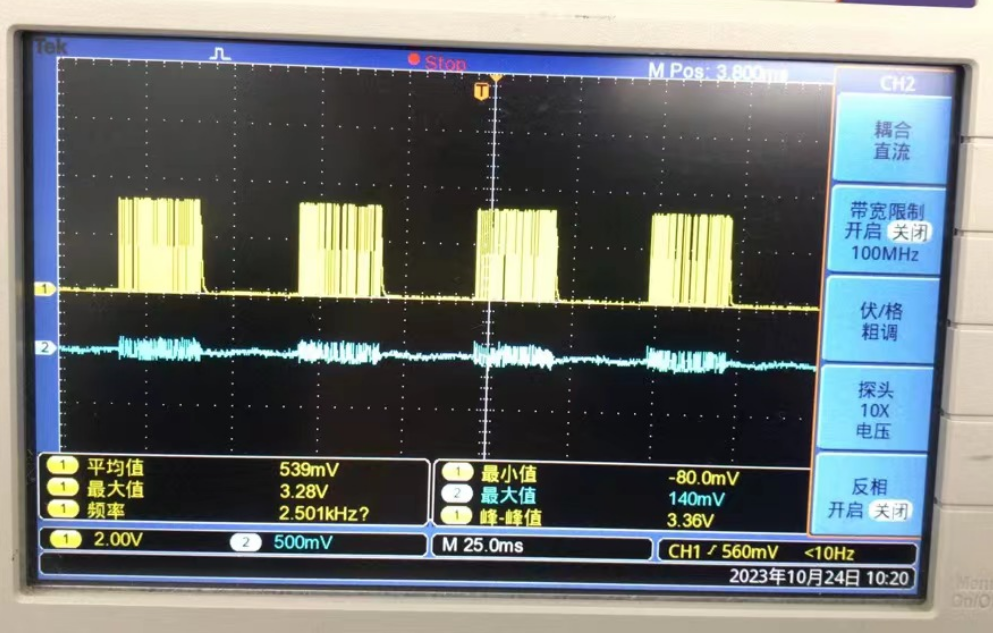

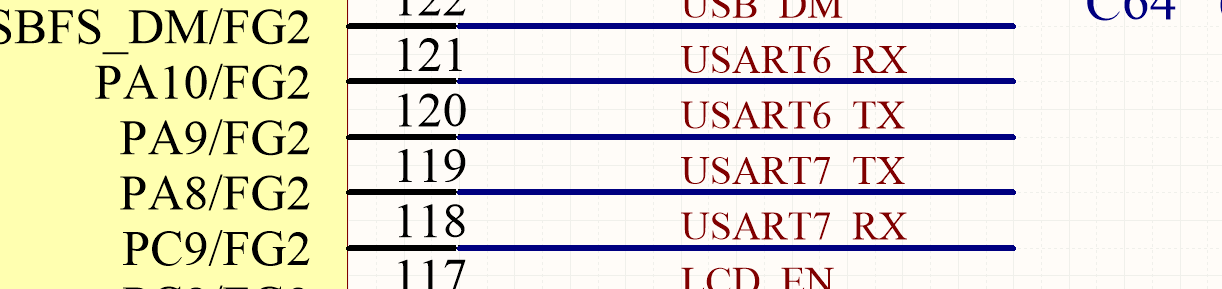

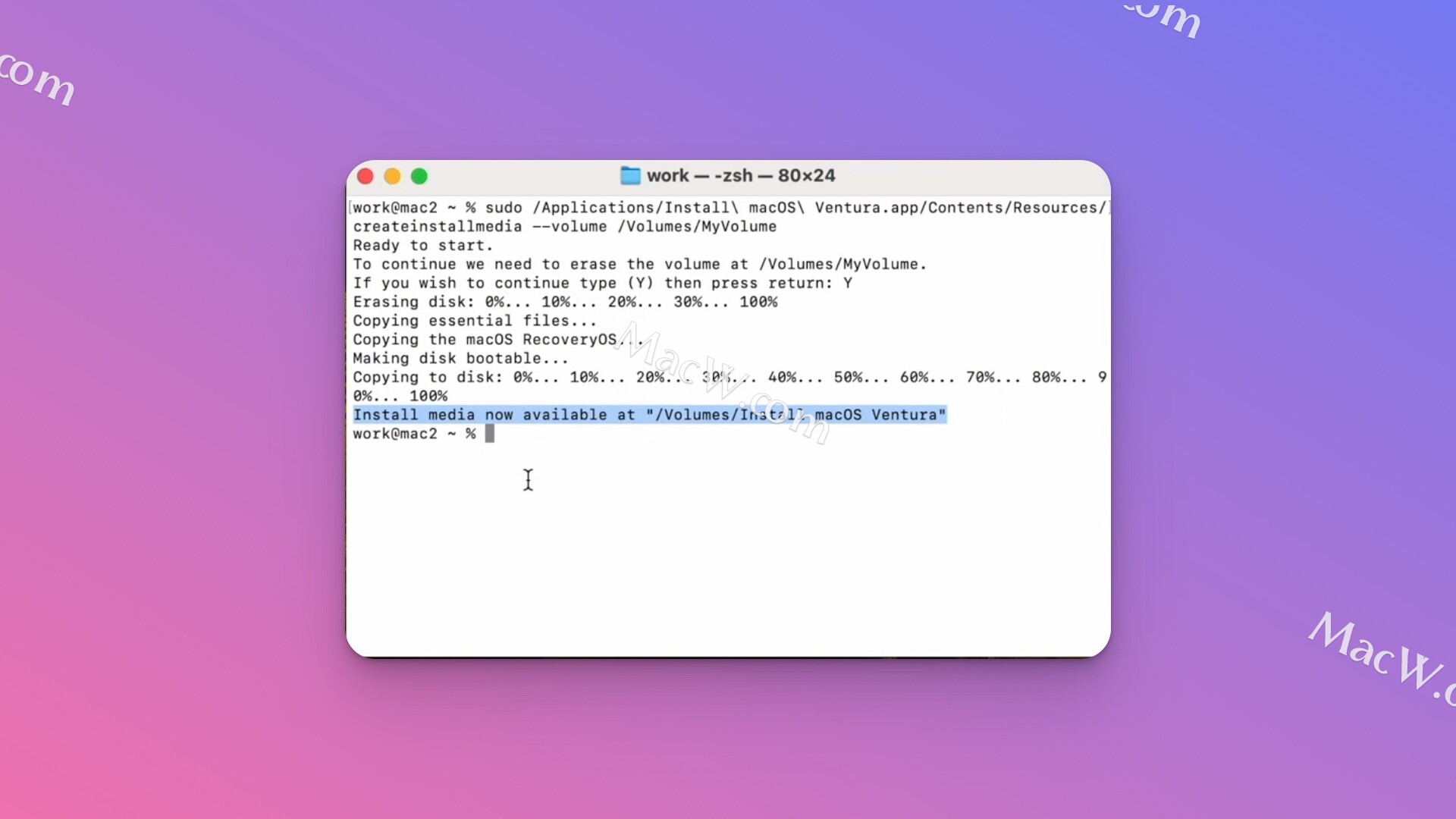

问题分析:经过分析发现,程序中关闭UART7串口的时候,USART6能够正常通讯,说明程序基本没有问题。USART6上收到了UART7上发出的数据,因为UART7是一直在通讯的一个串口,USART7_TX引脚上一直有数据发送即其引脚上存在变化的电流,会产生变化的磁场,而pcb布线上,USART7_TX和USART6_TX是相邻布线的,因此怀疑USART7_TX上的信号通过电磁场干扰到了USART6_TX,用示波器查看两个TX引脚上的波形:

问题分析:经过分析发现,程序中关闭UART7串口的时候,USART6能够正常通讯,说明程序基本没有问题。USART6上收到了UART7上发出的数据,因为UART7是一直在通讯的一个串口,USART7_TX引脚上一直有数据发送即其引脚上存在变化的电流,会产生变化的磁场,而pcb布线上,USART7_TX和USART6_TX是相邻布线的,因此怀疑USART7_TX上的信号通过电磁场干扰到了USART6_TX,用示波器查看两个TX引脚上的波形:

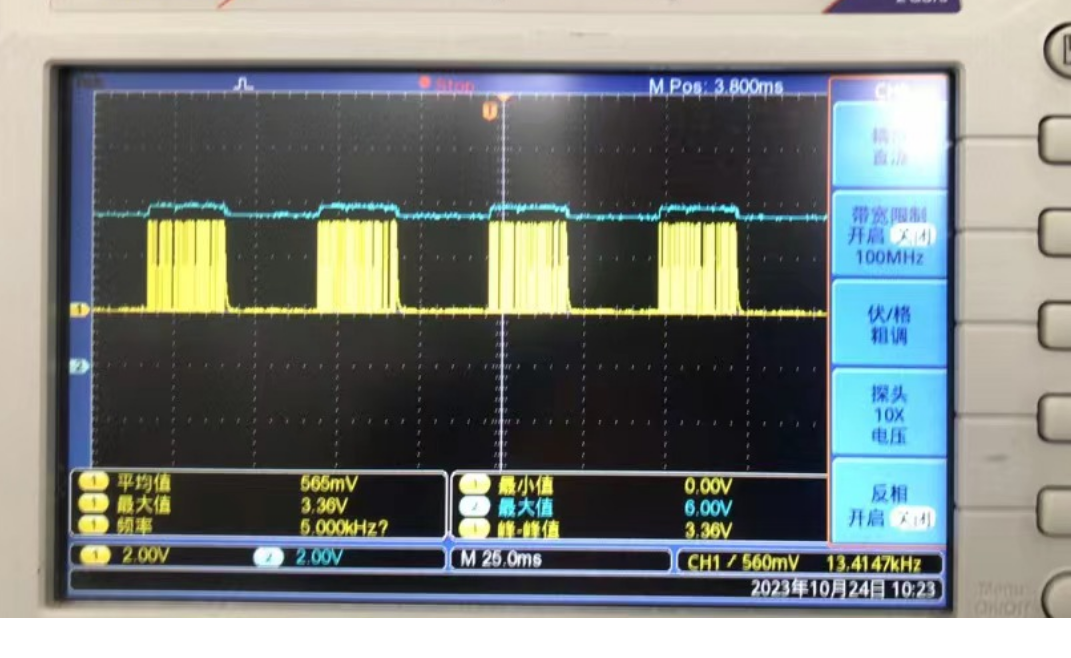

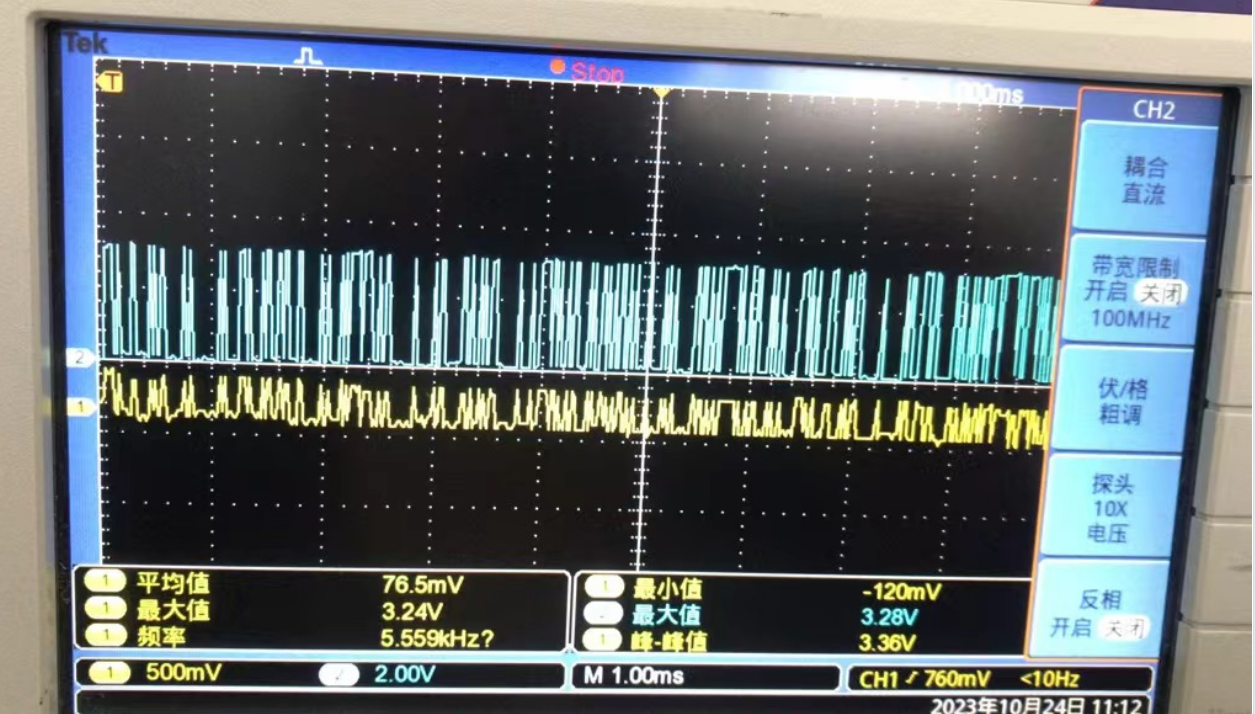

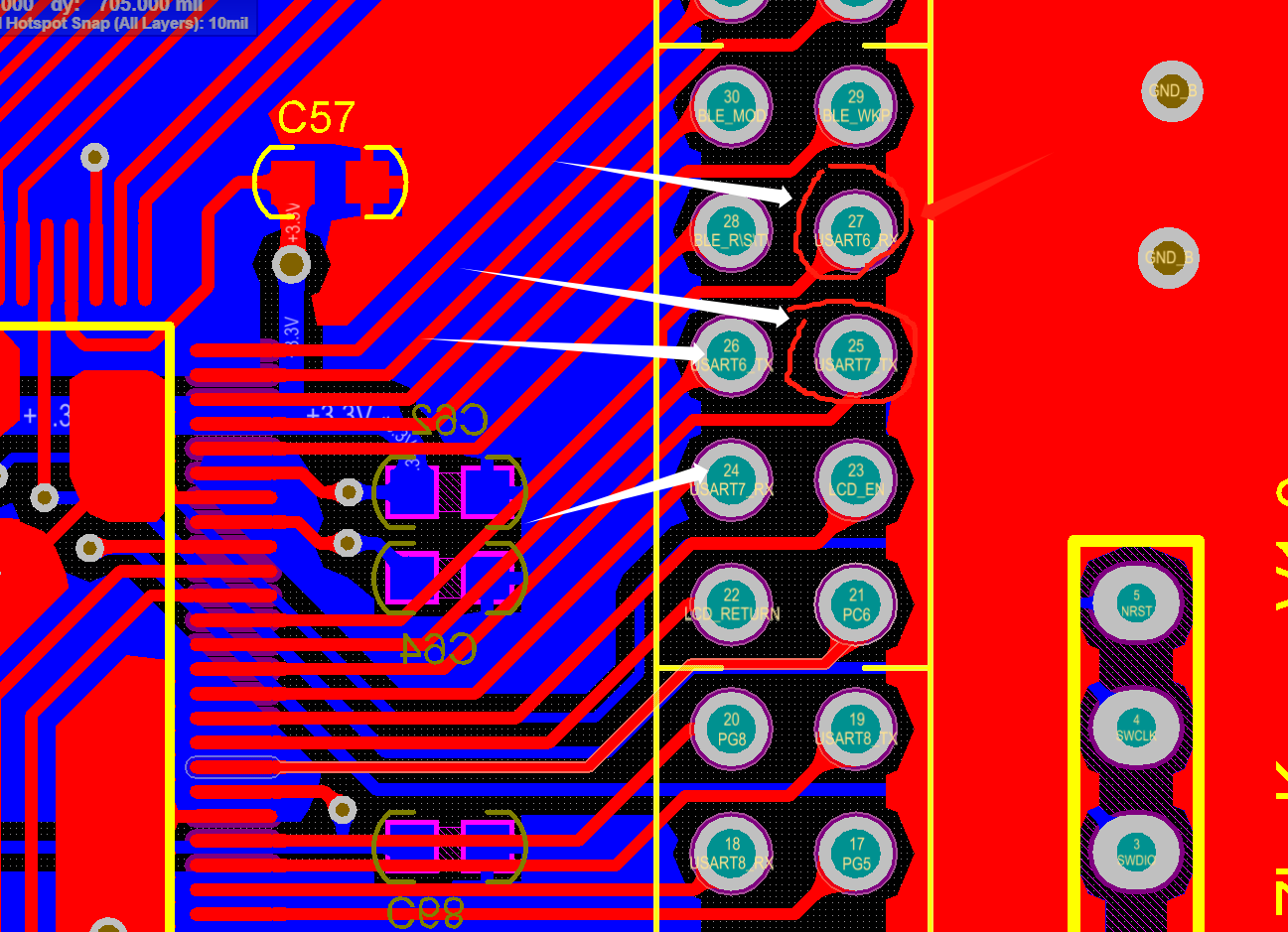

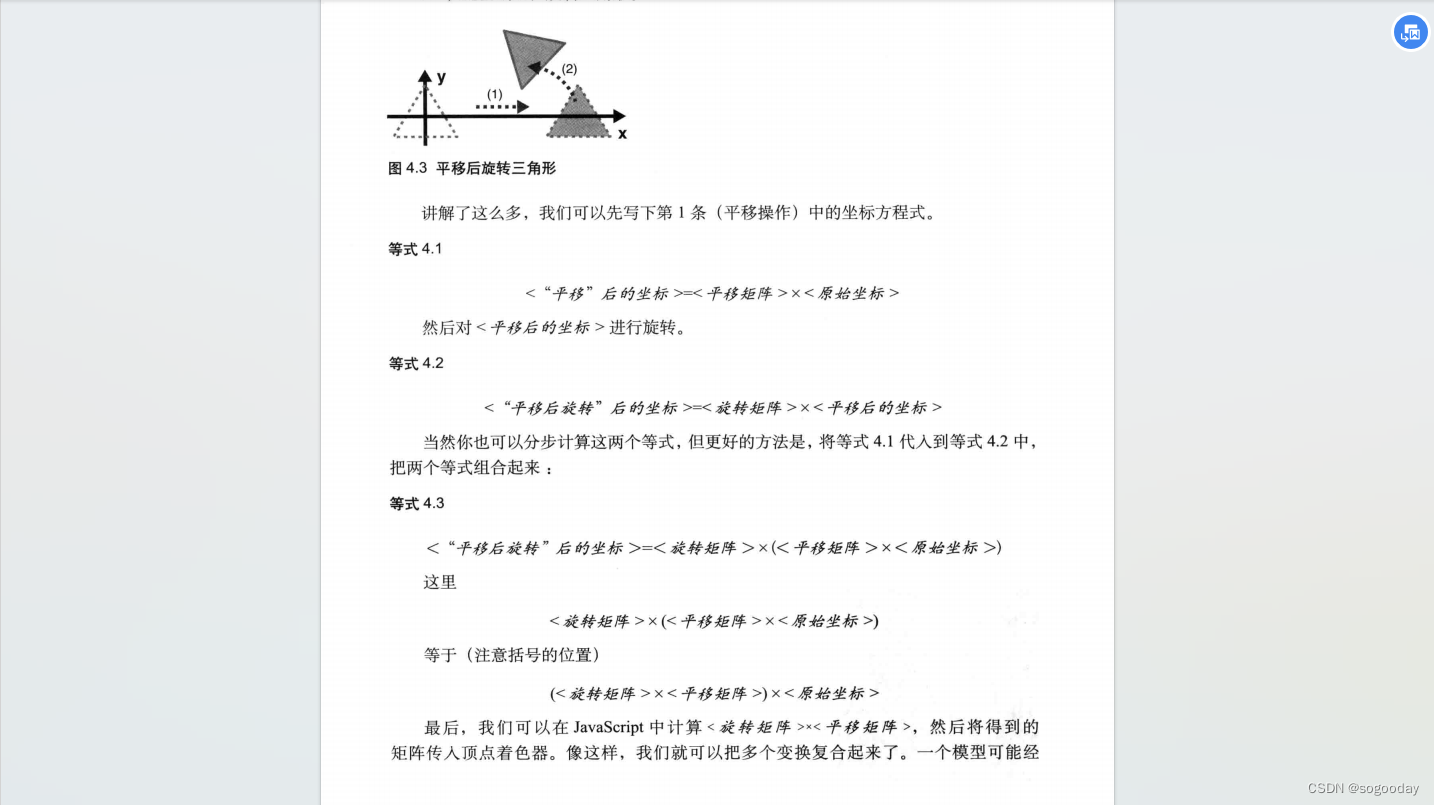

这4张图是UART6_TX引脚上同原理图设计中串联100欧电阻时抓取的,可以看到黄色的UART7_TX上发送数据时UART6_TX上感应出相同频率的干扰信号,从第4张图可以看出TTL引脚上的干扰电平大概有300~400mv,第3张图蓝色是同PC串口相连接的MOB_232_TX3上的波形,所以PC端串口测试程序会收到干扰数据就是这样来的。

后两种图是将UART6_TX引脚上串联的100欧电阻换为0欧电阻,UART7_TX上任串100欧电阻,可以看到UART6_TX的干扰电平明显变大,所以设计中在TTL电平段通讯引脚上串小电阻的意义就在这里,可以减弱相邻通讯线路信号的干扰。

后续改进:原理图设计中和PCB走线过程中尽量保持TX信号线之间的距离,TX与TX引脚之间不要设计在一起,可以RX、TX、RX、TX交替分配管脚。 这种设计不好,能分开远一点最好。

这种设计不好,能分开远一点最好。

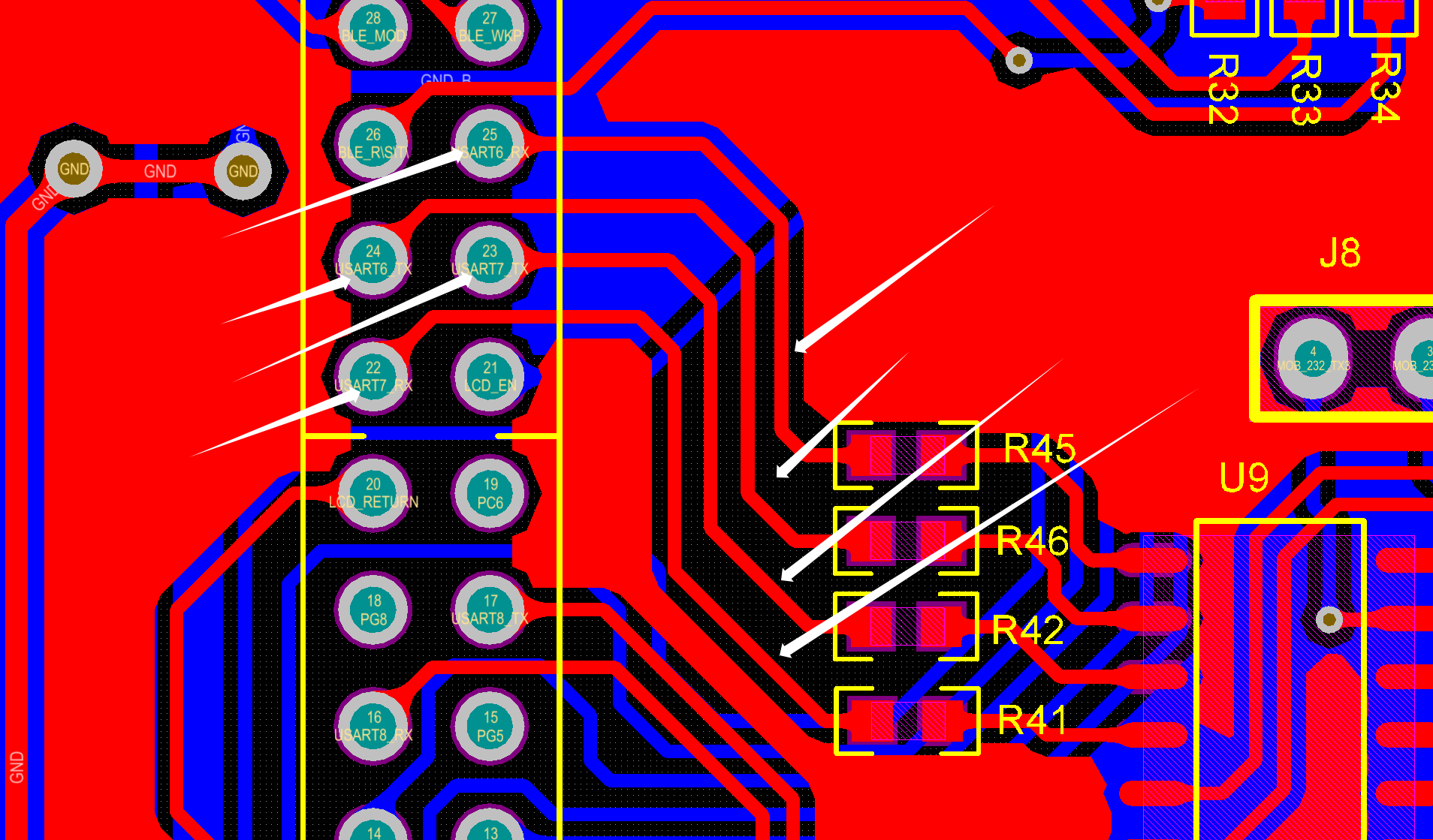

这种pcb走线也可以将TX、RX在顶层和底层分开走线,这样可以防止干扰。

这种pcb走线也可以将TX、RX在顶层和底层分开走线,这样可以防止干扰。

![[数据分析与可视化] 基于Python绘制简单动图](https://img-blog.csdnimg.cn/img_convert/109d834890f04c38ce7e4597759ea39a.gif)