名称:Quartus调用FIFO-IP核,完成数据的求和

软件:Quartus

语言:Verilog

代码功能:

题目:FIFO-IP核的调用

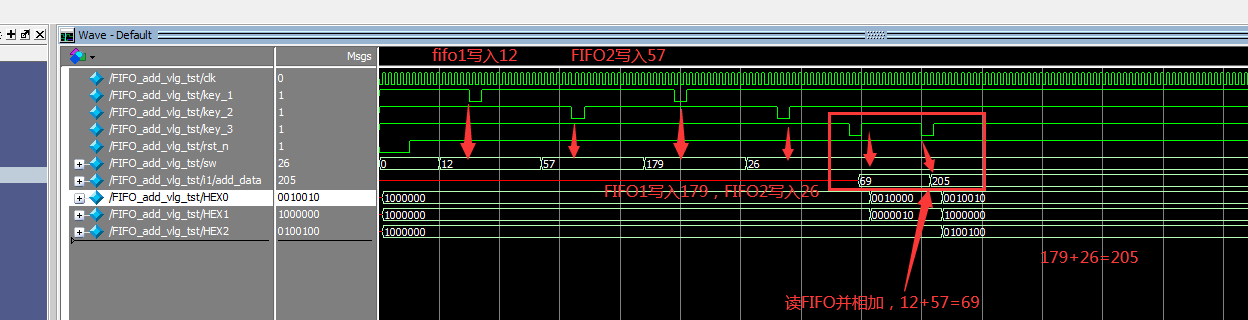

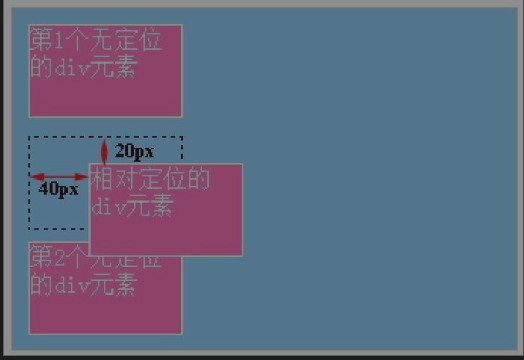

主要内容:调用两个FIFO-IP核,完成2行数据的求和

技术参数:两行数据值的输入可通过拨码开关实现,分别存储于2个FIFO,依次读取2个FIFO的数据求和,并将结果通过数码管显示

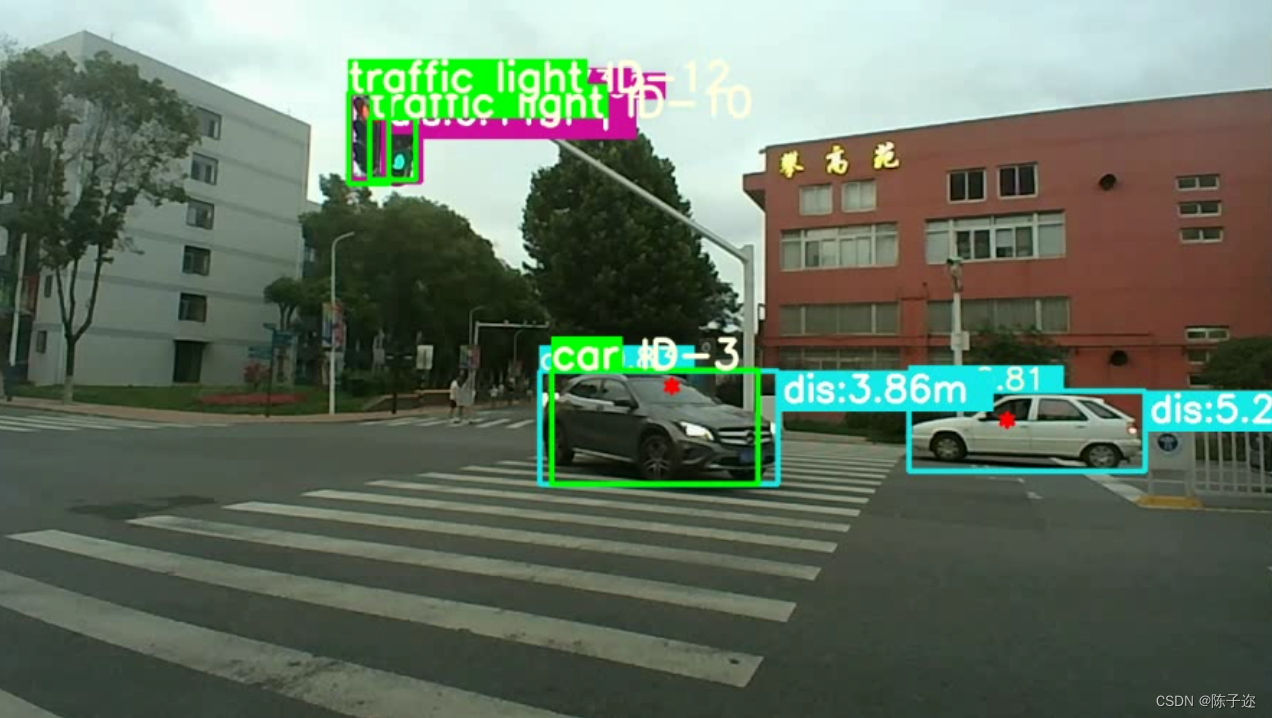

本代码已在DE1-SOC开发板验证,开发板照片:

板子.jpg

演示视频:http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=205

FPGA代码资源下载网:hdlcode.com

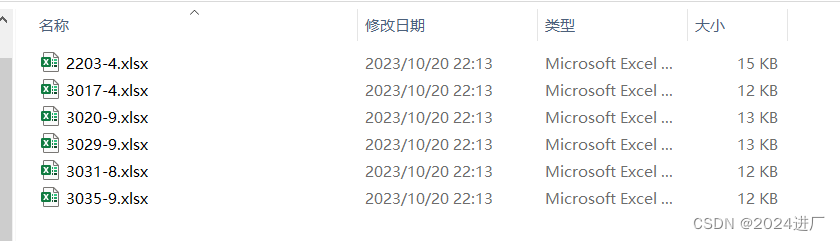

代码下载:

FIFO-IP核的调用 主要内容:调用两个FIFO-IP核,完成2行数据的求和 技术参数:两行数据值的输入可通过拨码开关实现,分别存储于2个FIFO,依次读取2个FIFO的数据求和,并将结果通过数码管显示名称:Quartus调用FIFO-IP核,完成数据的求和(代码在文末付费下载)软件:Quartus语言:Verilog代码功能:题目:FIFO-IP核的调用主要内容:调用两个FIFO-IP核,完成2行数据的求和技术参数:两行数据值的输入可通过拨码开关实现,分别存储于2个FIFO,依次读取2个FIFO的数据求和,并将结果通过数码管显示本代码已在DE1-SOC开发板验证,开发板照片:板子.jpg演示视![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=205

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=205

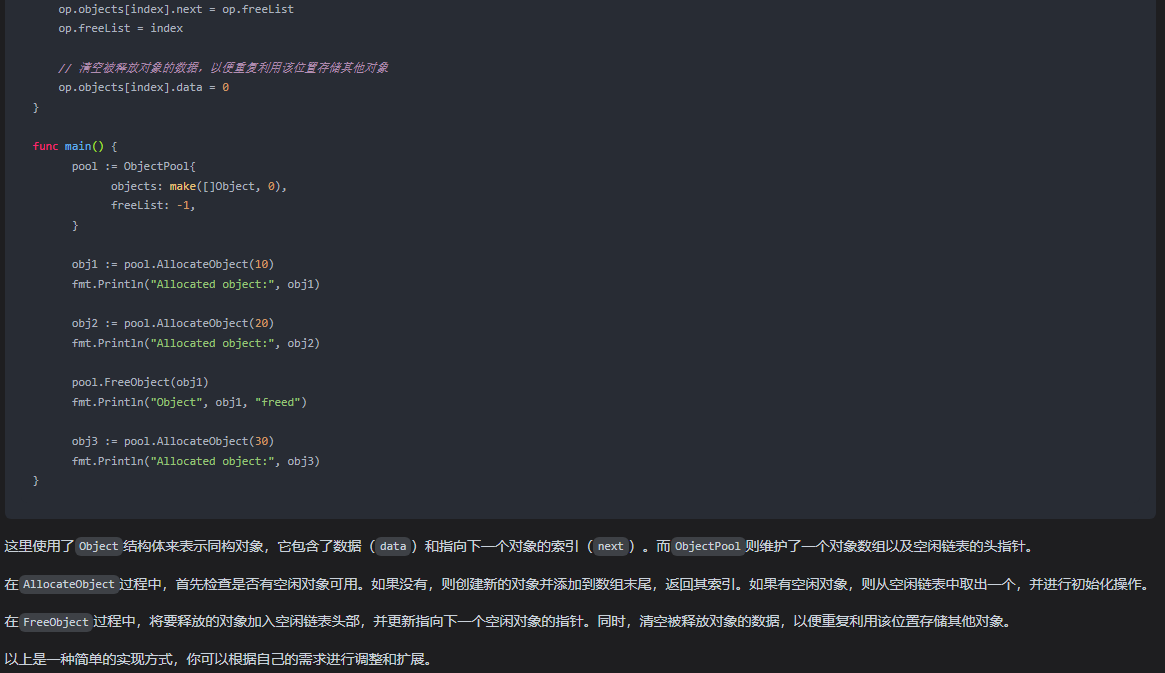

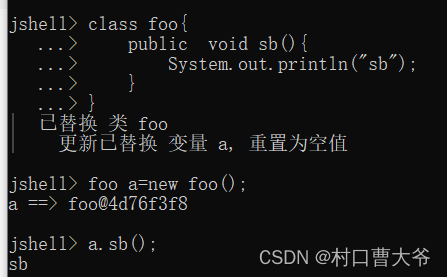

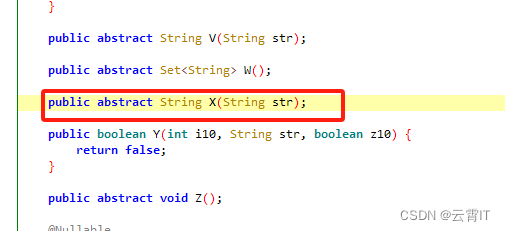

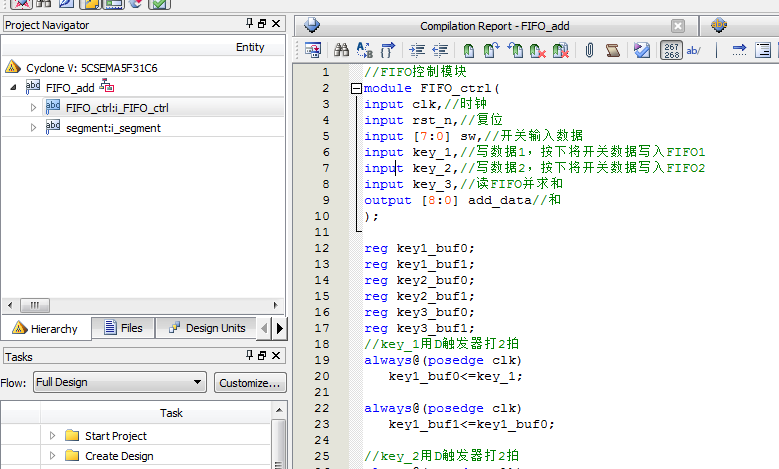

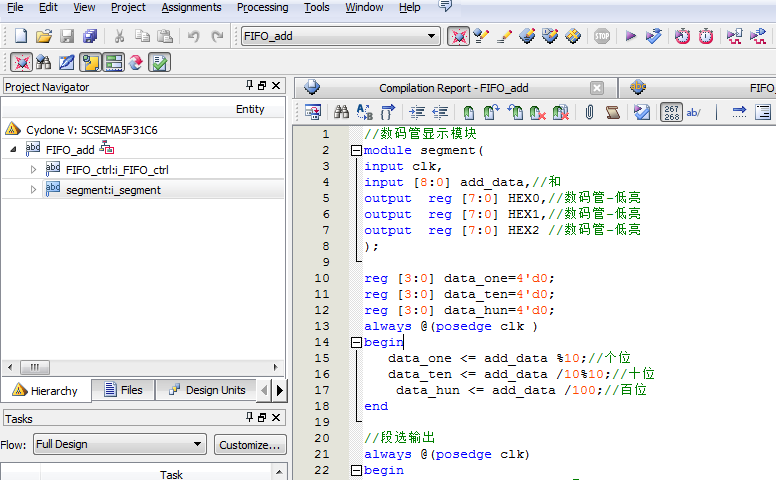

部分代码展示

//调用两个FIFO-IP核,完成2行数据的求和 //技术参数:两行数据值的输入可通过拨码开关实现, //分别存储于2个FIFO,依次读取2个FIFO的数据求和, //并将结果通过数码管显示 module FIFO_add( input clk,//时钟 input rst_n,//复位 input [7:0] sw,//开关输入数据 input key_1,//写数据1,按下将开关数据写入FIFO1 input key_2,//写数据2,按下将开关数据写入FIFO2 input key_3,//读FIFO并求和 output [6:0] HEX0,//数码管0 output [6:0] HEX1, //数码管1 output [6:0] HEX2 //数码管2 ); wire [8:0] add_data;//和 //FIFO控制模块 FIFO_ctrl i_FIFO_ctrl( . clk(clk),//时钟 . rst_n(rst_n),//复位 . sw(sw),//开关输入数据 . key_1(key_1),//写数据1,按下将开关数据写入FIFO1 . key_2(key_2),//写数据2,按下将开关数据写入FIFO2 . key_3(key_3),//读FIFO并求和 . add_data(add_data)//和 ); //数码管显示模块 segment i_segment( . clk(clk), . add_data(add_data),//和 . HEX0(HEX0),//数码管-低亮 . HEX1(HEX1),//数码管-低亮 . HEX2(HEX2)//数码管-低亮 ); endmodule //数码管显示模块 module segment( input clk, input [8:0] add_data,//和 output reg [7:0] HEX0,//数码管-低亮 output reg [7:0] HEX1,//数码管-低亮 output reg [7:0] HEX2 //数码管-低亮 ); reg [3:0] data_one=4'd0; reg [3:0] data_ten=4'd0; reg [3:0] data_hun=4'd0; always @(posedge clk ) begin data_one <= add_data %10;//个位 data_ten <= add_data /10%10;//十位 data_hun <= add_data /100;//百位 end //段选输出 always @(posedge clk) begin case (data_one) //显示码 8'd0: HEX0<= 8'b1100_0000; 8'd1: HEX0<= 8'b1111_1001; 8'd2: HEX0<= 8'b1010_0100; 8'd3: HEX0<= 8'b1011_0000; 8'd4: HEX0<= 8'b1001_1001; 8'd5: HEX0<= 8'b1001_0010; 8'd6: HEX0<= 8'b1000_0010; 8'd7:

设计文档:

设计文档.doc

1. 工程文件

2. 程序文件

3. 程序编译

4. RTL图

5. 管脚分配

6. Testbench

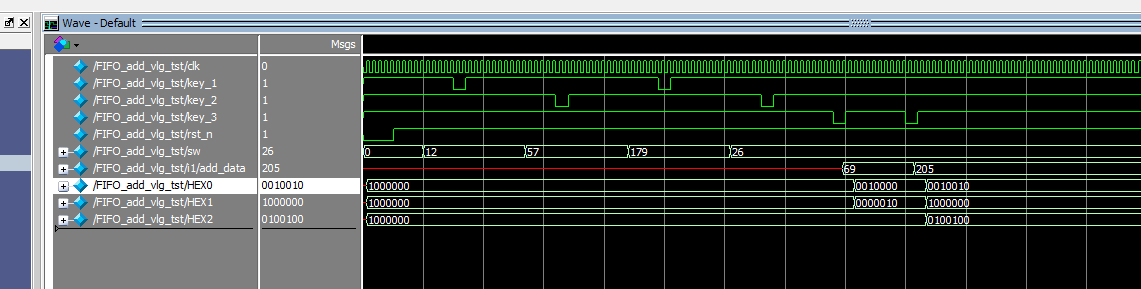

7. 仿真图