相关阅读

数字IC前端![]() https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12173698.html?spm=1001.2014.3001.5482

门控时钟(clock gating)技术作为一种传统的动态低功耗技术被广泛应用于现在的数字集成电路设计中,这是RTL级别的低功耗优化技术。门控时钟即使用逻辑门电路控制时钟的开启和关闭,当芯片上某一模块的功能不需要工作时,如芯片上的USB模块或SPI接口模块没有使用时,可以使用门控信号停止这些模块的时钟,有效降低了时钟树上的功耗和信号翻转率。

图1所示的为一种简单的门控时钟结构,它由一个与非门和一个非门组成,甚至可以仅仅引入一个与门。其设计开销几乎可以可忽略不计,可以说是门控时钟的原型。

图1 简单的门控时钟

图1 简单的门控时钟

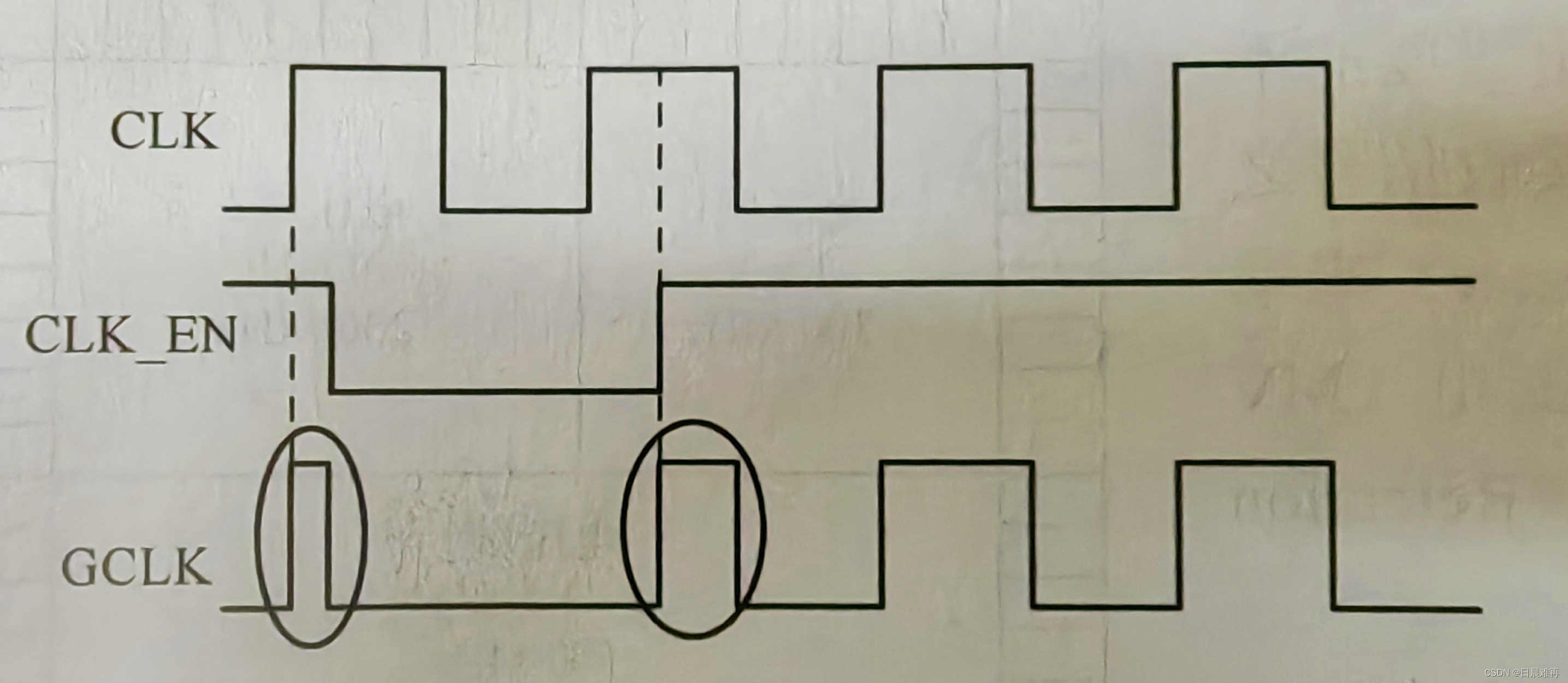

但是从信号完整性角度来看,这种设计结构对于大规模的数字电路实现有一个极大的缺陷,可能产生毛刺。在实际系统工作时,如图2所示,当源时钟CLK为高电平时,如果CLK_EN变为低电平,GCLK将立刻变为低电平,即出现了一个下降沿,这是一个毛刺信号,会影响一些使用下降沿的触发器。同样的,当源时钟CLK为高电平时,如果CLK_EN变为高电平,GCLK将立刻变为高电平,即出现了一个上升沿,这会影响一些使用上升沿的触发器。总之,这类在门控时钟上出现的毛刺,对同步电路来说是非常致命的。

图2 简单的门控时钟会产生毛刺

图2 简单的门控时钟会产生毛刺

由于上述限制,工业界广泛采用的门控电路是一种在上述简单的门控电路结构上加入了高电平锁存的锁存器,如图3所示。因为以上的毛刺都是出现在CLK为高电平时,所以思路是使用CLK的高电平锁存CLK_EN信号,这样CLK_EN在CLK高电平期间就一定是一个稳定的值(CLK_EN在CLK低电平期间没有影响,因为是相与)。

图3 使用锁存器的门控时钟

图3 使用锁存器的门控时钟

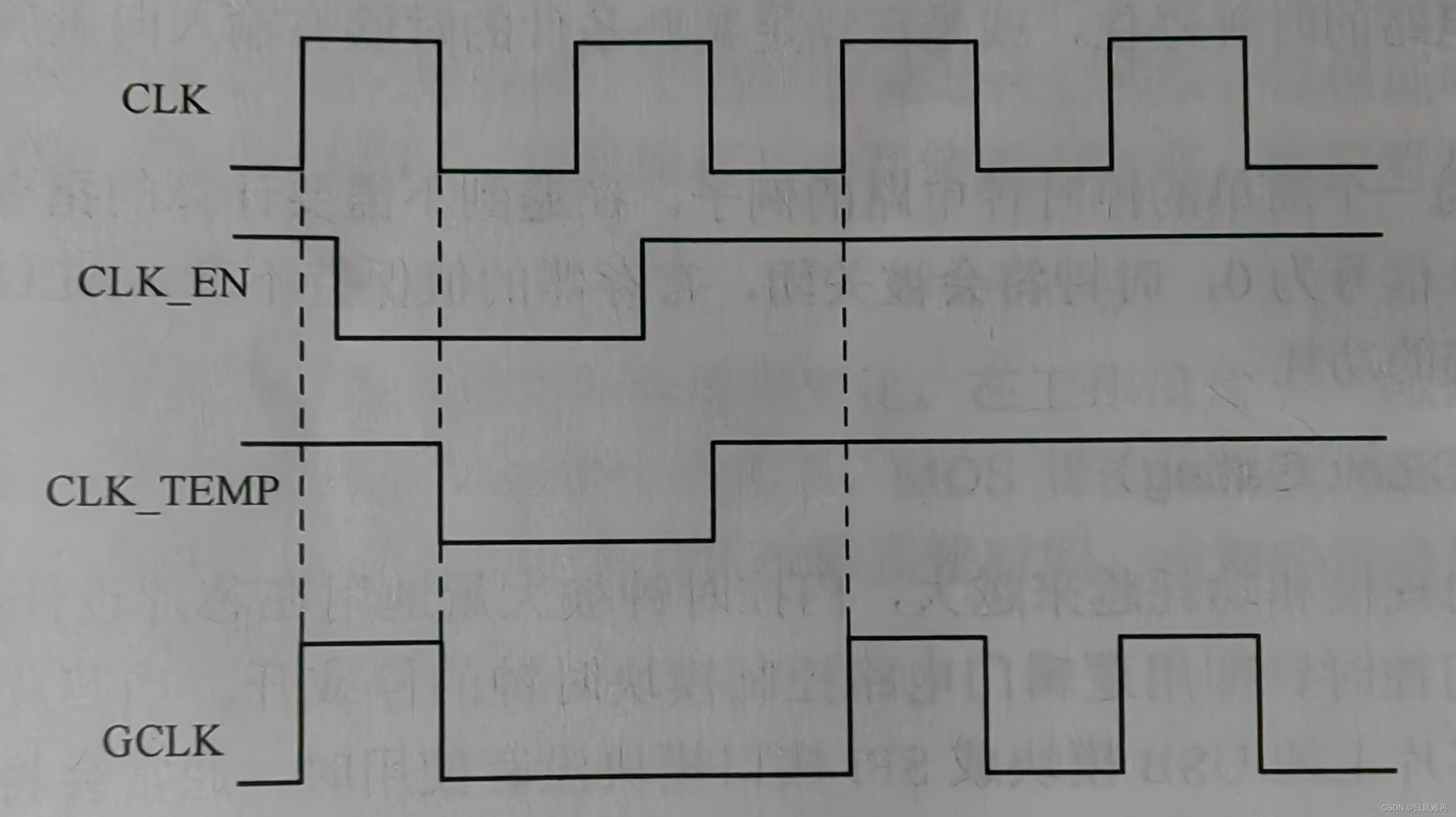

图4为带锁存器的门控时钟的工作波形,从图中可以看出,只有当CLK为低电平时,CLK_EN才能直接传到与非门的输入端,这相当于CLK_EN信号被锁存了半个周期,这样就不会有毛刺了。

图4 使用锁存器的门控时钟不会产生毛刺

图4 使用锁存器的门控时钟不会产生毛刺