减小功耗 就得减小电流 电流和CF有关( C: 电容(被门数目和布线长度影响) F:时钟频率)

方法大纲 减小功耗:1 时钟控制 2输入控制 3减小供电电压 4双沿触发器 5修改终端

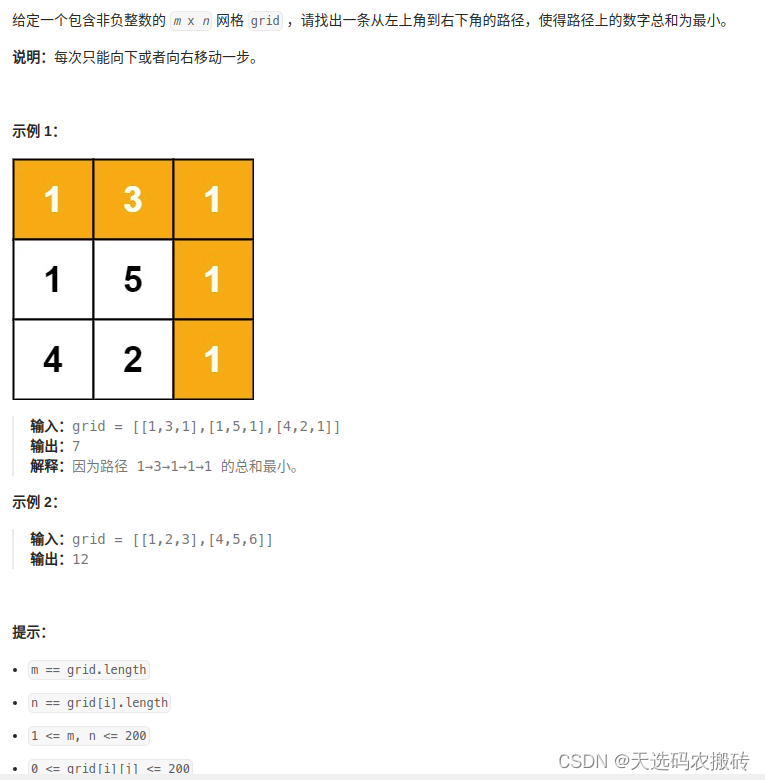

同步数字电路降低动态功耗:动态禁止在特定区域中的时钟:利用触发器的时钟使能引脚,或利用全局时钟的多路选择器。时钟使能触发器输入或全局时钟多路选择器)替代直接时钟选通(因为直接的时钟选通大多是不好的)

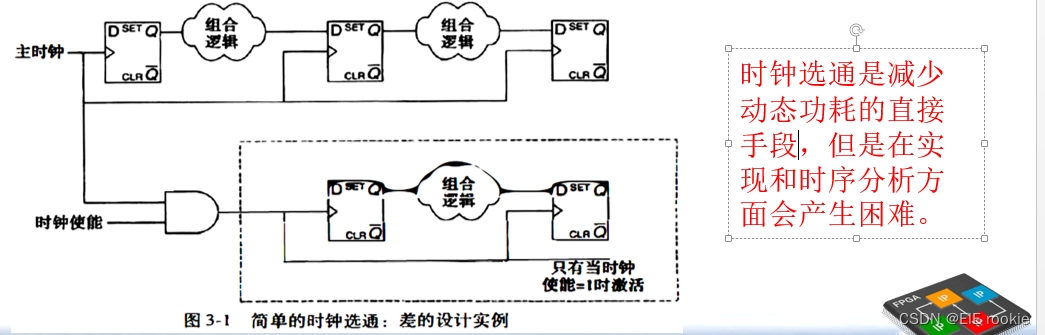

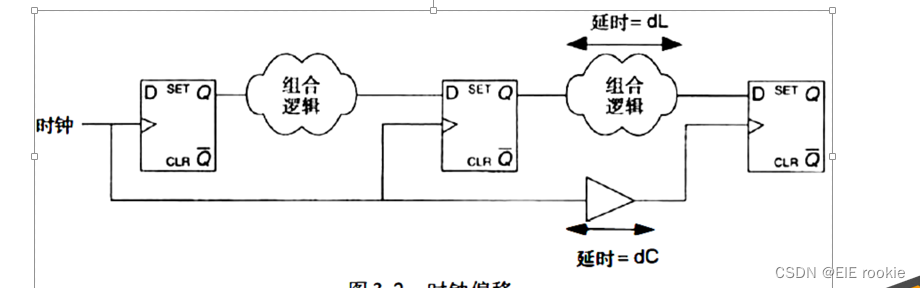

时钟树利用缓冲器使得时钟到达各个寄存器的时间差最小。

在执行时序分析时必须考虑时钟偏移。时钟偏移与时钟速度是无关的。

由于逻辑模块和布线资源的内在延时,在FPGA设计中很少出现保持冲突 ,但时钟线上过度延时仍会导致保持冲突。可通过添加时钟约束来消除冲突。\

2输入控制

为了最大限度的降低输入设备的功耗,应尽量减少驱动输入的上升和下降时间。可以瞬间切换

3降低供电电压

虽然降低供电电压通常不是期望的选择

降低FPGA电源的供电电压接近最小要求的电压,可以达到显著地节省功率。但是,降低这个电压也将减少系统的性能。(降低 但也影响性能)

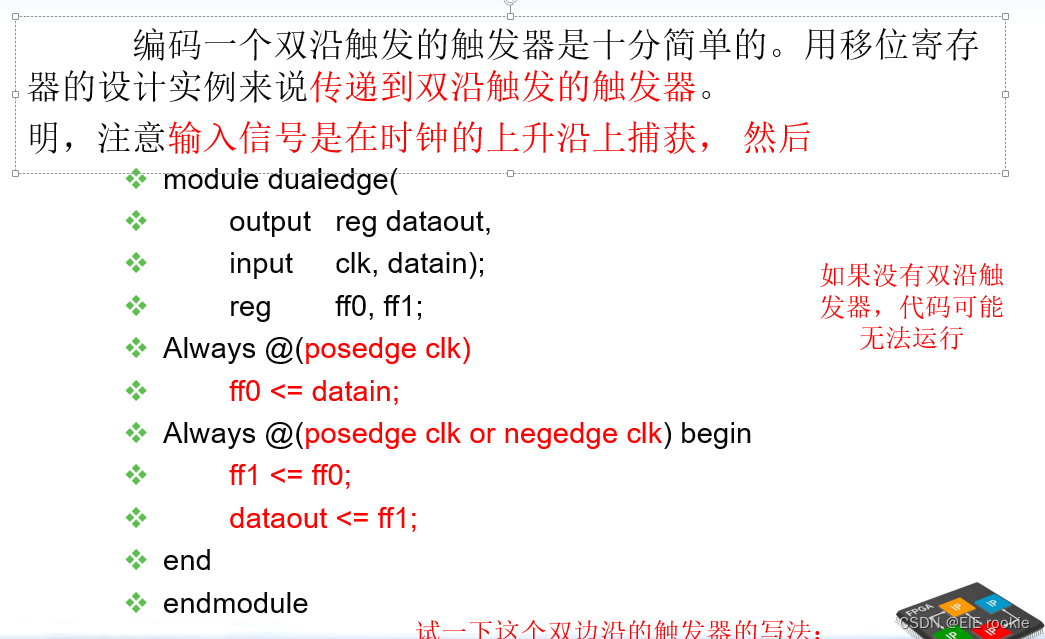

双沿触发触发器

功耗是与信号触发频率成正比,我们希望高扇出网线的每个触发功能数量要最大化.使得设计者运行的时钟频率只需达到确定程度功能和性能的频率的一半。

如果双沿触发器是无效的, 将添加多余的触发器和选通来仿真相应的功能。

修改终端

对于负载带短路终端的传输线,可采用串行端接替代并行端接

采用串行端接没有稳态电流的消耗

串行端接方法将消除通过端接电阻的静态功耗。