ZYNQ笔记(5):软中断实现核间通信 - 咸鱼IC - 博客园 (cnblogs.com)

ZYNQ基础----AMP核间软中断_zynq核间中断-CSDN博客

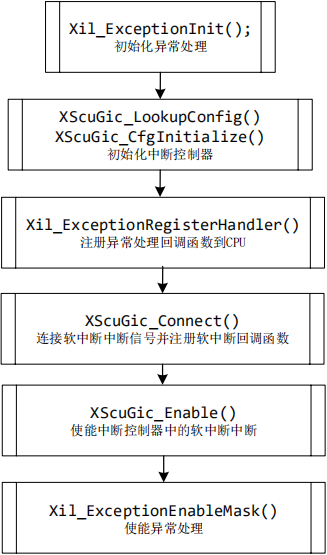

相较于GPIO中断,省去了对中断触发敏感类型的配置(软中断不可配),对中断管脚(Bank)的中断使能,对GPIO回调函数的设置(GPIO中断自己也可以省略这个步骤)。

这是因为GPIO中断实际上是共享同一个中断号的,所以要使能,设置具体的管脚。

具体用什么中断实际上是在第四步连接中断号之后才确定的:

s32 XScuGic_Connect(XScuGic *InstancePtr, u32 Int_Id, Xil_InterruptHandler Handler, void *CallBackRef)

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,

(Xil_ExceptionHandler) XScuGic_InterruptHandler,

&Interrupt_Gpio_instance);

Status = XScuGic_Connect(&Interrupt_Gpio_instance,

Interrupt_ID_Gpio,

(Xil_InterruptHandler )XGpioPs_IntrHandler,

(void *)&GPIO_Decive

); 但是怎么去中断已经在第三步中配置妥善:

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,

(Xil_ExceptionHandler) XScuGic_InterruptHandler,

&Interrupt_Gpio_instance); 触发中断的函数:

指定CPU:Cpu_Identifier上的编号为:Int_Id的中断源触发软中断。

s32 XScuGic_SoftwareIntr(XScuGic *InstancePtr, u32 Int_Id, u32 Cpu_Identifier)

Allows software to simulate an interrupt in the interrupt controller. This function will only be successful when the interrupt controller has been started in simulation mode. A simulated interrupt allows the interrupt controller to be tested without any device to drive an interrupt input signal into it.

参数: InstancePtr – is a pointer to the XScuGic instance. Int_Id – is the software interrupt ID to simulate an interrupt. Cpu_Identifier – is the list of CPUs to send the interrupt.

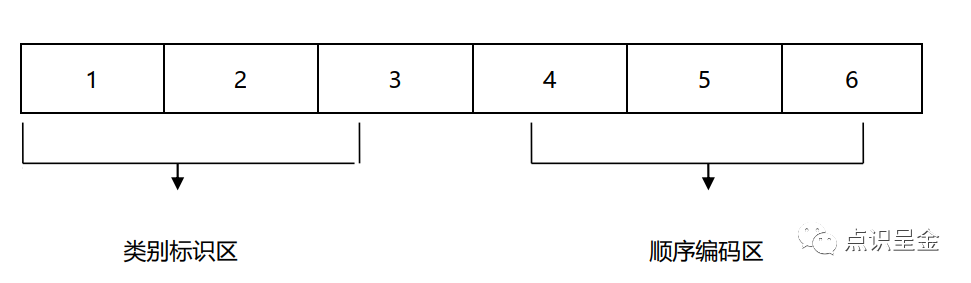

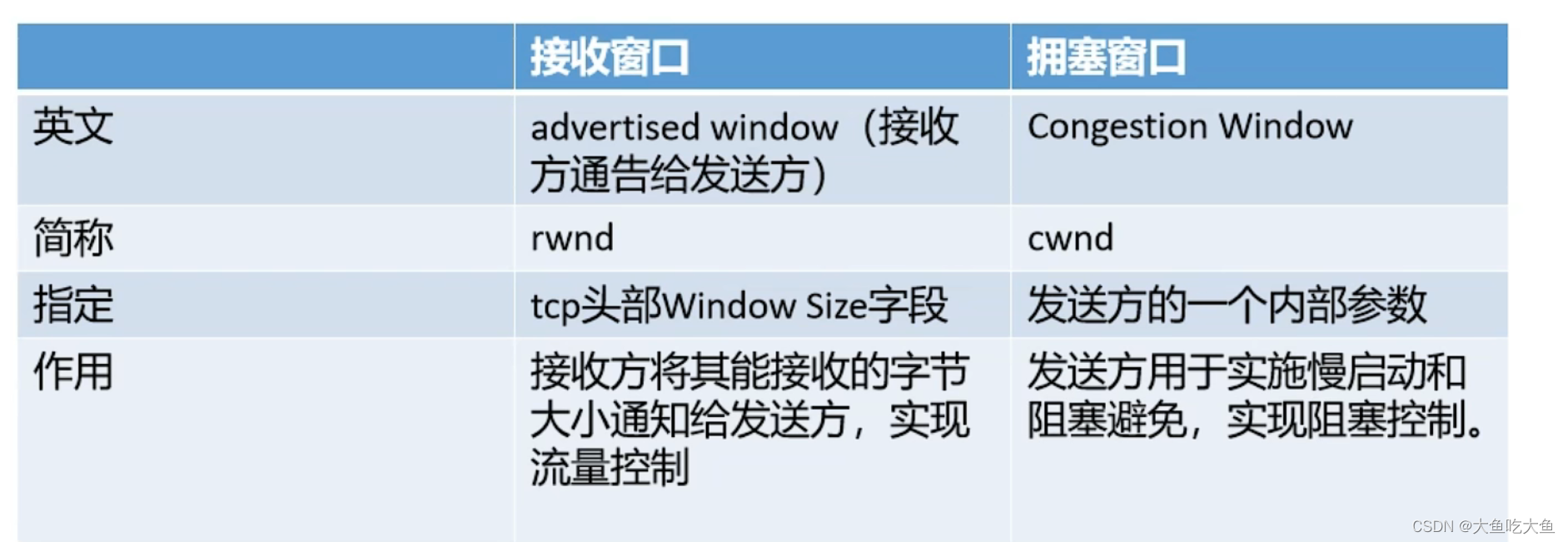

/** @name SPI 目标寄存器 0x800-0x8FB * 每个字节引用一个单独的 SPI 和程序,最多 8 个 CPU * 接口将发送待处理中断。

* 每个 CPU 接口在偏移量 0x800 到 0x81C 处都有寄存器。每个地址最多有 8 个寄存器别名。

* SPI 中断寄存器组可用于所有 CPU 接口。

* 最多有 255 个寄存器从位置 0x820 开始。

* * 该驱动程序不支持多CPU接口。这些包含在 * 中以获取完整的文档。

* @{

*/

#define XSCUGIC_SPI_CPU7_MASK 0x00000080U /**< CPU 7 掩码*/

#define XSCUGIC_SPI_CPU6_MASK 0x00000040U /**< CPU 6 掩码*/

#define XSCUGIC_SPI_CPU5_MASK 0x00000020U /**< CPU 5 掩码*/

#define XSCUGIC_SPI _CPU4_MASK 0x00000010U /**< CPU 4 掩码*/

#define XSCUGIC_SPI_CPU3_MASK 0x00000008U /**< CPU 3 掩码*/

#define XSCUGIC_SPI_CPU2_MASK 0x00000004U /**< CPU 2 掩码*/

#define XSCUGIC_SPI_CPU1_MASK 0x00000002U /**< CPU 1 掩码*/

#define XSCUG IC_SPI_CPU0_MASK 0x00000001U /**< CPU 0 掩码*/