目录

1.算法运行效果图预览

2.算法运行软件版本

3.部分核心程序

4.算法理论概述

5.算法完整程序工程

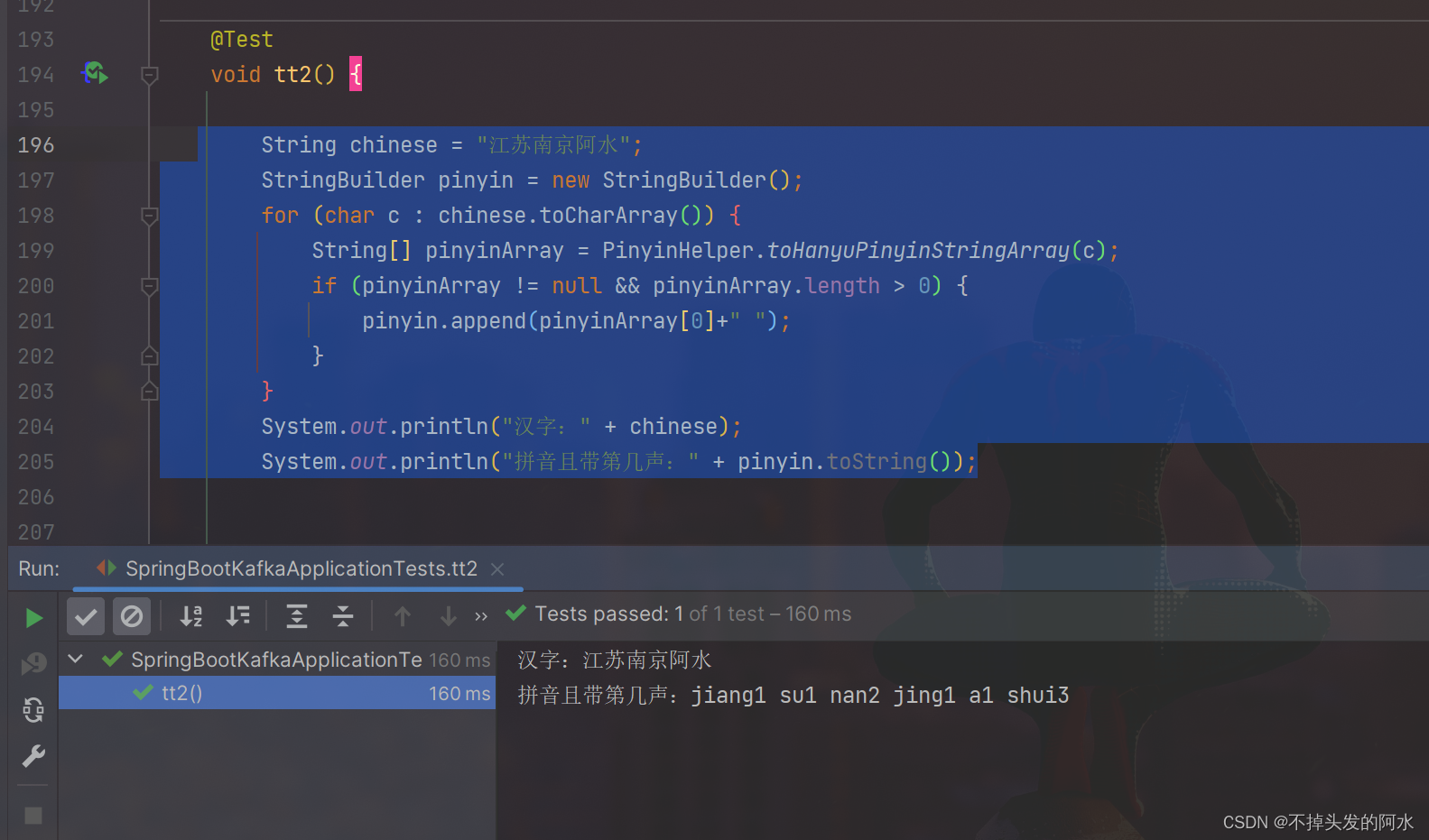

1.算法运行效果图预览

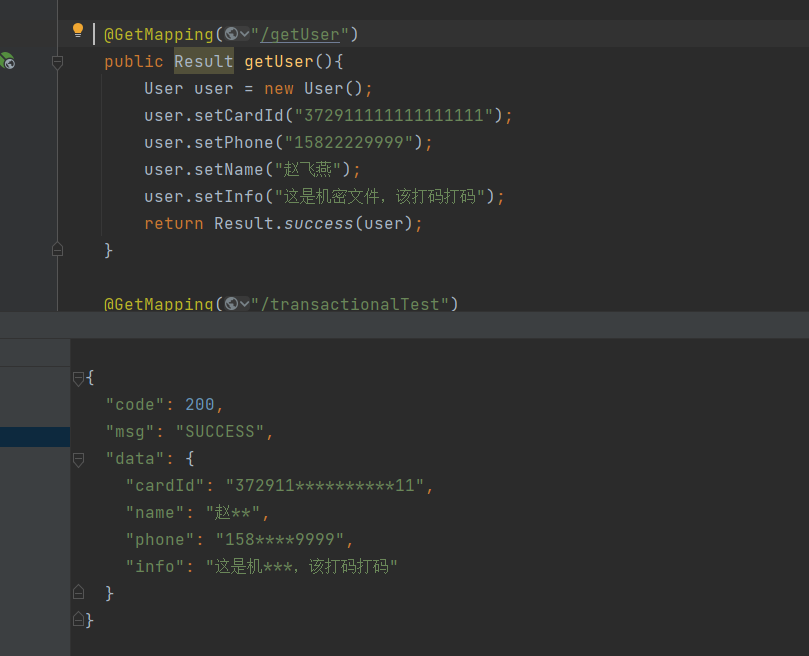

将FPGA的处理结果导出到matlab中显示图像效果:

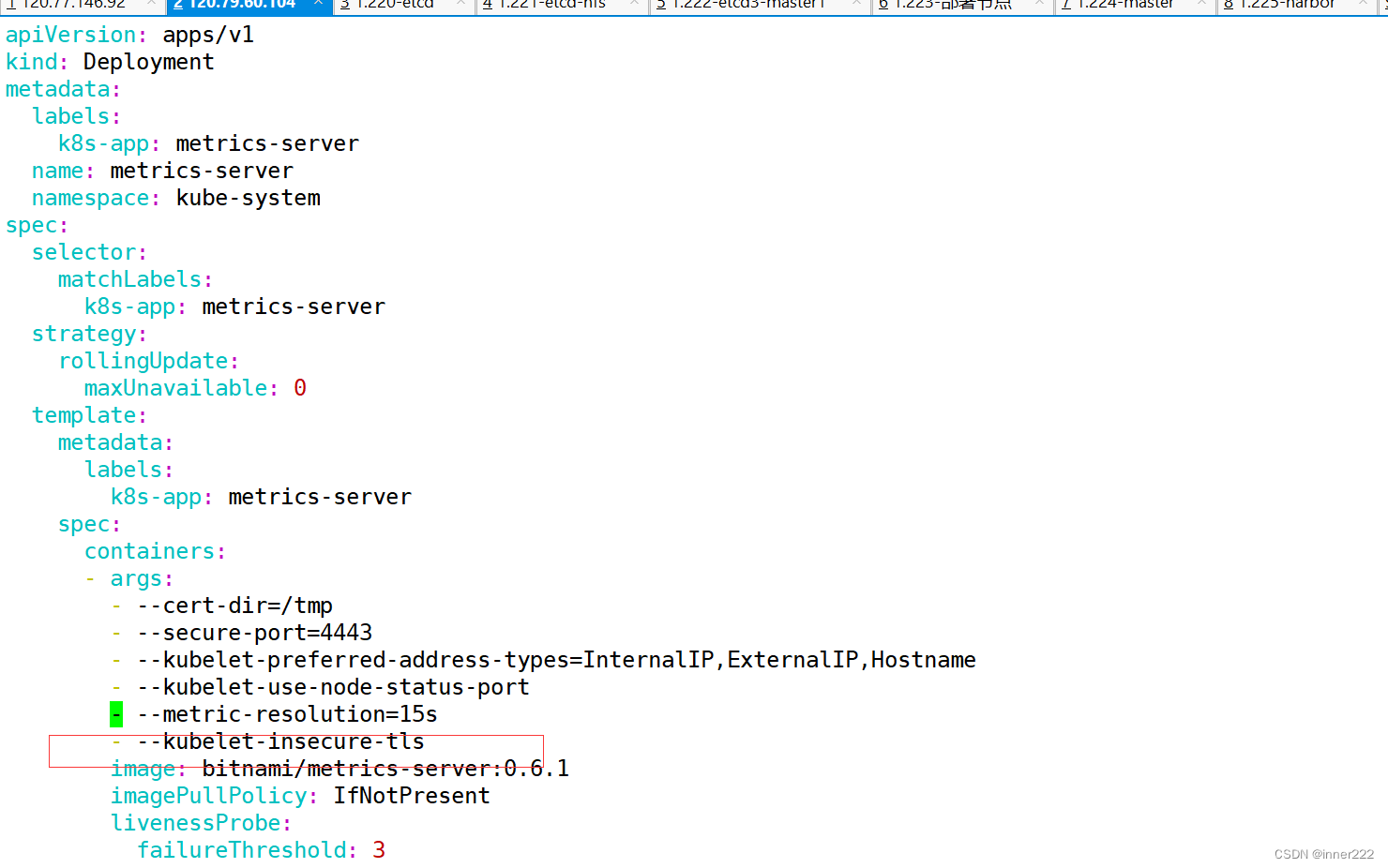

2.算法运行软件版本

vivado2019.2

matlab2022a

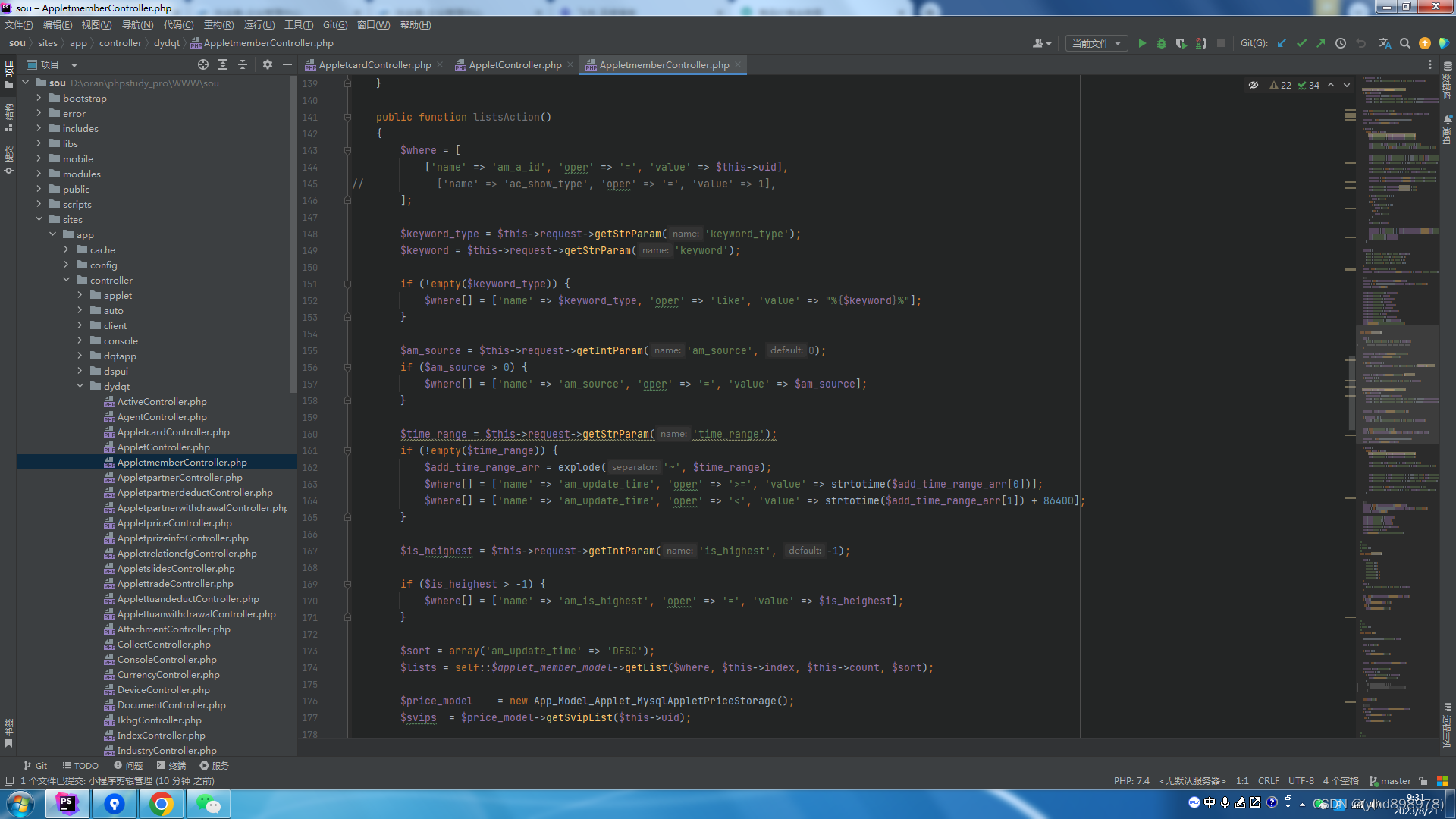

3.部分核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/28 01:51:45

// Design Name:

// Module Name: test_image

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module test_image;

reg i_clk;

reg i_rst;

reg i_en;

reg [7:0] image_buff [0:100000];

reg [7:0] II0;

wire [7:0] o_image;

wire flager;

integer fids,jj=0,dat;

//D:\FPGA_Proj\FPGAtest\codepz

initial

begin

fids = $fopen("D:\\FPGA_Proj\\FPGAtest\\codepz\\data.bmp","rb");

dat = $fread(image_buff,fids);

$fclose(fids);

end

initial

begin

i_clk=1;

i_rst=1;

#2000;

i_rst=0;

end

always #10 i_clk=~i_clk;

always@(posedge i_clk)

begin

if(i_rst)

begin

II0<=0;

jj<=0;

end

else

begin

if(jj<=66614 & jj>=1)

i_en<=1'b1;

else

i_en<=1'b0;

II0<=image_buff[jj];

jj<=jj+1;

end

end

tops tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_en (i_en),

.i_I0 (II0),

.o_image (o_image),

.flager (flager)

);

reg[19:0]cnts;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

cnts<=20'd0;

end

else begin

cnts<=cnts+20'd1;

end

end

integer fout1;

integer fout2;

initial begin

fout1 = $fopen("flager.txt","w");

fout2 = $fopen("expansion.txt","w");

end

always @ (posedge i_clk)

begin

if(cnts <= 66514)

begin

$fwrite(fout1,"%d\n",flager);

$fwrite(fout2,"%d\n",o_image);

end

else

begin

$fwrite(fout1,"%d\n",0);

$fwrite(fout2,"%d\n",0);

end

end

endmodule

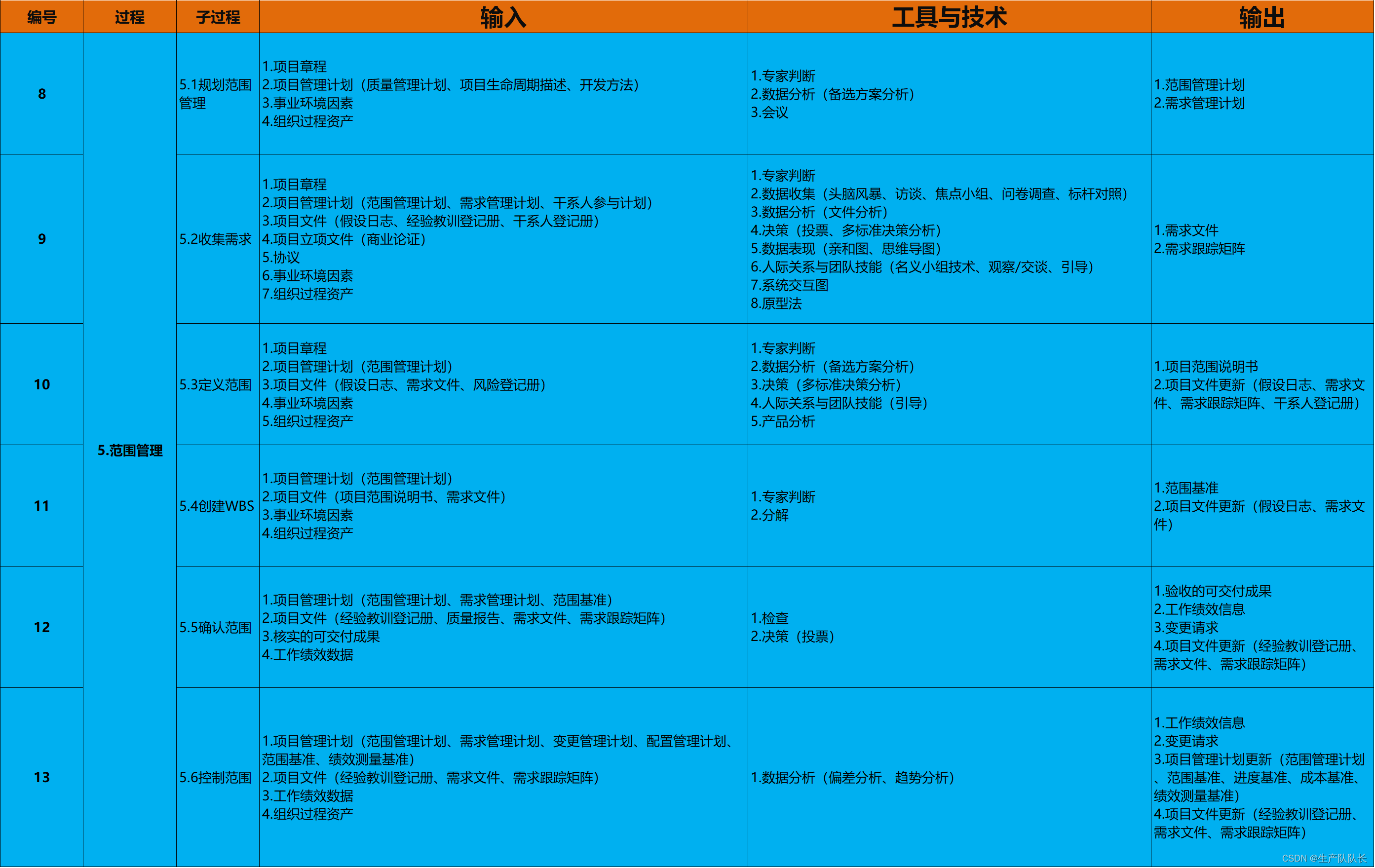

0X_014m4.算法理论概述

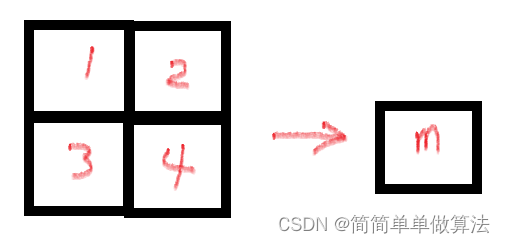

图像放小算法主要通过抽取算法实现,常见的抽取算法最大值抽取,和均值抽取。其示意图如下所示:

以缩小一半为例,如果是最大值抽取,则在一个2*2窗口内,选择最大的像素输出,那么整个图像的维度就变为了原图像的一半。如果是均值抽取,则在一个2*2窗口内,选择四个像素均值输出,那么整个图像的维度就变为了原图像的一半。

在FPGA上实现图像放小算法时,可以采用硬件并行处理的方式,以提高处理速度。具体地,可以通过图像数据缓冲单元模块来实现。

5.算法完整程序工程

OOOOO

OOO

O

![2023年中国在线语言教育行业发展趋势分析:预计2026年在线语言教育市场规模有望实现1182.3亿元[图]](https://img-blog.csdnimg.cn/img_convert/f09632161c47d834838ad25b369795e6.png)