在FPGA的学习中,数字时钟是一个比较基础的实验案例,通过该实验可以更好的锻炼初学者的框架设计能力以及逻辑思维能力,从而打好坚实的基本功,接下来就开始我们的学习吧!

1.数码管介绍

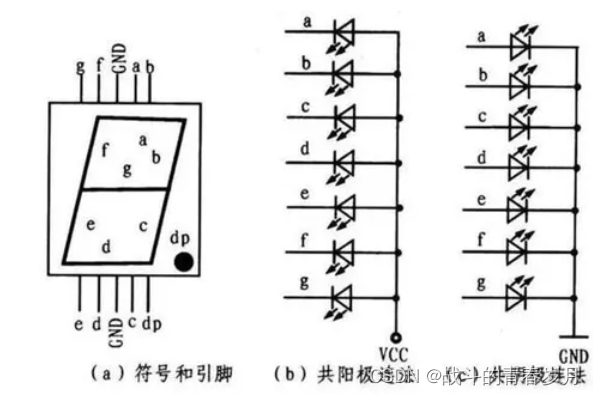

数码管通俗理解就是将8个LED(包含dp部分)灯拼接到一起组成的,分别标号为a~g。前面对LED灯已经讲过,主要是理解对LED的不同硬件接法,对应点亮的输出是不同的。共阳极的接法,0代表亮;共阴极的接法,1代表亮。

数码管可以显示0~9的数字或者一些英文字母,点亮数码管中的部分LED灯,从而组成对应的图形。

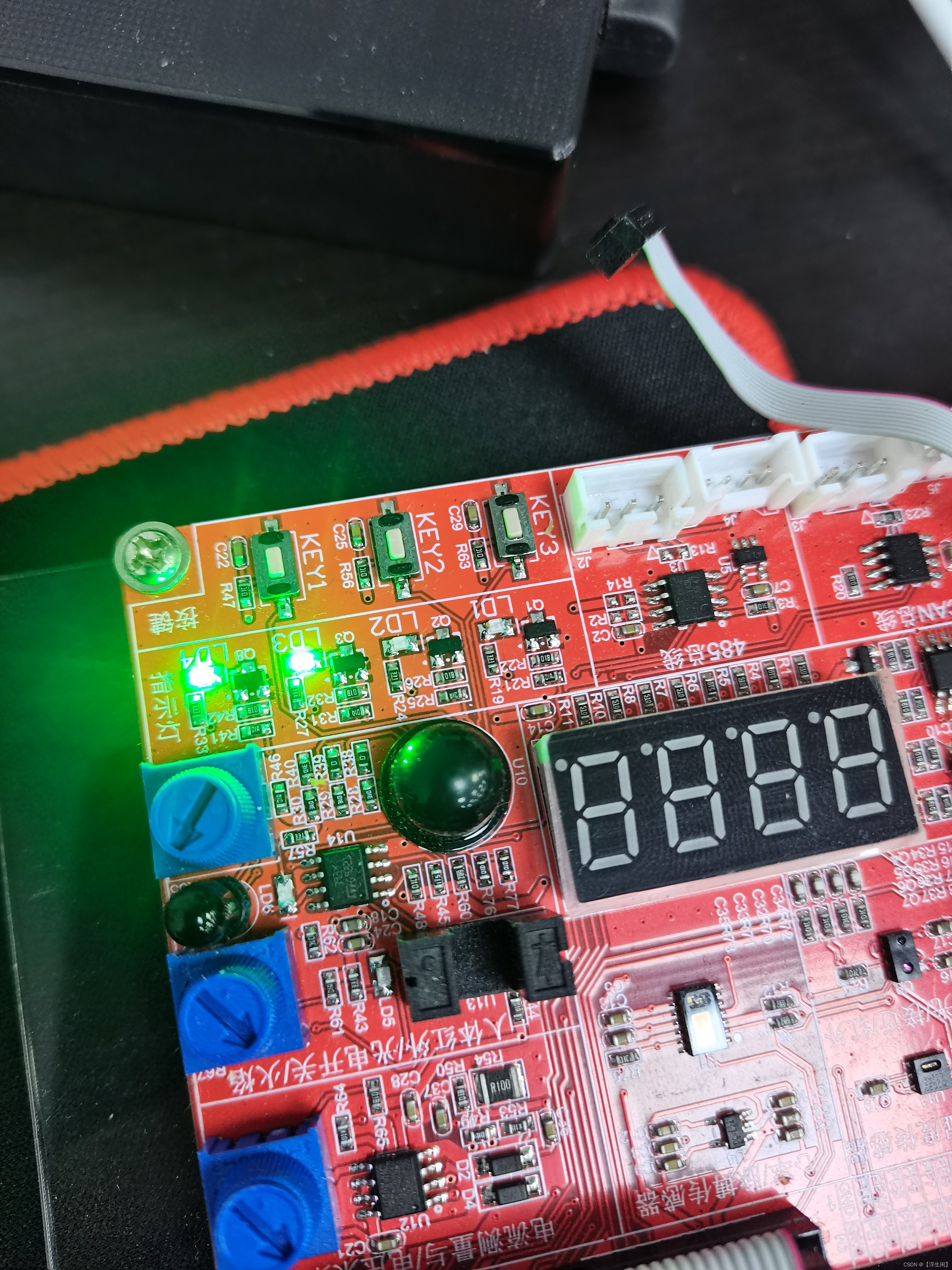

对于多个数码管拼接成一组的操作就是多了一个数码管选通接口,如上图中的K1、K2、K3、K4。如何理解一组数码管的选通接口呢,我们可以把这4个数码管当做家里的4盏灯,K1~K4就是灯的开关,想要哪盏灯亮就打开那个开关,每个数码管在通过8个LED输出想要的图像形就完成了。

在实际操作中,一组数码管每次只能输出一个数码管的显示图形,为了人眼看到4个数码管都能显示图形结果,在选通接口操作时就要加快开关的切换速度,从而让人眼感觉每个数码管都在亮,这个切换频率控制2khz就可以了。

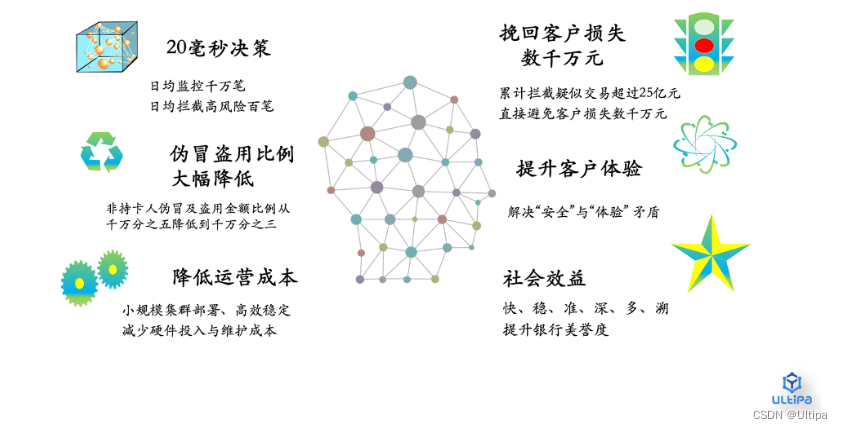

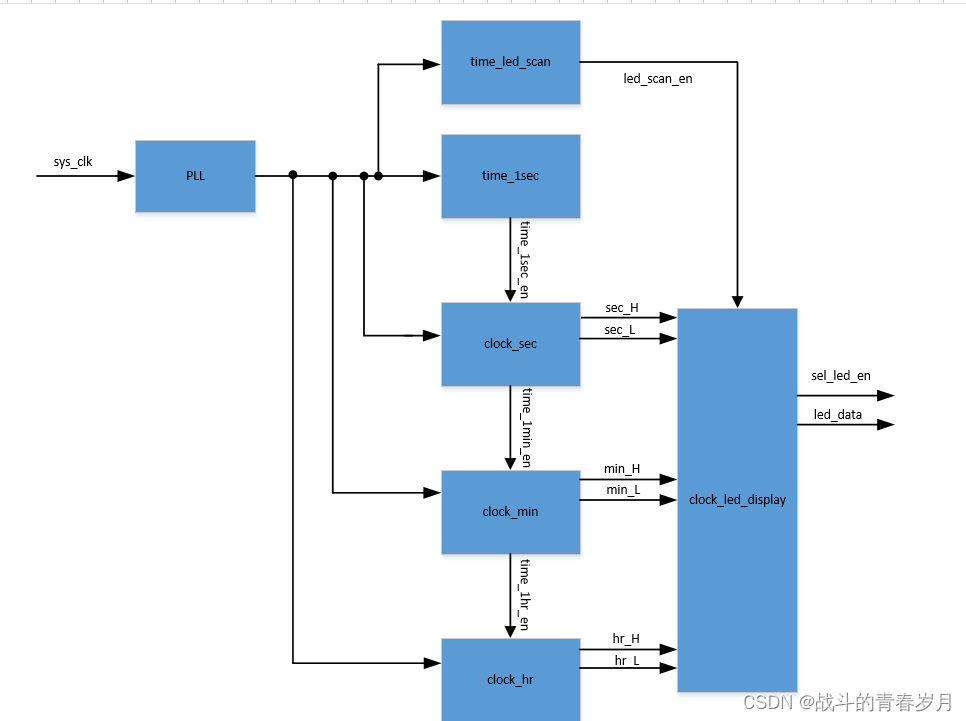

2.系统框架图设计

如上图所示,数字钟系统由7个模块组成,分别是PLL、time_led_scan、time_1sec、clock_sec、clock_min、clock_hr、clock_led_display。

PLL模块:我自己使用的开发板的系统时钟是50Mhz,输出的工作时钟是25Mhz.

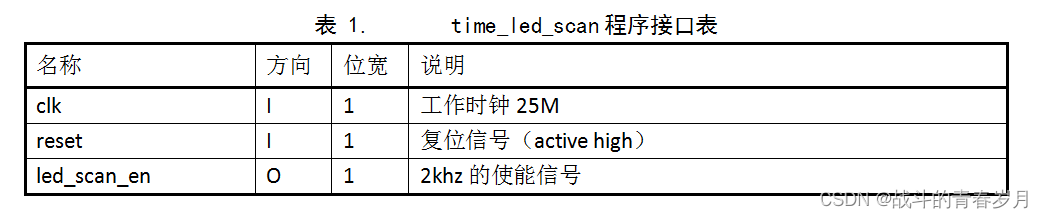

time_led_scan模块

该模块就是产生数码管段选的2khz频率信号。

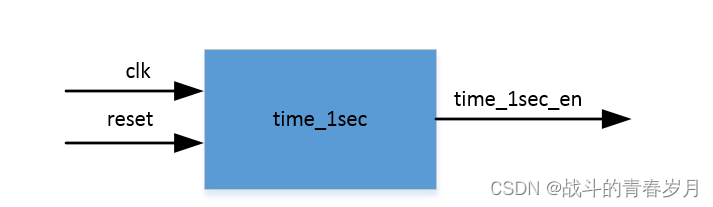

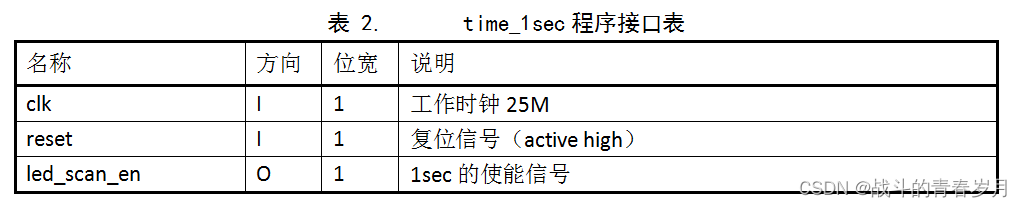

time_1sec模块:输出1秒钟的使能信号

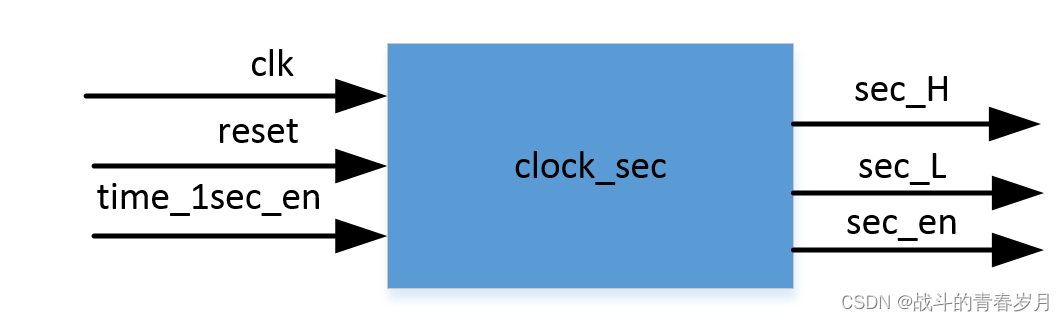

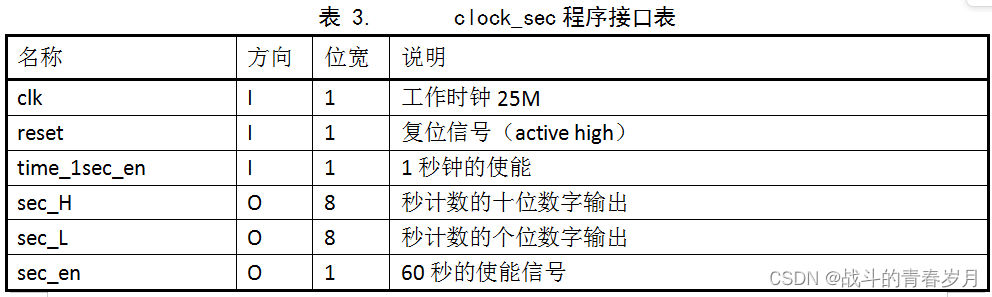

clock_sec模块:输出0~59秒钟的计时功能;

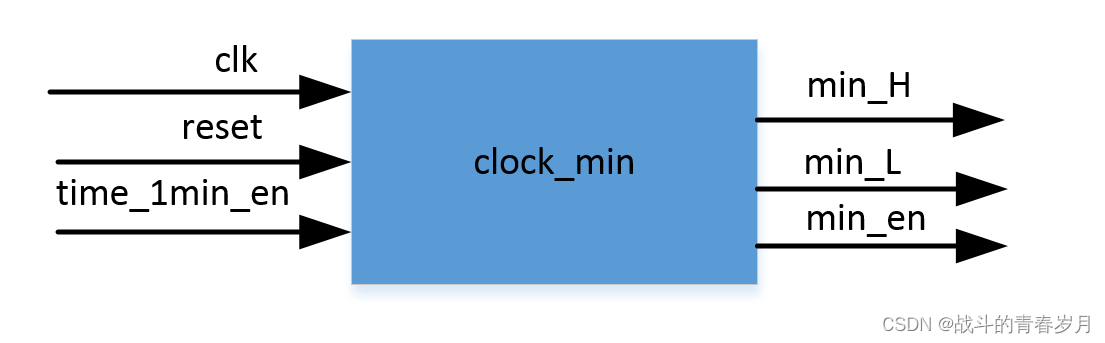

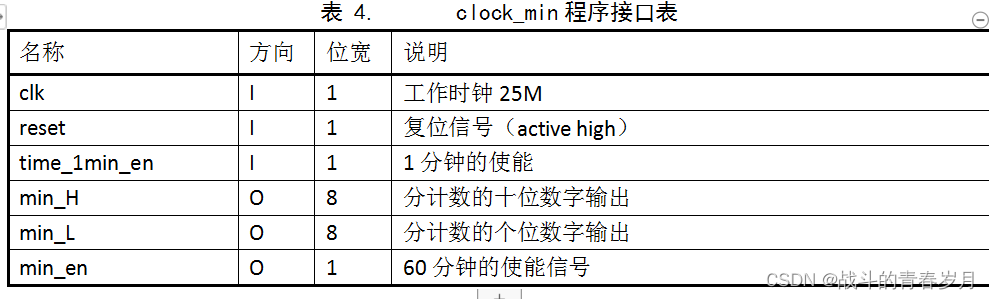

clock_min模块:输出0~59分钟的计时功能;

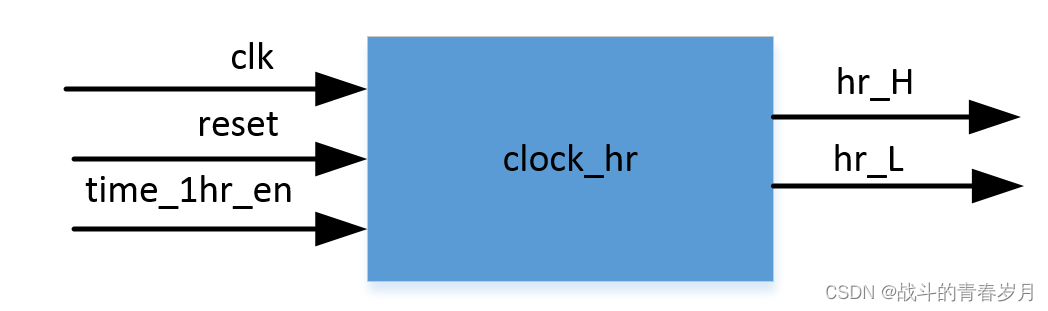

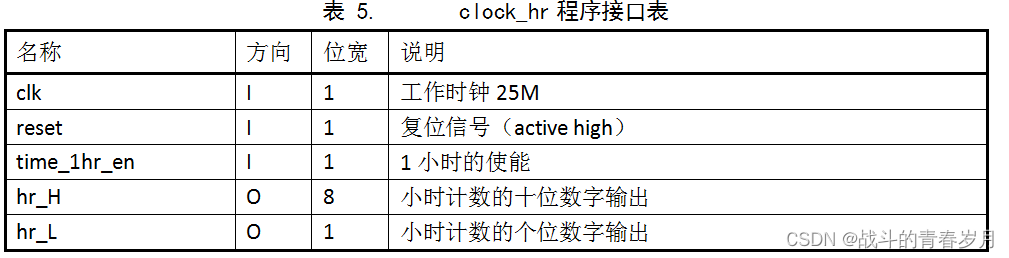

clock_hr模块:输出0~23小时的计时功能

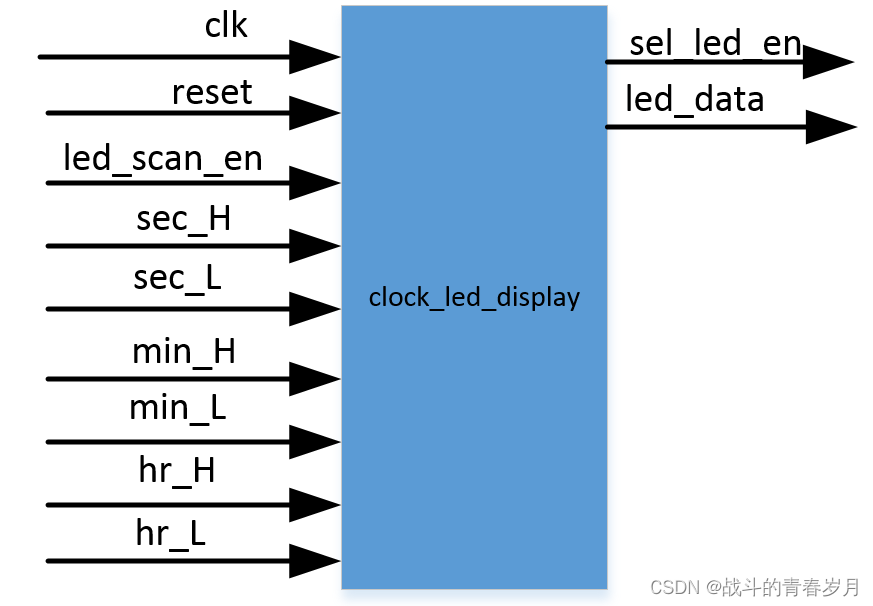

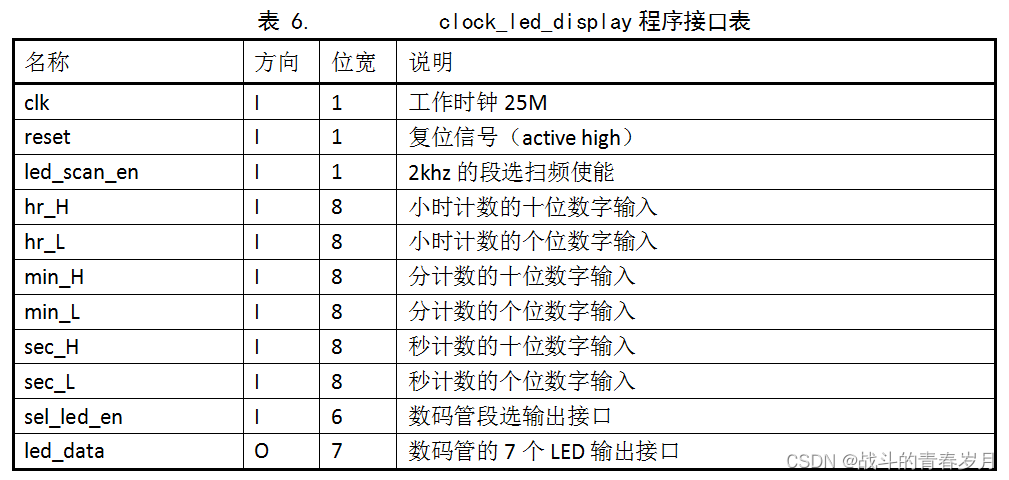

clock_led_dispaly模块:输出对应的时间数字图形。

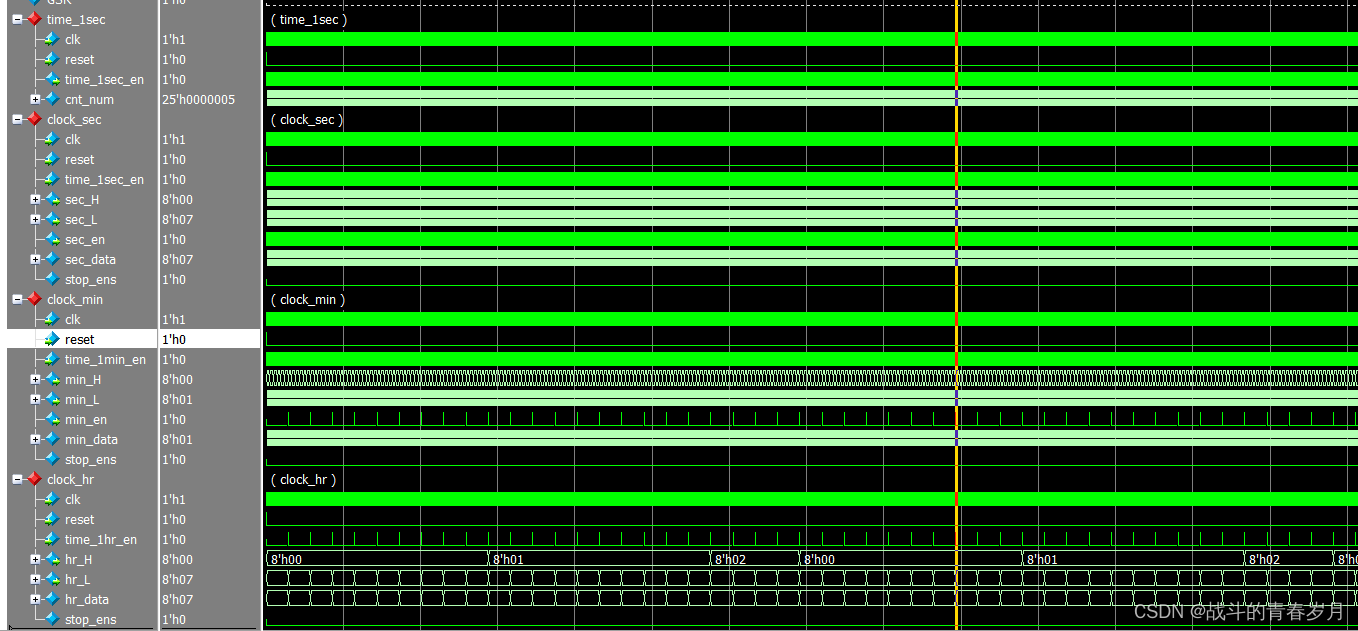

程序仿真结果

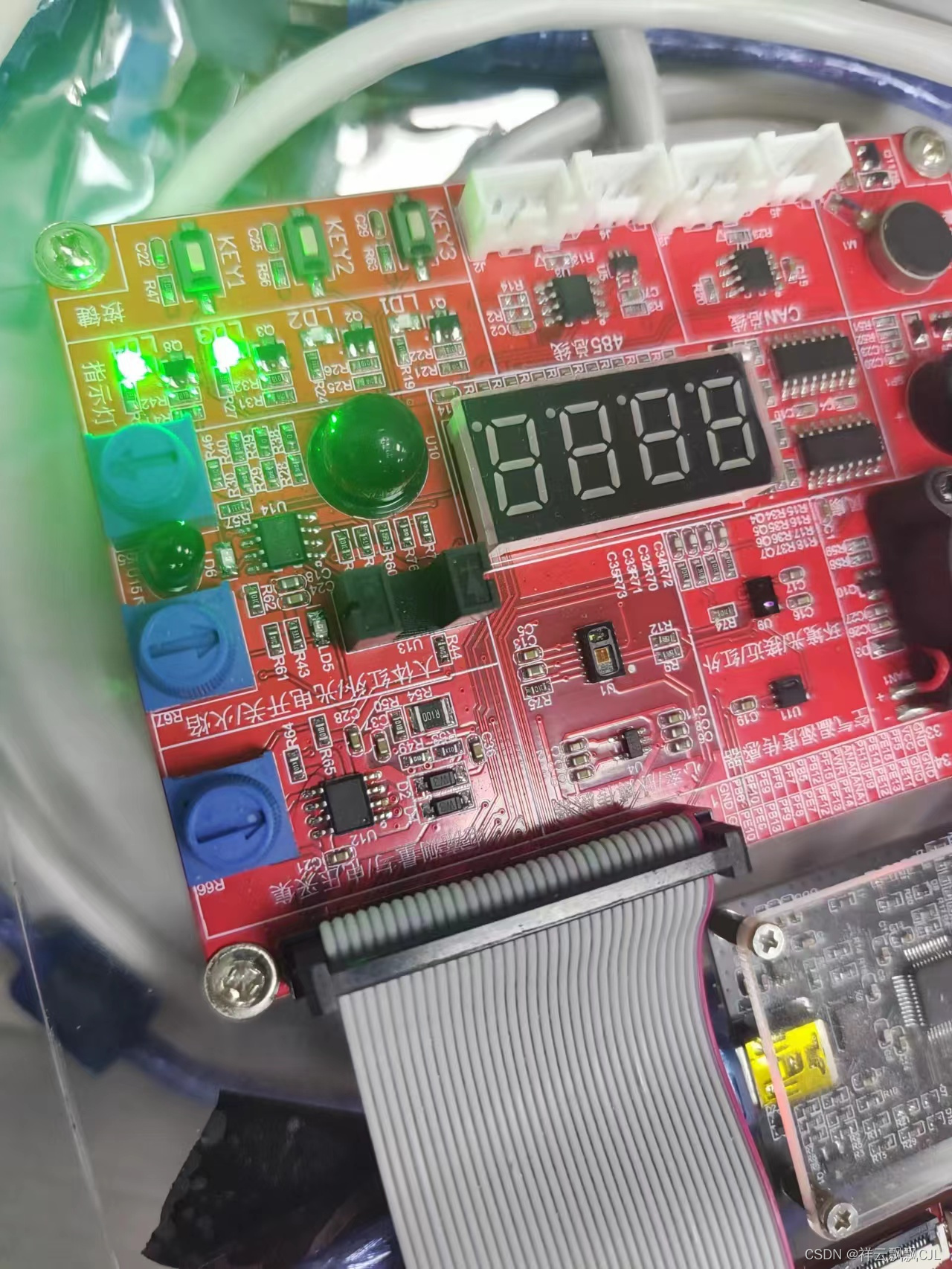

上板运行结果:输出的是0时0分25秒,程序上电初始化的时间是0时0分0秒。