名称:多功能频率计周期、脉宽、占空比、频率测量verilog

软件:Quartus

语言:Verilog

代码功能:

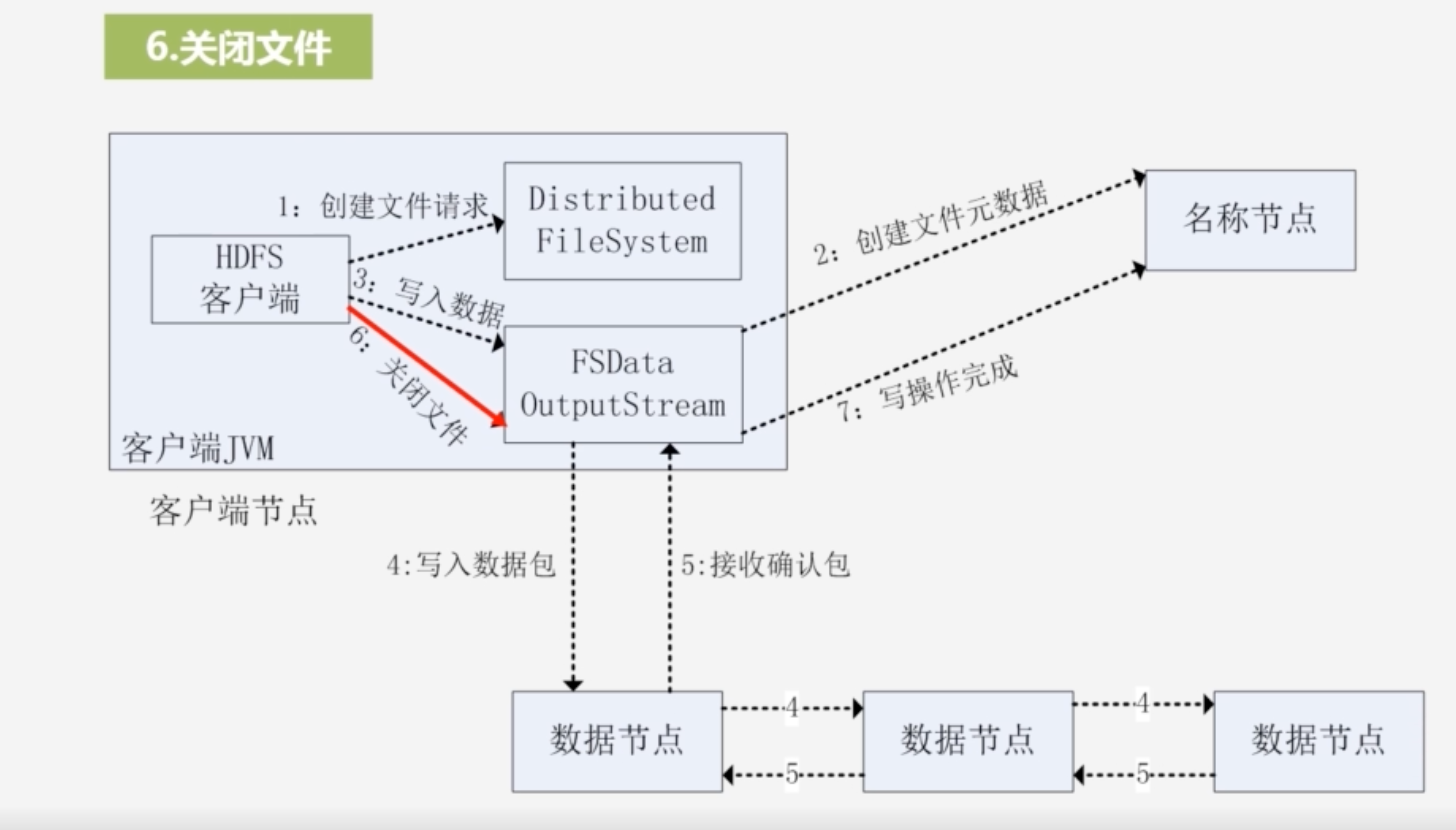

多功能频率计,可测量信号的周期、脉冲宽度、占空比、频率,语言为verilog,quartus软件设计仿真

代码下载:多功能频率计周期、脉宽、占空比、频率测量verilog_Verilog/VHDL资源下载名称:多功能频率计周期、脉宽、占空比、频率测量verilog(代码在文末付费下载)软件:Quartus语言:Verilog代码功能: 多功能频率计,可测量信号的周期、脉冲宽度、占空比、频率,语言为verilog,quartus软件设计仿真演示视频:部分代码展示module signal_detect(input clk_in,//输入100M基准时钟input reset_p,//复位信号in![]() http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=187

http://www.hdlcode.com/index.php?m=home&c=View&a=index&aid=187

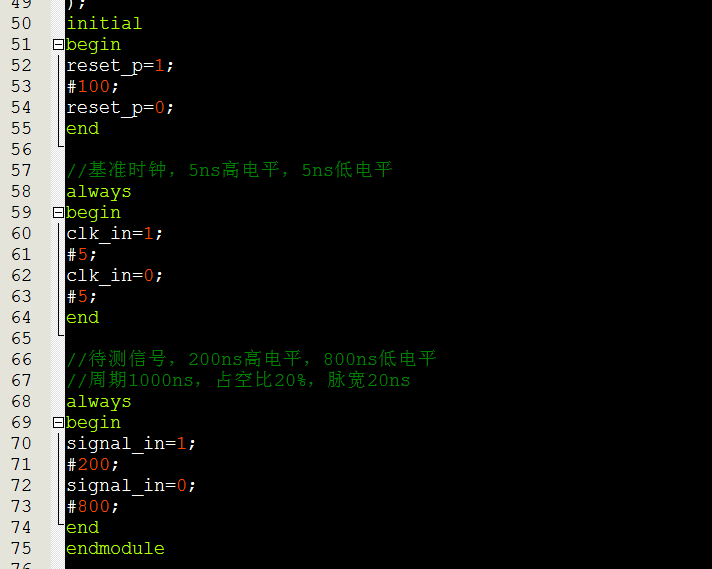

部分代码展示

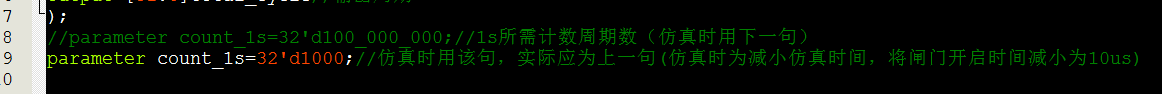

module signal_detect( input clk_in,//输入100M基准时钟 input reset_p,//复位信号 input signal_in,//待测频率输入 output [31:0]total_frequency,//输出频率 output [31:0]total_cycle,//输出周期 output [31:0]pulse_width,//输出脉宽 output [31:0]duty_cycle//输出占空比 ); frequency_detect i_frequency_detect( . clk_in(clk_in),//输入100M基准时钟 . reset_p(reset_p),//复位信号 . signal_in(signal_in),//待测频率输入 . total_frequency(total_frequency),//输出频率 . total_cycle(total_cycle)//输出周期 ); pulse_detect i_pulse_detect( . clk_in(clk_in),//输入100M基准时钟 . reset_p(reset_p),//复位信号 . signal_in(signal_in),//待测频率输入 . pulse_width(pulse_width),//输出脉宽 . duty_cycle(duty_cycle)//输出占空比 ); endmodule module frequency_detect( input clk_in,//输入100M基准时钟 input reset_p,//复位信号 input signal_in,//待测频率输入 output [31:0]total_frequency,//输出频率 output [31:0]total_cycle//输出周期 ); //parameter count_1s=32'd100_000_000;//1s所需计数周期数(仿真时用下一句) parameter count_1s=32'd1000;//仿真时用该句,实际应为上一句(仿真时为减小仿真时间,将闸门开启时间减小为10us) reg [31:0] door_1s_cnt=32'd0;//闸门信号1s开启一次 always@(posedge clk_in) if(reset_p==1) door_1s_cnt<=32'd0; else if(door_1s_cnt==count_1s) door_1s_cnt<=32'd0; else door_1s_cnt<=door_1s_cnt+32'd1; reg door_1s=0; always@(posedge clk_in) if(door_1s_cnt==count_1s) door_1s<=~door_1s;//闸门信号1s开启一次 reg [31:0] CNT1=32'd0;//基准时钟计数器 reg [31:0] CNT2=32'd0;//待测频率计数器 reg [31:0] CNT1_buf=32'd0;//基准时钟计数器寄存器 reg [31:0] CNT2_buf=32'd0;//待测频率计数器寄存器

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

3. 原理图文件

4. 程序编译

5. Testbench

6. 仿真图

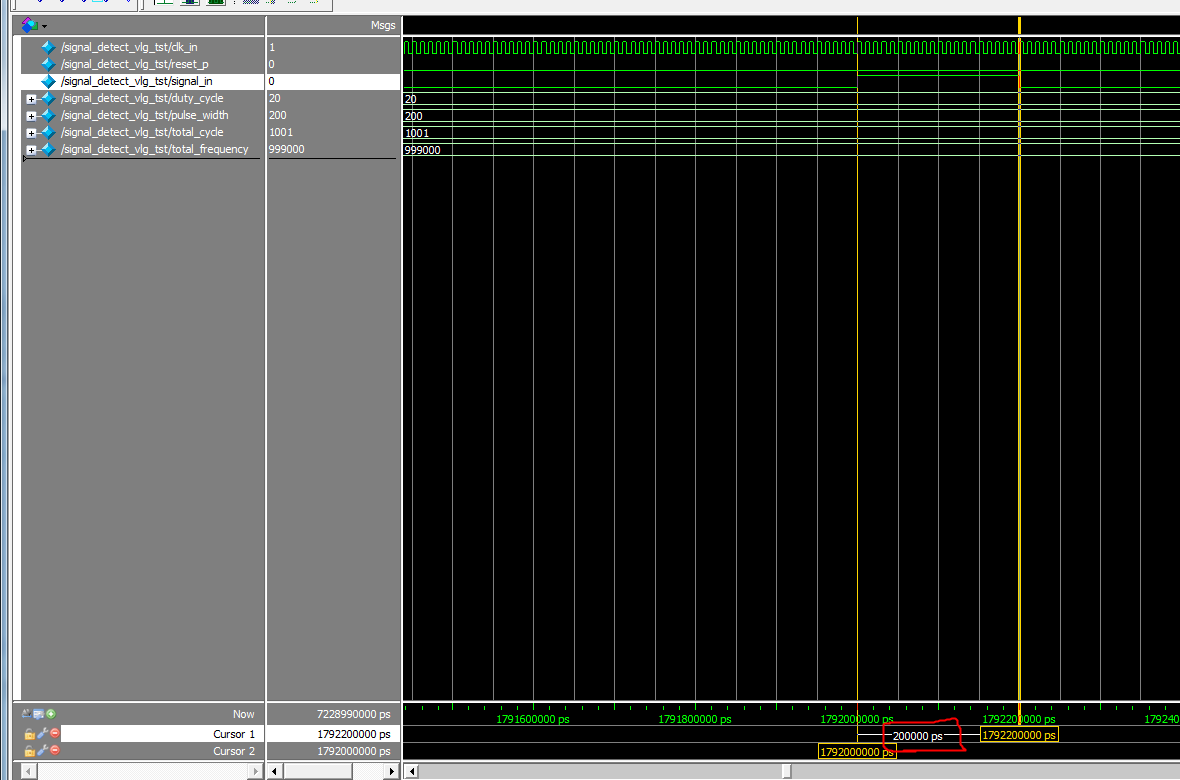

6.1整体仿真图

仿真图可看出测得占空比duty_cycle=20%;脉宽pulse_width=200ns,周期total_cycle=1001ns,频率total_frequency=999000Hz,其中频率误差较大(实际应为1000000Hz,误差999Hz)这是因为仿真时为减小仿真时间,使用的闸门信号为10us,闸门实际应为1s,减小了100000倍。

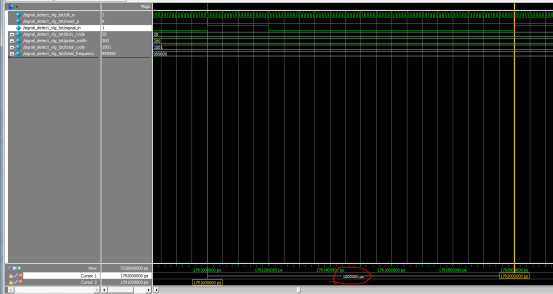

6.2局部细节,被测信号脉宽200ns,测试结果为200,正确

6.3局部细节,被测信号周期1000ns,测试结果为1001ns,误差1ns。(误差与频率一样,可以通过增大闸门减小误差)

设计文档.doc

演示视频:多功能频率计周期、脉宽、占空比、频率测量verilog_Verilog/VHDL资源下载