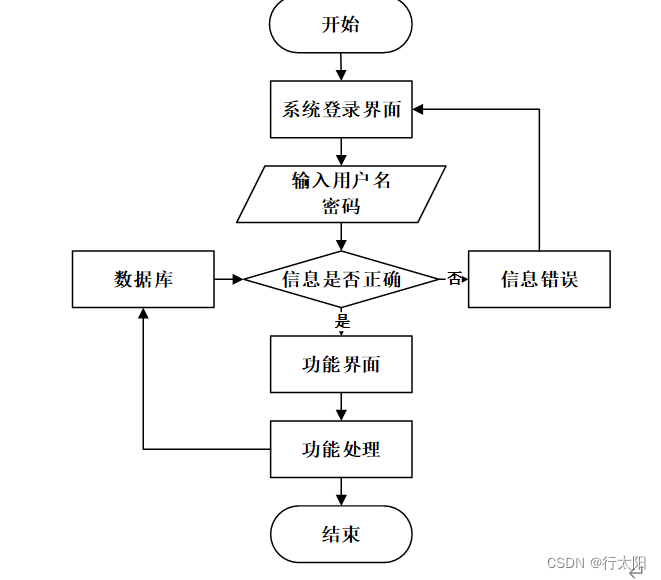

IIC: inter-integrated circuit bus ,即 集成电路总线,串行通信,多主从架构,半双工(对讲机),小数据量场合,短距离传输。

速率:100kb/s 、 400kb/s 、 3.4Mkb/s

传输单位:8位(一个字节)(双向)

架构:每个IIC器件都可作为主/从器件,一个时间只有一个主设备

两条总线线路:SCL(串行时钟线)、 SDA(串行数据线)总线拓扑结构如图

图中,每个IIC器件拥有唯一地址(识别码)。

主机往总线上发送地址,所有的从机都能接收到主机发出的地址,然后每个从机都将主机发出的地址与自己的地址比较,如果匹配上了,这个从机就会向总线发出一个响应信号。主机收到响应信号后,开始向总线上发送数据,与这个从机的通讯就建立起来了。如果主机没有收到响应信号,则表示寻址失败。

IIC帧格式

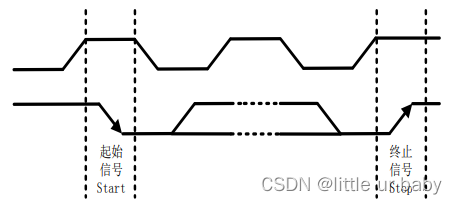

默认规定:SCL高电平时,SDA稳定;SCL低电平时,SDA变化。(依此设定SDA的数据变化时刻,在SCL的低电平中点变化较为靠谱)

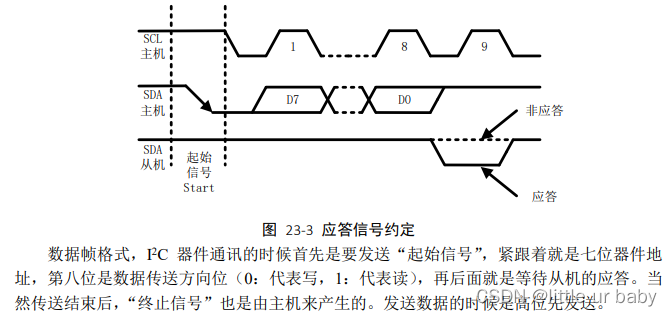

响应位:当 IIC 主机(不一定是发送端还是接受端)将8位数据或命令传出后, SDA释放,即设置为输入,然后等待从机应答(低电平 0 表示应答,1 表示非 应答),此时的时钟仍然是主机提供的。

起始信号:SCL高且SDA出现下降沿。

停止信号:SCL高且SDA出现上升沿。

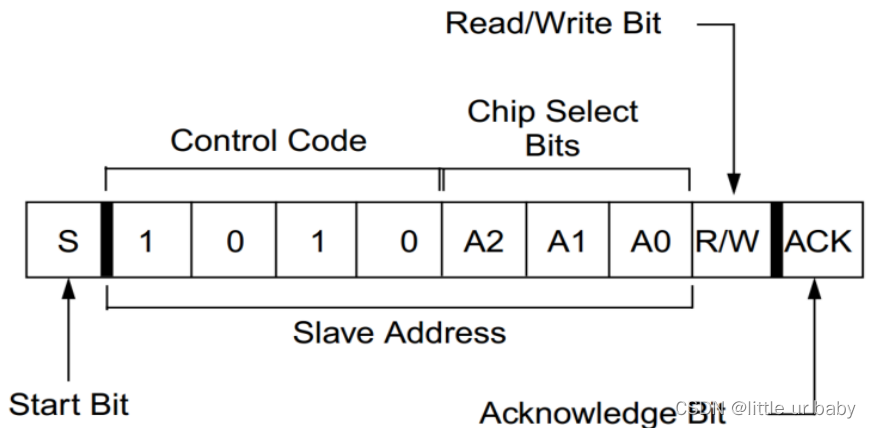

器件地址

每个I2C器件都有一个器件地址,有的器件地址在出厂时地址就设置好了,用户不可以 更改(例如 OV7670 器件地址为固定的 0x42),有的确定了几位,剩下几位由硬件确定(比 如常见的I2C接口的EEPROM存储器,留有3个控地址的引脚,由用户自己在硬件设计时确定)。

对于AT24C64这样一颗EEPROM器件,其器件地址为1010加3位的片选信号。3位片选信号由硬件连接设定。当硬件电路上分别将这三个引脚连接到 GND 或 VCC 时,就可以设置不同的片选地址。

I2C传输时,按照从高到低的位序进行传输。控制字节的最低位为读写控制位,当该位 为0时表示主机对从机进行写操作,当该位为1时表示主机对从机进行读操作。

在某些IIC器件中,A2 A1 A0可以当作存储单元地址来用。存储器地址一般为1或2字节。取决于IIC器件容量。

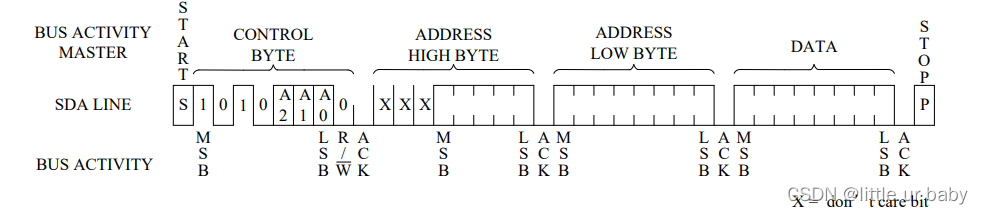

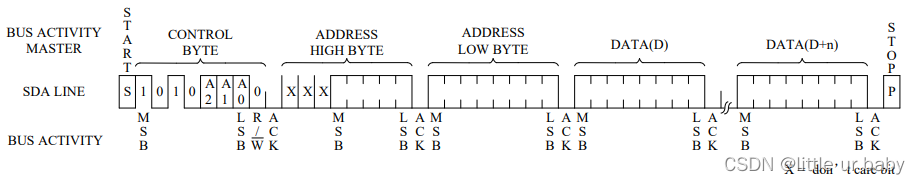

IIC写时序

时序:

1、主机设置 SDA 为输出;发送起始信号;

3、主机传输器件地址字节,其中最低位为 0,表明为写操作;

4、主机设置 SDA 为三态门输入,读取从机应答信号;

5、读取应答信号成功,主机设置 SDA 为输出,传输地址数据高字节;

6、主机设置 SDA 为三态门输入,读取从机应答信号;

7、读取应答信号成功,主机设置 SDA 为输出,传输地址数据低字节;

8、设置 SDA 为三态门输入,读取从机应答信号;

9、读取应答信号成功,主机设置 SDA 为输出,传输待写入的数据;

10、设置 SDA 为三态门输入,读取从机应答信号;

11、读取应答信号成功,主机产生 STOP 位,终止传输。

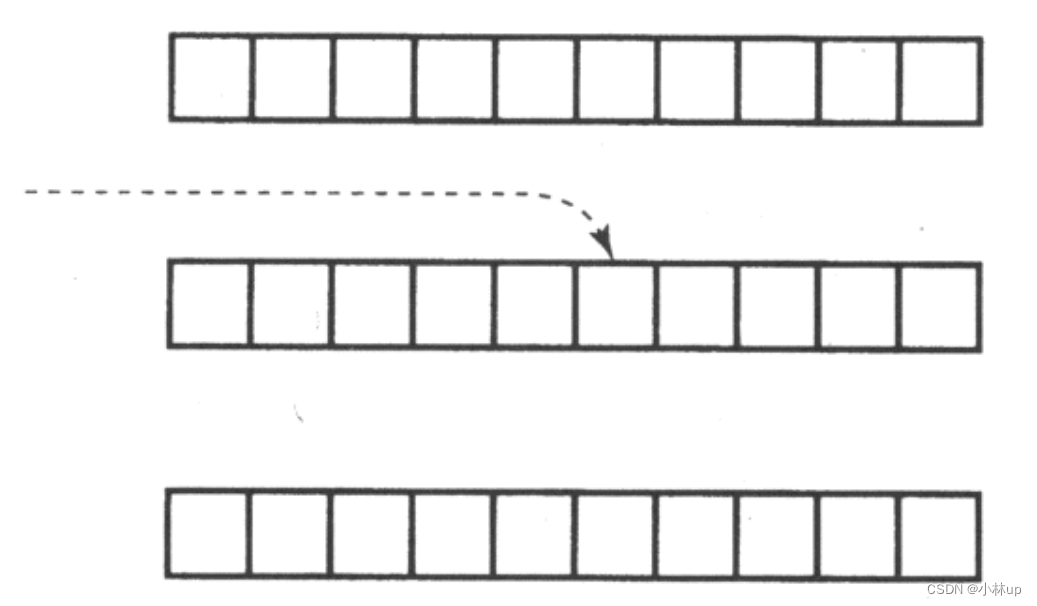

IIC页写时序(连续写)

主机连续写多个字节数据到从机,I2C连续写时序仅部分器件支持。

时序类似上面,只是变成了连续写n个数据。

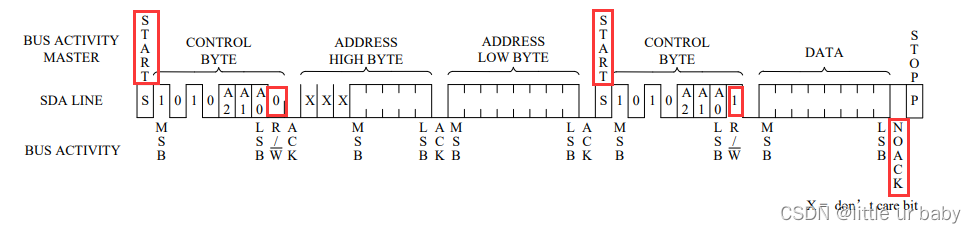

IIC读时序

注意:虽然是读时序,但是这里先用了写信号告诉从机要读的存储器地址,然后再换成读信号把该地址的数据读到主机。

1、主机设置 SDA 为输出;发送起始信号;

3、主机传输器件地址字节,其中最低位为 0,表明为写操作;

4、主机设置 SDA 为三态门输入,读取从机应答信号;

5、读取应答信号成功,主机设置 SDA 为输出,传输地址数据高字节;

6、主机设置 SDA 为三态门输入,读取从机应答信号;

7、读取应答信号成功,主机设置 SDA 为输出,传输地址数据低字节;

8、设置 SDA 为三态门输入,读取从机应答信号;

9、读取应答信号成功,主机发起起始信号;

10、主机传输器件地址字节,其中最低位为 1,表明为读操作;

11、设置 SDA 为三态门输入,读取从机应答信号;

12、读取应答信号成功,主机设置 SDA 为三态门输入,读取 SDA 总线上的一个字节的 数据;

13、主机设置 SDA 输出,产生无应答信号(高电平)(不想继续读数据了)(无需设置为输出高电平,因为总线会被自动拉高);

14、主机产生 STOP 位,终止传输。

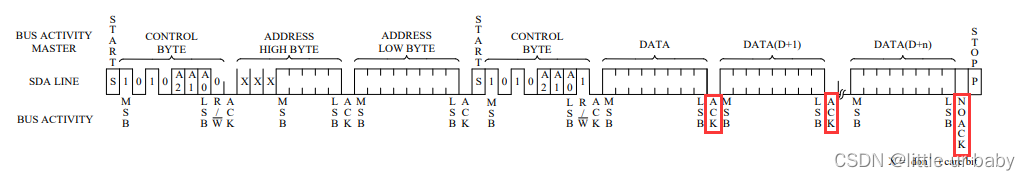

IIC页读时序

读数据时用ACK应答,不想继续读时用NOACK应答即可。

IIC控制器设计

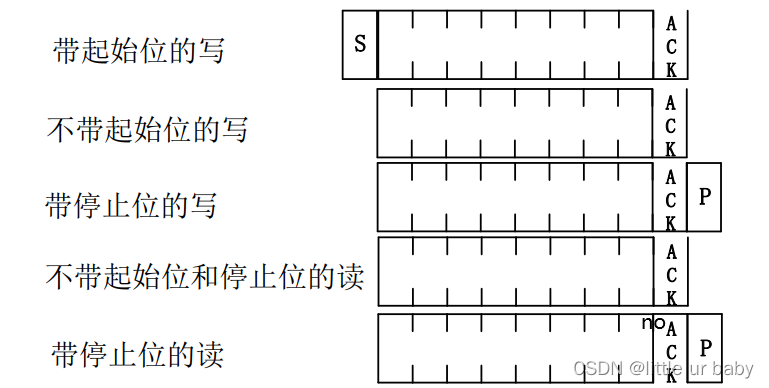

对完整的读和写时序进行分析,可以总结为五种情况:

每段在传输的时候,只需要确定当前这个字节的传输 之前是否需要加入起始位,以及当前这个字节的传输结束后是否需要加入停止位就结束了。

![[JAVAee]SpringBoot-AOP](https://img-blog.csdnimg.cn/90425924543a410786d19347fcb5ae6c.png)