一、计算机组成原理

1.数据的表示

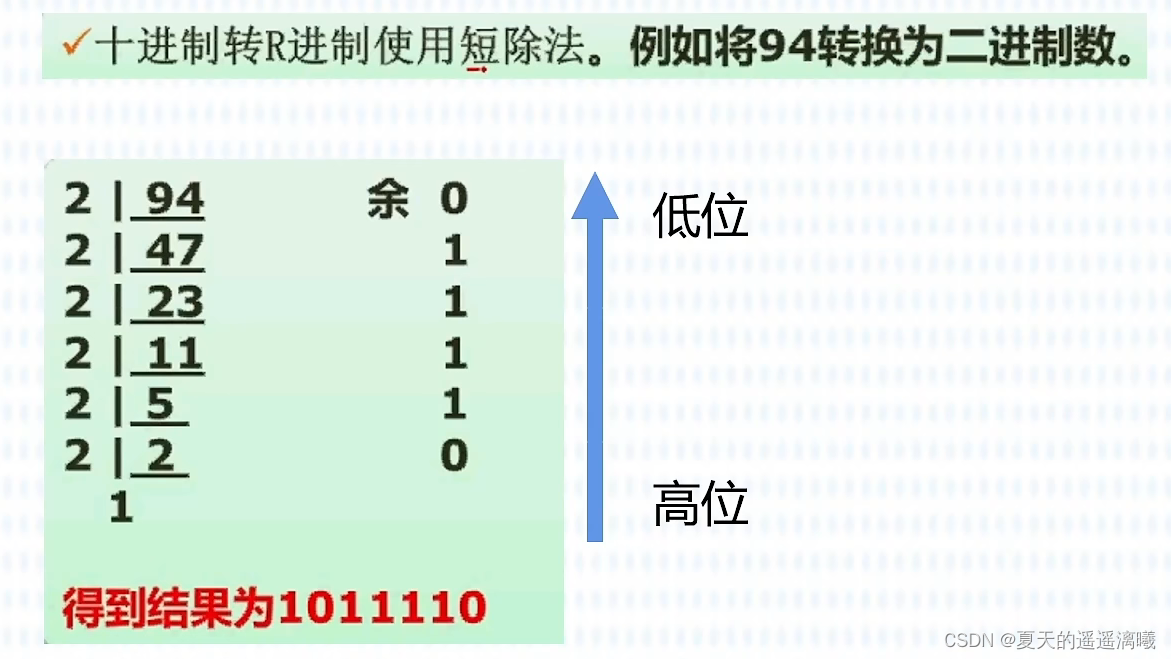

1.1 十进制转R进制

方法:对十进制数除R取余,最后对余数取倒序

如:

1.2 原码反码补码

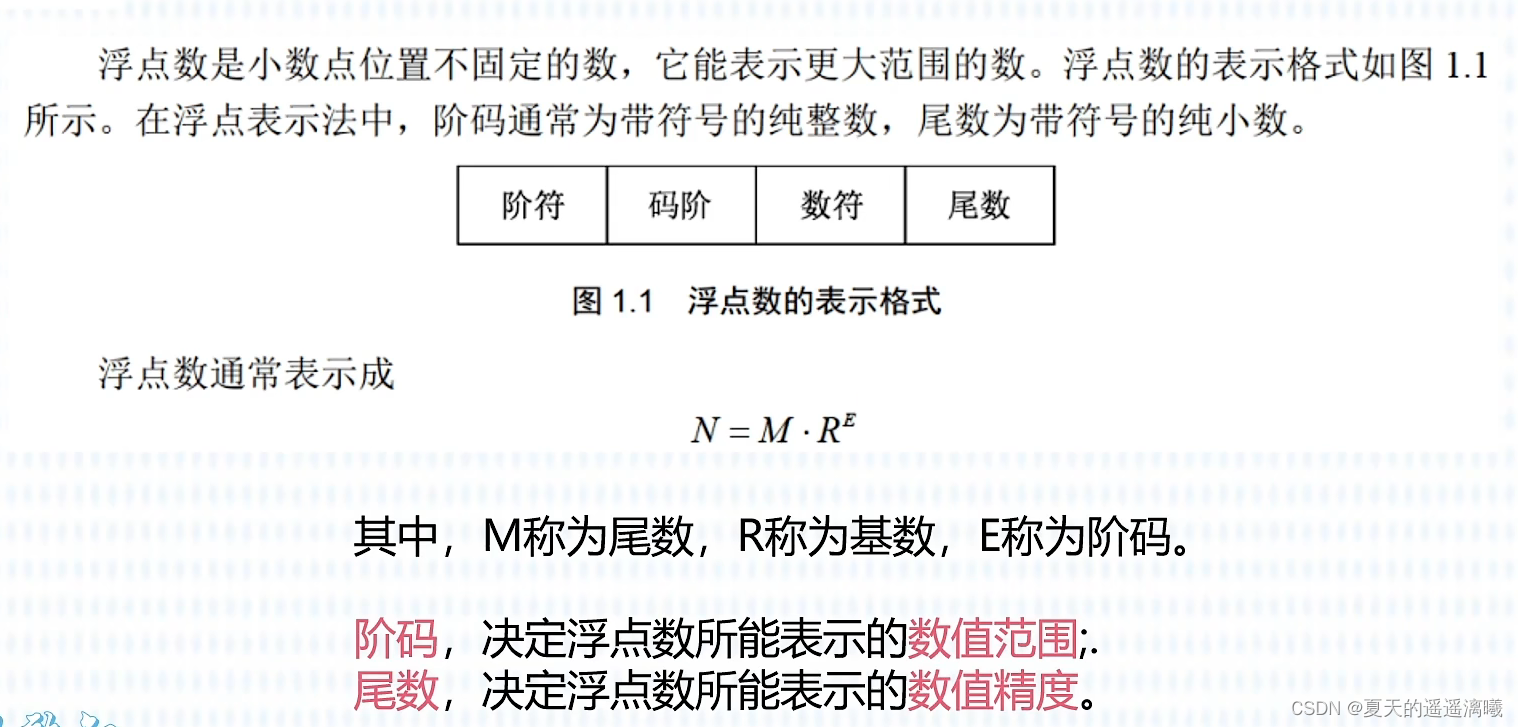

1.3 浮点数

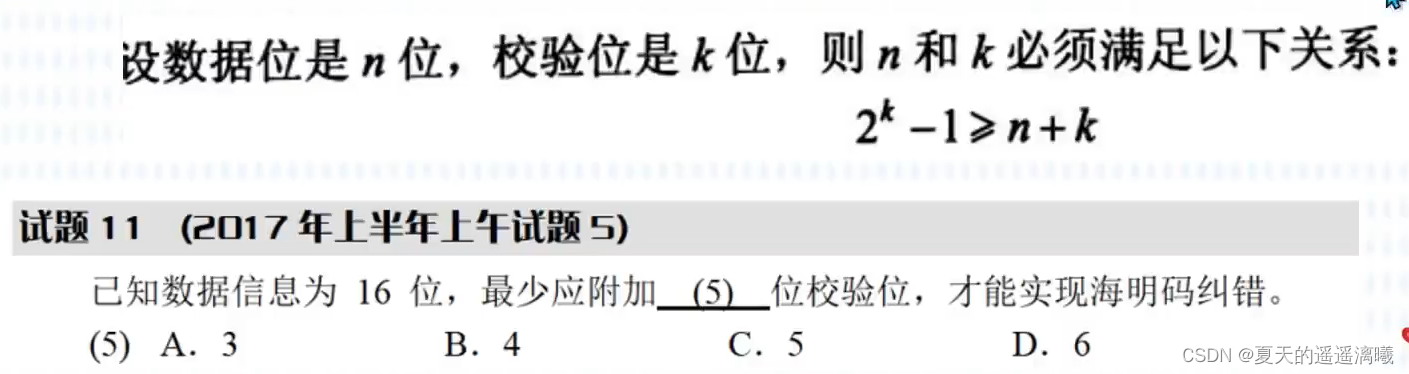

1.4 校验码 —— 海明码 (非重点,了解即可)

海明码的构成方法: 在数据位之间插入k个校验码,通过扩大码距来实现检错和纠错。

n = 16 , 根据关系式依次带入校验位k:

当K=4时,

- 1

16 + 4 X

当k= 5 时,

√

最终选C

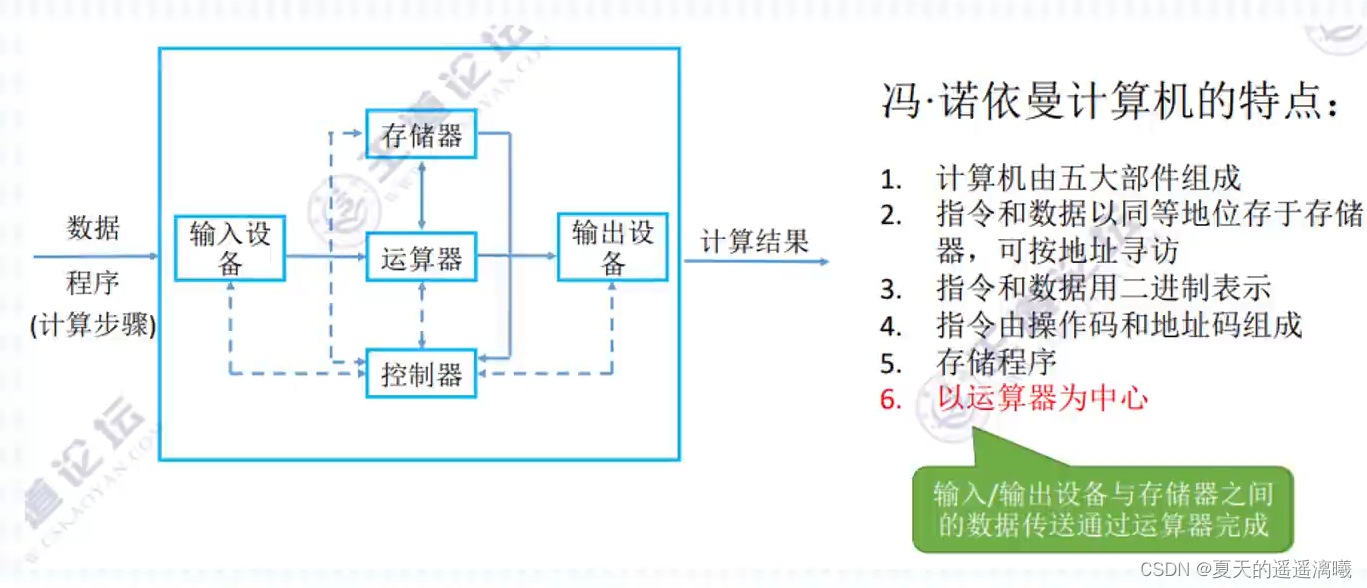

2. CPU

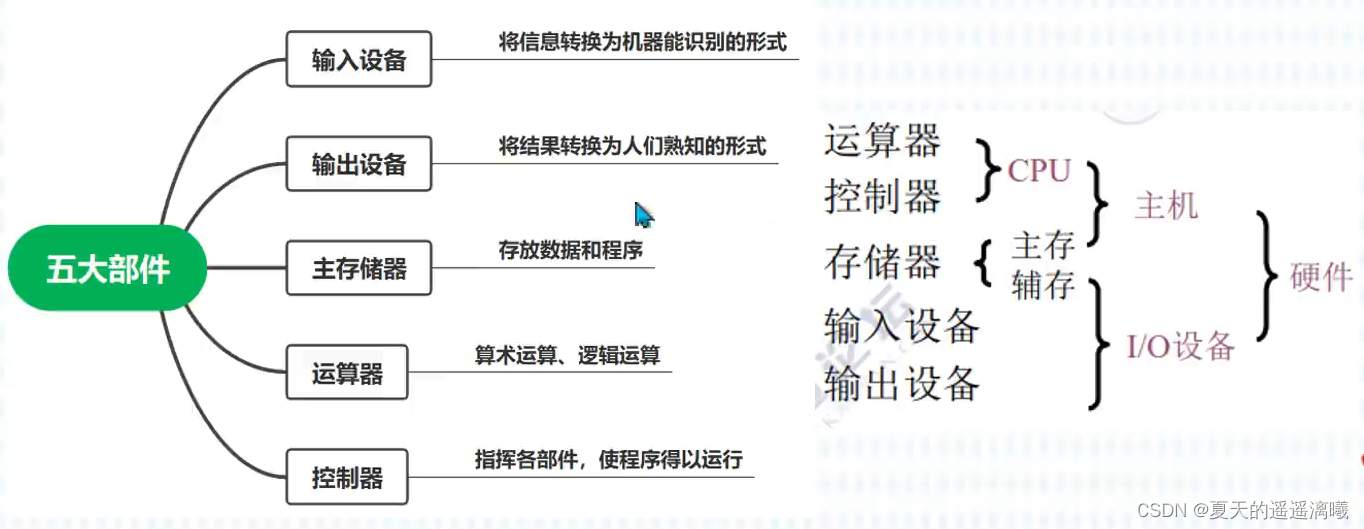

2.1 计算机体系结构——五大部件

- 例如 买手机或平板时 ,6+128G或8+128G等,6/8相当于计算机的主存(主存储器),128G相当于计算机的辅存(辅助存储器)

- 计算机的主机包括两大部件:CPU和内存(主存储器)。而对于声卡、显卡、鼠标键盘这些都是属于外设。

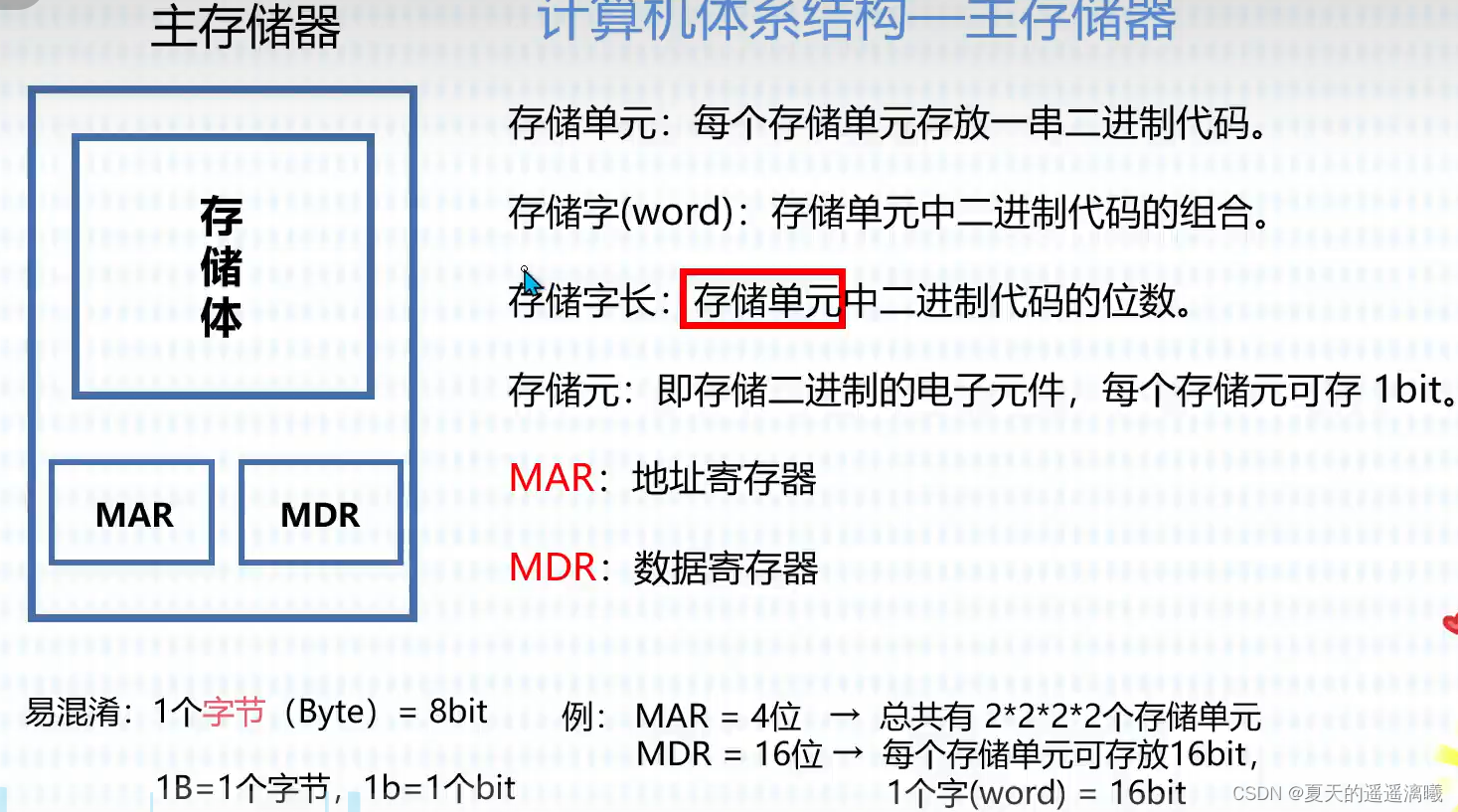

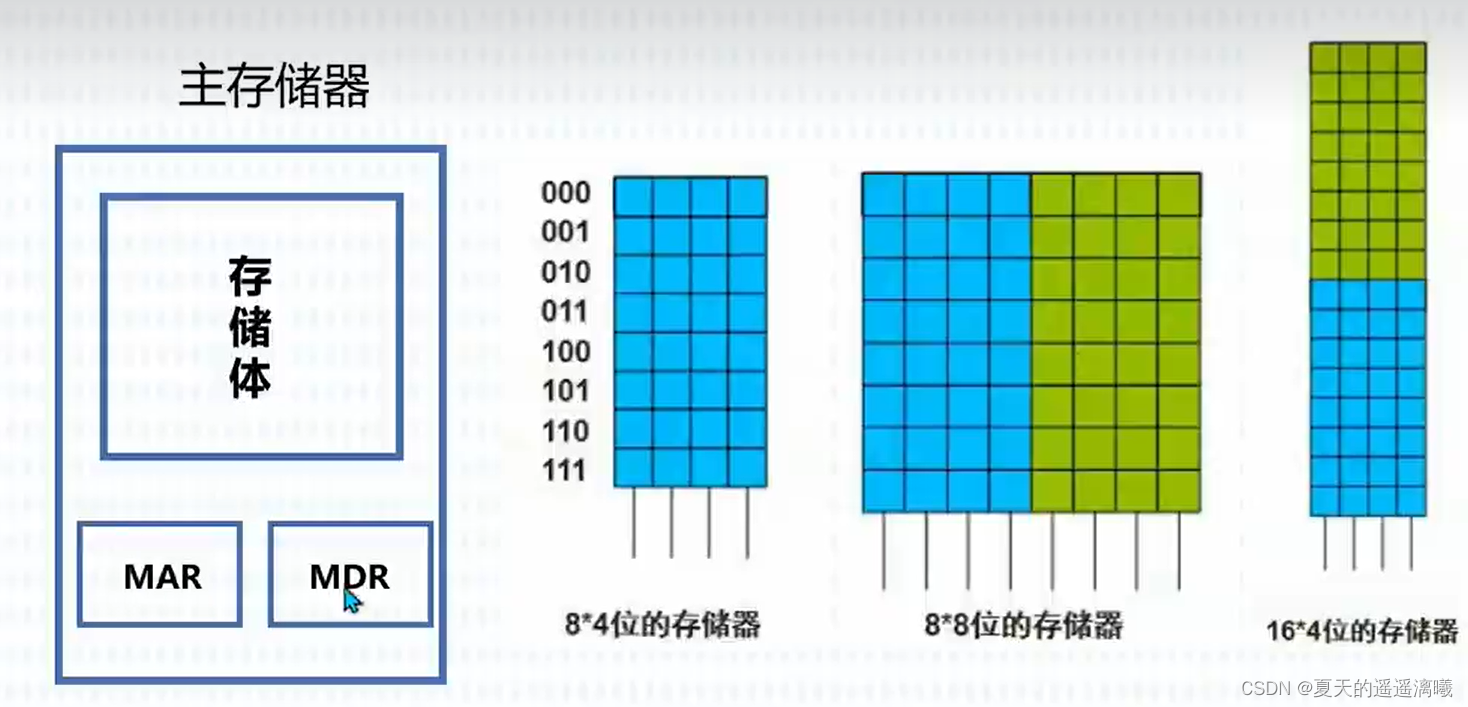

2.2 主存储器

2.3 运算器

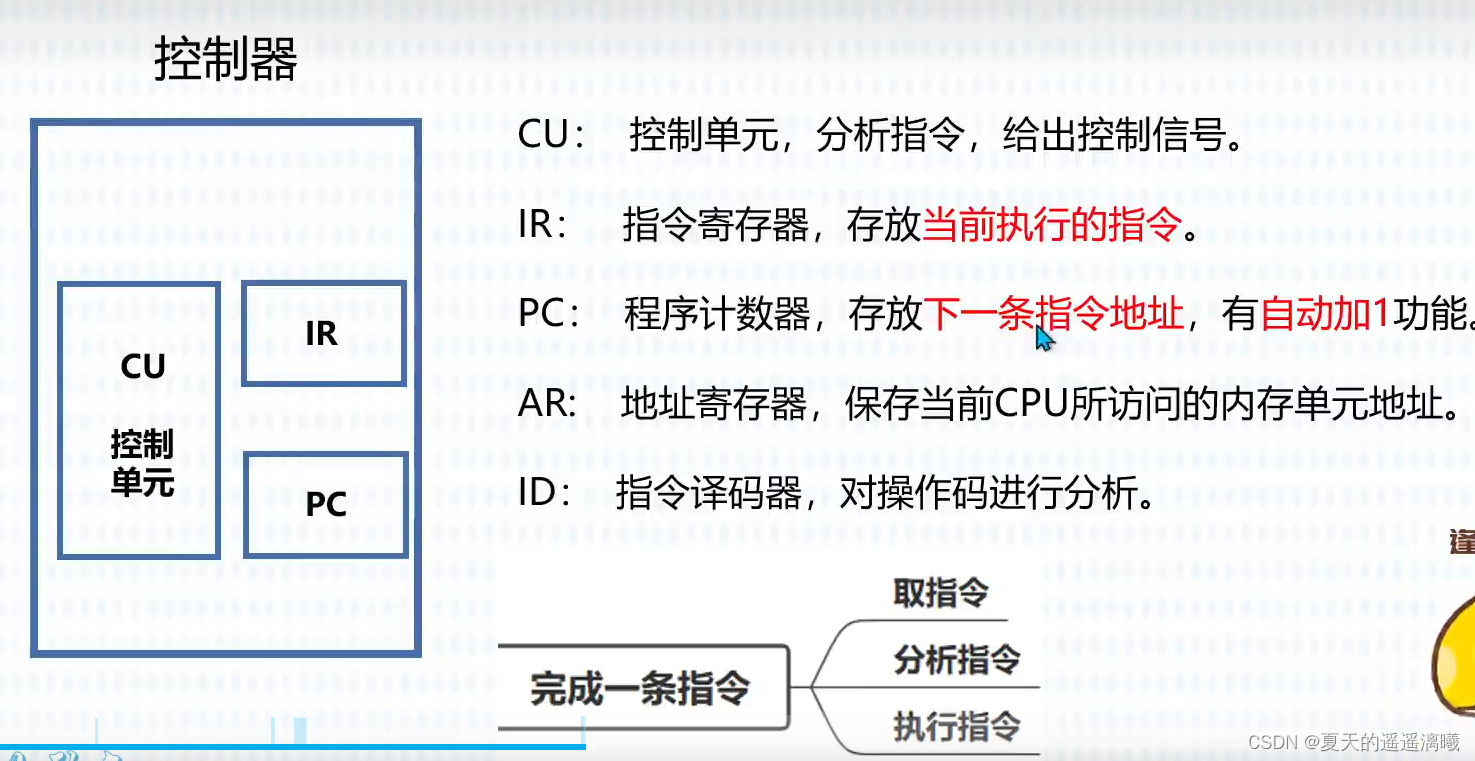

- 助记:ALU 算数 逻辑 单元(arithmetical logic unit)、register(寄存器)、I(instruction)指令、

- 数据缓冲寄存器 DR:作为CPU和内存、外设之间数据传送的中转站,作为CPU和内存、外设之间在操作速度上的缓冲。

2.4 控制器

3. Flynn分类法

- !!! 多指令流单数据流:理论上存在而实际上不存在

- Flynn分类法中主要有两个指标:一个是指令流,一个是数据流。指令流为机器执行的指令序列;数据流是由指令调用的数据序列。无论是指令流还是数据流,它们都分为两种类型:单、多。

4. 指令系统

-

指令

指令(又称机器指令):是指示计算机执行某种操作的命令,是计算机运行的最小功能单位,由二进制表示。

一台计算机的所有指令的集合构成该机的指令系统,也称为指令集。

-

指令格式

一条指令就是机器语言的一个语句,它是一组有意义的二进制代码。

一条指令通常包括操作码字段和地址码字段两部分:

-

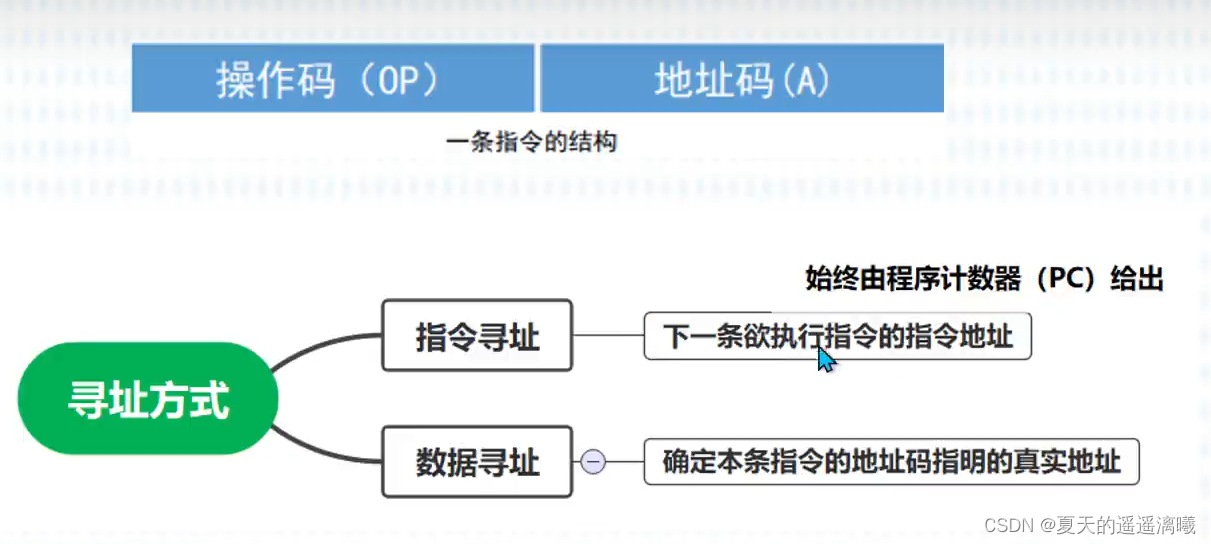

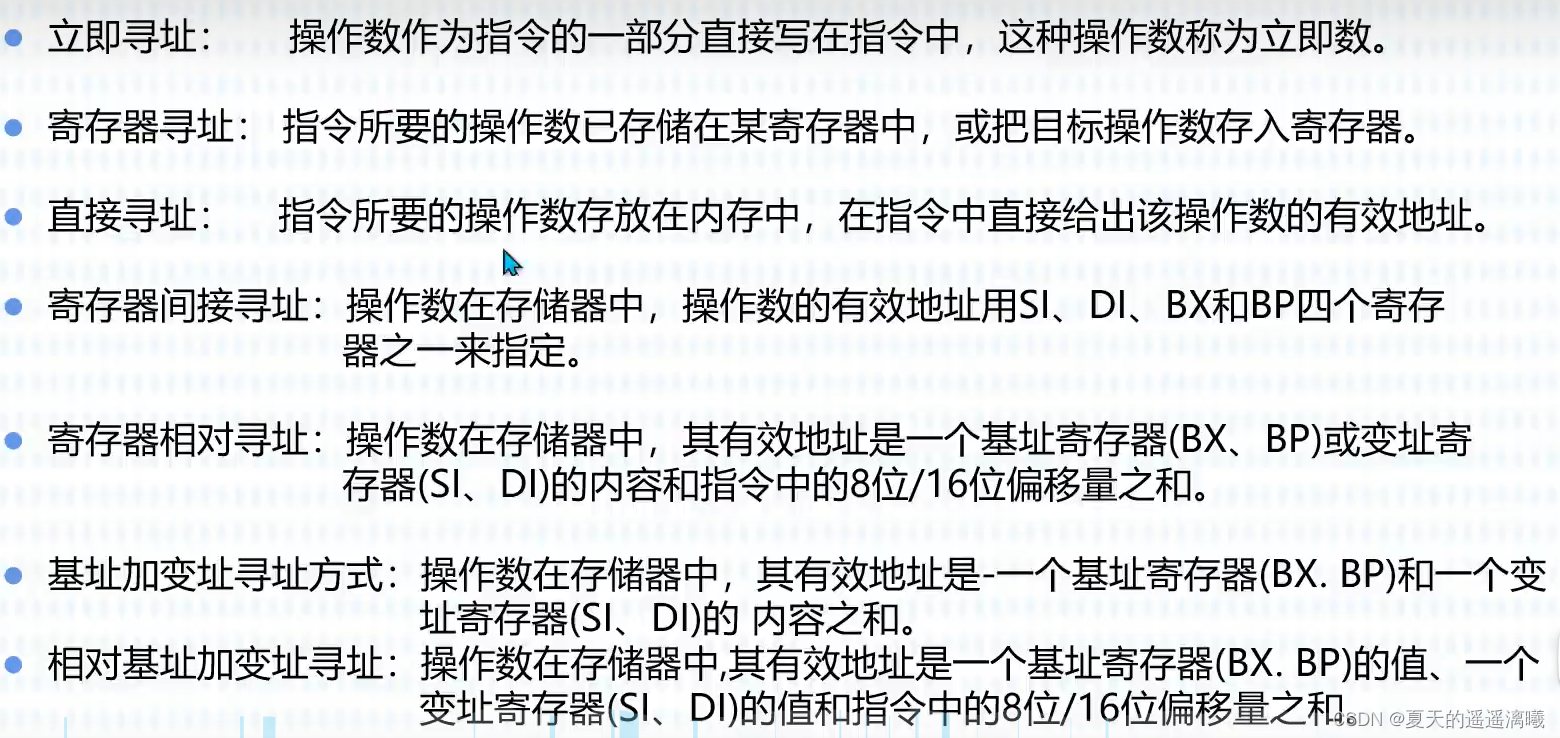

寻址方式 !!

数据寻址:(速度:快->慢)

-

CISC(复杂指令集 计算机)和RISC(精简指令集计算机)

-

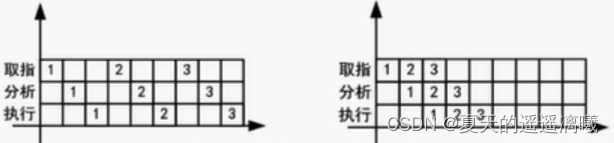

指令的流水处理

指令控制方式有 顺序方式、重叠方式和流水方式。

流水方式:是指并行性或并发性嵌入计算机系统里的一种形式,它把重复的顺序处理过程分解为若干子过程,每个子过程能在专用的独立模块上有效地并发工作。

--> 取指 --> 分析 --> 执行 -->

下图:左图是 未使用流水线执行指令情况; 右图是 使用流水线执行指令情况

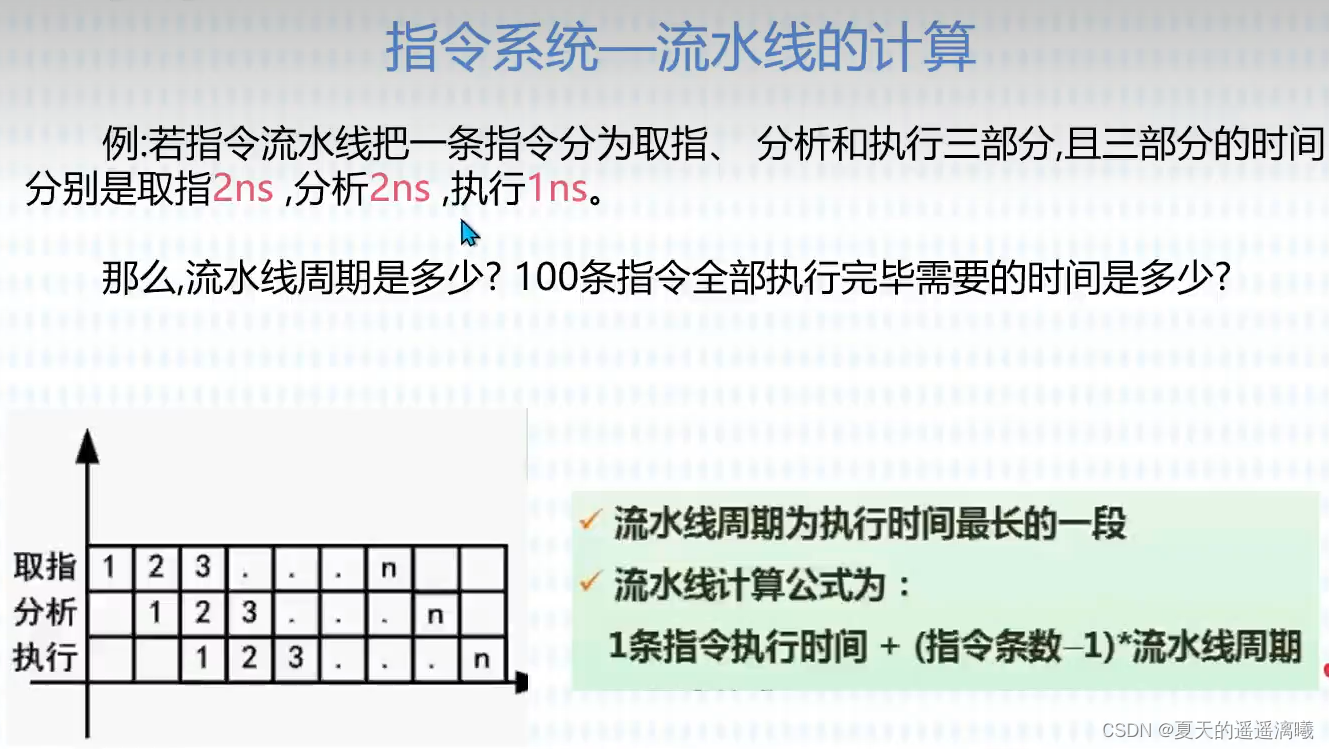

例:1.流水线周期计算,n条指令全部执行完毕所需时间计算

解:

流水线周期: 2ns(纳秒) (注:流水线周期是指在(取指、分析、执行)三个阶段中时间最长的一段)

1条指令执行时间):2ns + 2ns + 1ns = 5ns

100条指令全部执行完毕:5ns + (100 - 1) * 2ns = 203ns

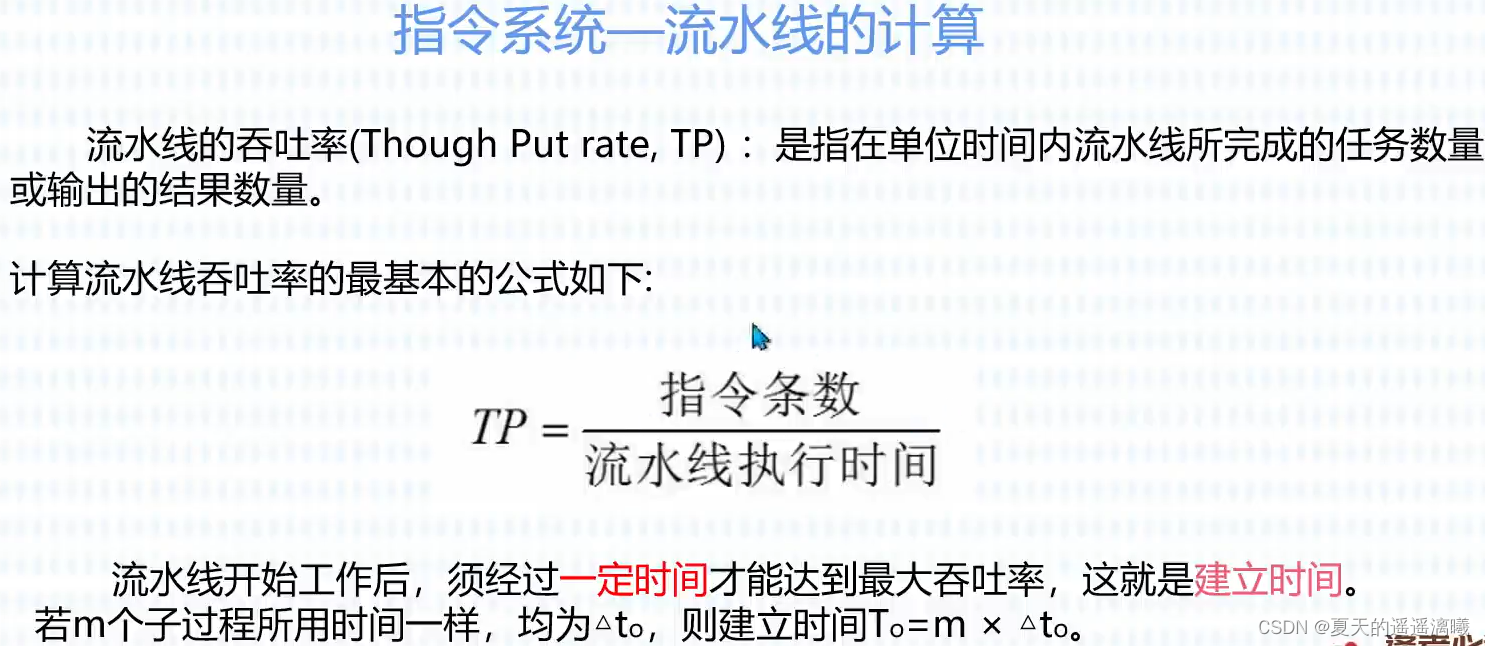

吞吐率:TP = 100 / 203

0.5

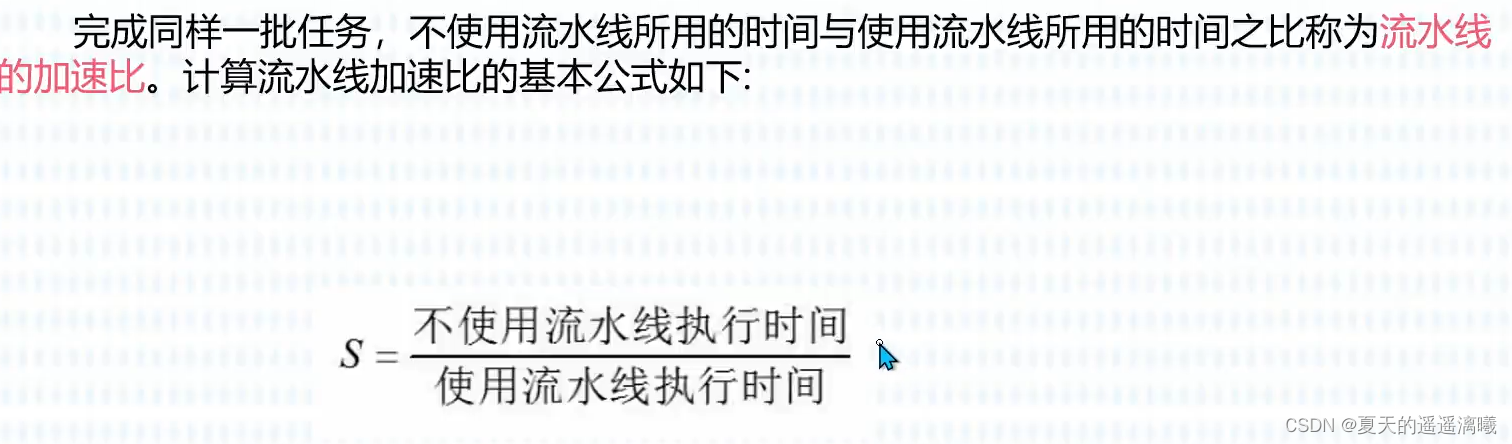

完成100条指令,加速比:S = 5 * 100 / 203 = 2.46 (如果不使用流水线,则采用顺序执行的方法)

例2:吞吐率计算

-

例3 流水线的加速比

5. 存储系统

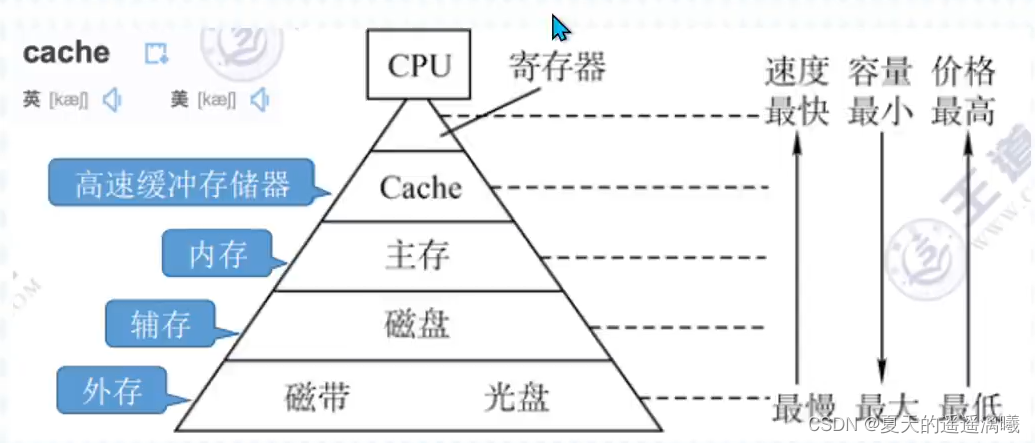

5.1 存储系统的层次结构

- 在上图中,存储速度最快、效率最高的就是寄存器,它位于CPU中,在CPU中,拥有运算器和控制器,而在运算器和控制器中,就会存在相应的寄存器。而寄存器的容量是极小的,但是速度非常快。

主存 — 辅存:实现虚拟存储系统,解决了主存容量不够的问题。

Cache — 主存:解决了主存与CPU速度不匹配的问题。由硬件自动完成

5. 2 存储器的分类

5.2.1 按存储器所处的位置分类:

- 内存(主存):设在主机内或主板上,用来存放机器当前运行所需要的程序和数据,以便向CPU提供信息。相对于外存,其特点是容量小、速度快。

- 外存(辅存):如磁盘、磁带、光盘和U盘等,用来存放当前不参加运行的大量信息,而在需要时调入内存。容量大但速度慢

5.2.2 按材料分类

- 磁存储器:用磁性介质做成,如磁芯、磁泡、磁膜、磁鼓、磁带及磁盘等。

- 半导体存储器:根据所用元件可分为:双极型和MOS型;根据数据是否需要刷新可分为:静态和动态。

- 光存储器:利用光学方法读/写数据的存储器,如光盘

5.2.3 按工作方式分类

- 读/写存储器(RAM):既能读取数据也能存入数据的存储器。

- 只读存储器:工作过程中仅能读取的存储器。

根据数据的写入方式又可细分为:ROM、PROM、EPROM、EEPROM等。

- 固定只读存储器(ROM):这种存储器是在厂家生产时就写好数据的,其内容只能读出,不能改变。一般用于存放系统程序BIOS和用于微程序控制。

- 可编程的只读存储器(PROM):其中的内容可以由用户一次性写入,写入后不能再修改。

- 可擦除可编程的只读存储器(EPROM):其中的内容既可以读出,也可以由用户写入,写入后还可以修改,紫外线照射擦除信息。

- 电擦除可编程的只读存储器(EEPROM):与EPROM相似,既可以读出,也可以写入,只不过这种存储器采用电擦除的方式进行数据的改写。

- 闪速存储器(FM)(Flash Memory):简称闪存,其特性介于EPROM和EEPROM之间,类似于EEPROM,也可使用电信号进行信息的擦除操作。整块闪存可以在数秒内删除,速度远快于EPROM。

5.3 高速缓存Cache

5.3.1 局部性原理

- 空间局部性:在最近的未来要用到的 信息(包括指令和数据),很可能与现在正在使用的信息在存储空间上是临近的。(即:指一旦程序访问了某个存储单元,则在不久的将来,其附近的存储单元也最有可能被访问。)

例如:数组元素、顺序执行的指令代码

- 时间局部性:在最近的未来要用到的信息,很可能是现在正在使用的信息。

例如:循环结构里面的指令代码

- 基于局部性原理,不难想到,可以把CPU目前访问到的地址“周围”的部分数据放到Cache中,以提高访问效率。

- 使用Cahe改善系统性能的依据是程序的局部性原理

- 在计算机的存储体系中, Cache是访问速度最快的层次。

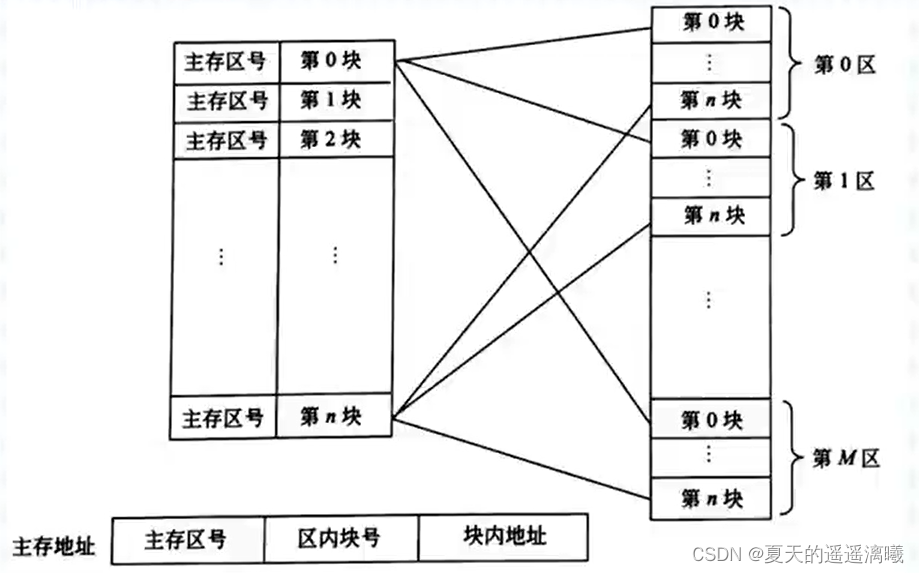

5.3.2 高速缓存中的地址映像方法

要把主存中的地址映射为Cache存储器里面的地址,地址映像方法有三种:

- 直接映像:指主存的块与Cache块的对应关系是固定的。优点是地址变换简单,缺点是灵活性差、Cache块冲突率高。

- 全相联映像:允许主存的任一块可以调入Cache存储器的任何一个块的空间中。优点是Cache的位置不受限制,十分灵活,缺点是无法从主存块号中直接获得Cache的块号,访问速度慢、地址变换较复杂、成本太高。

- 组相联映像:是前两种方式的折衷方案,具体方法是将Cache先分成组再分成块。即组间采用直接映像方式、组内的块采用全相联映像方式。

5.3.3 替换算法

选择替换算法的目标是使Cache获得最高的命中率。常用的替换算法有以下几种:

- 随机替换(RAND)算法:用随机数发生器产生一个要替换的块号,将该块替换出去。

- 先进先出(FIFO)算法:将最先进入的Cache信息块替换出去。

- 近期最少使用(LRU)算法:将近期最少使用的Cache中的信息块替换出去。这种算法较先进先出算法要好些,但此法也不能保证过去不常用的将来也不常用。

- 优化替换(OPT)算法:先执行一次程序,统计Cache的替换情况。有了这样的先验信息,在第二次执行该程序时便可以用最有效的方式来替换,达到最有目的。

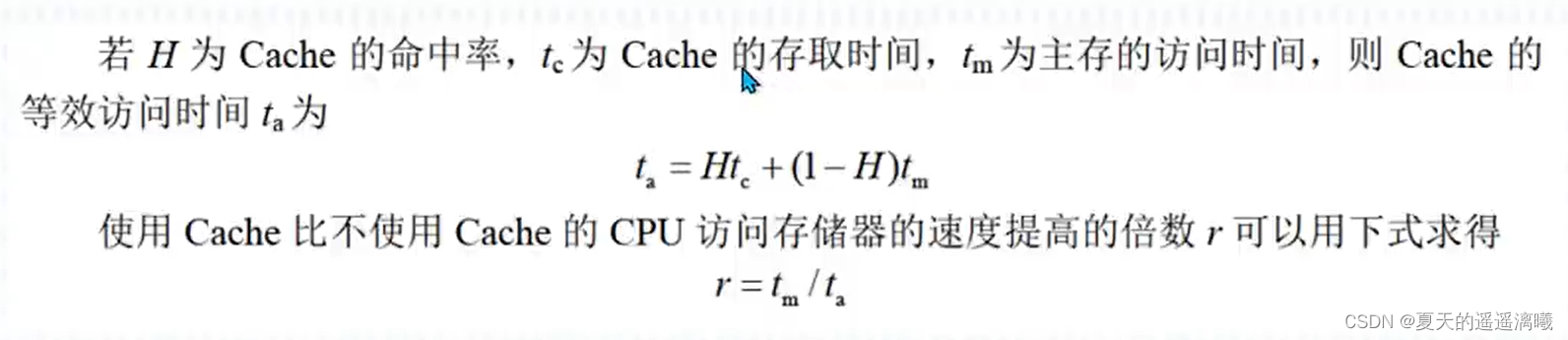

5.3.4 Cache的性能分析

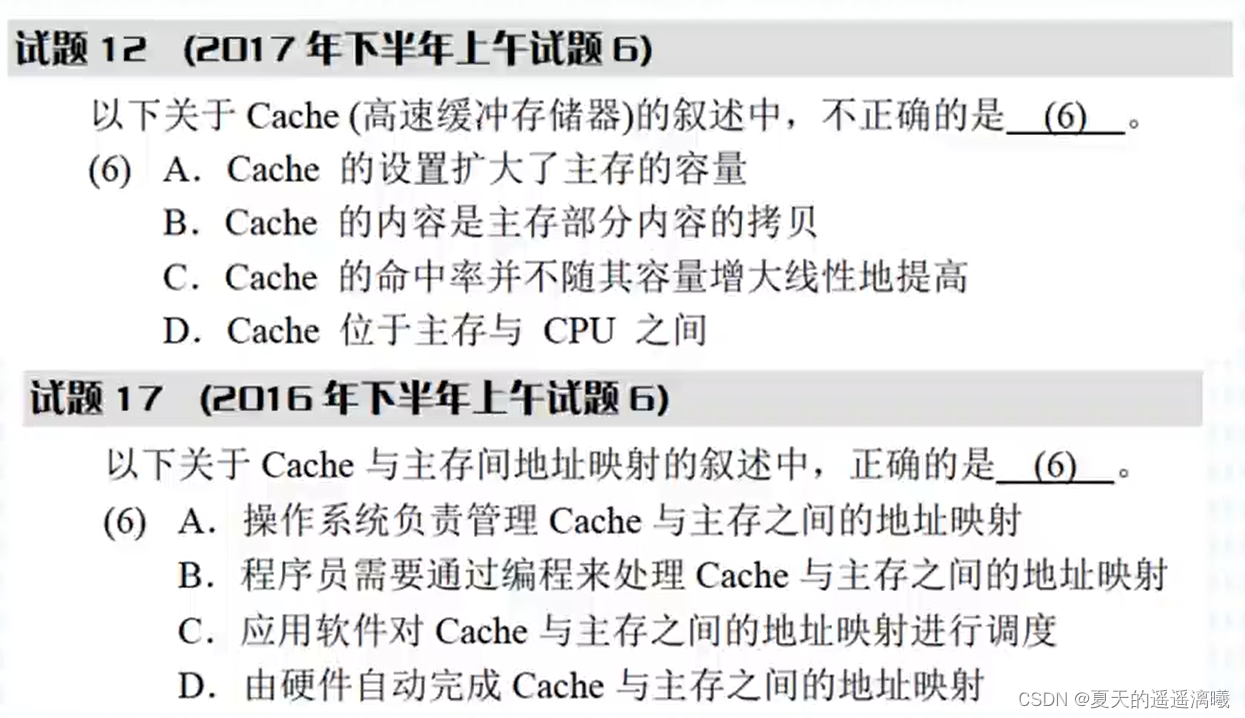

试题12:A

A:Cache中的内容也是主存中有的,并没有“扩大”

试题17:D

A、B:Cache和主存之间是由计算机硬件完成的,并不是操作系统,也不是通过编程

试题19:A

Cache总结:

- Cache位于CPU和主存之间由硬件来实现,容量小,速度比主存块5~10倍,由快速地半导体存储器制成,是主存的副本,无法扩充主存的容量。

5.4 主存

5.4.1 主存的编址

解:

K =

, M =

, G =

第(1)问:B

内存地址从AC000H到C7FFFH(两个十六进制数进行加减,再加1),C7FFFH-AC000H = 1BFFFH(因为十六进制,所以每借一位加16),再加1,得1C000H,(将其转换成K单位,要对结果除以1024)。将其转为十进制:(0×

+ 0×

+ 0×

+ C×

+ 1×

)/1024=112K。

第(2)问:A

总容量为112K×16bit,该芯片每个存储单元存储位数:(112K x 16bit) / (28 x 16K) = 4bit

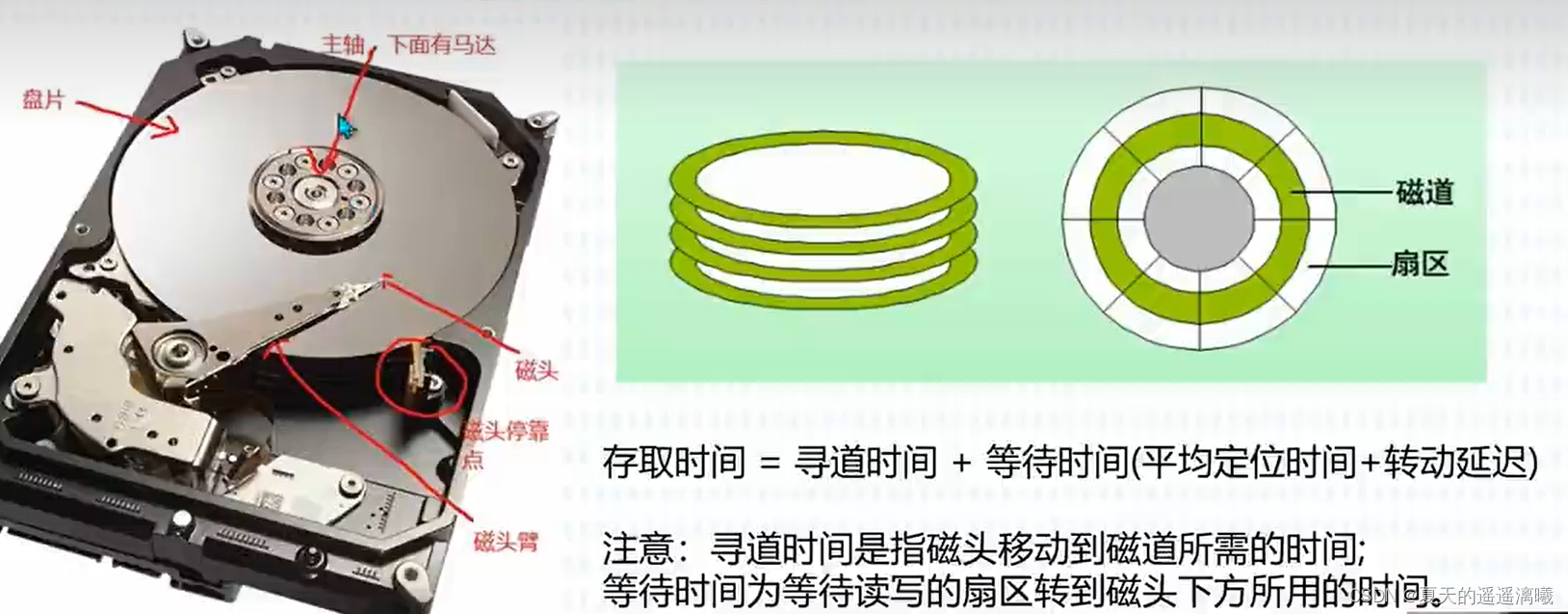

5.5 硬盘(磁盘)(了解公式即可)

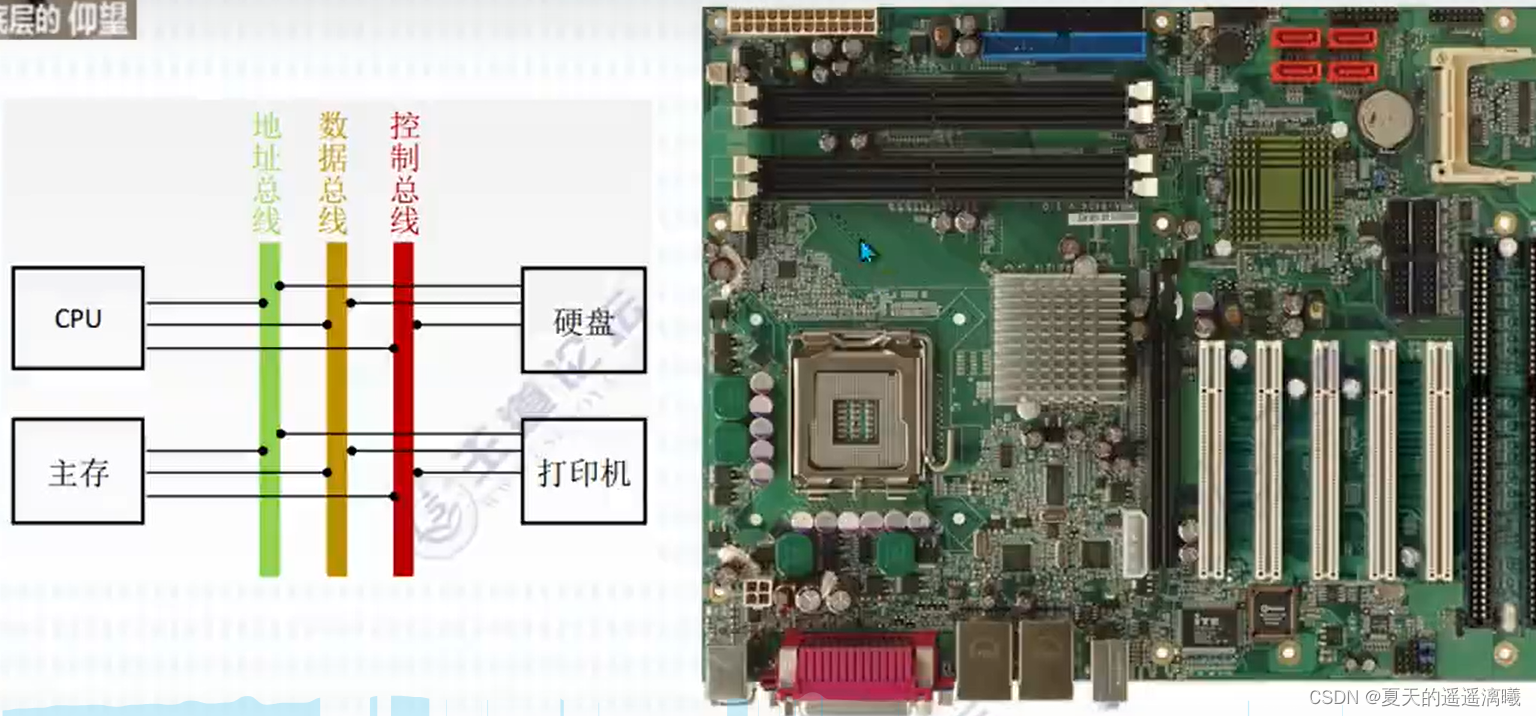

5.6 总线系统

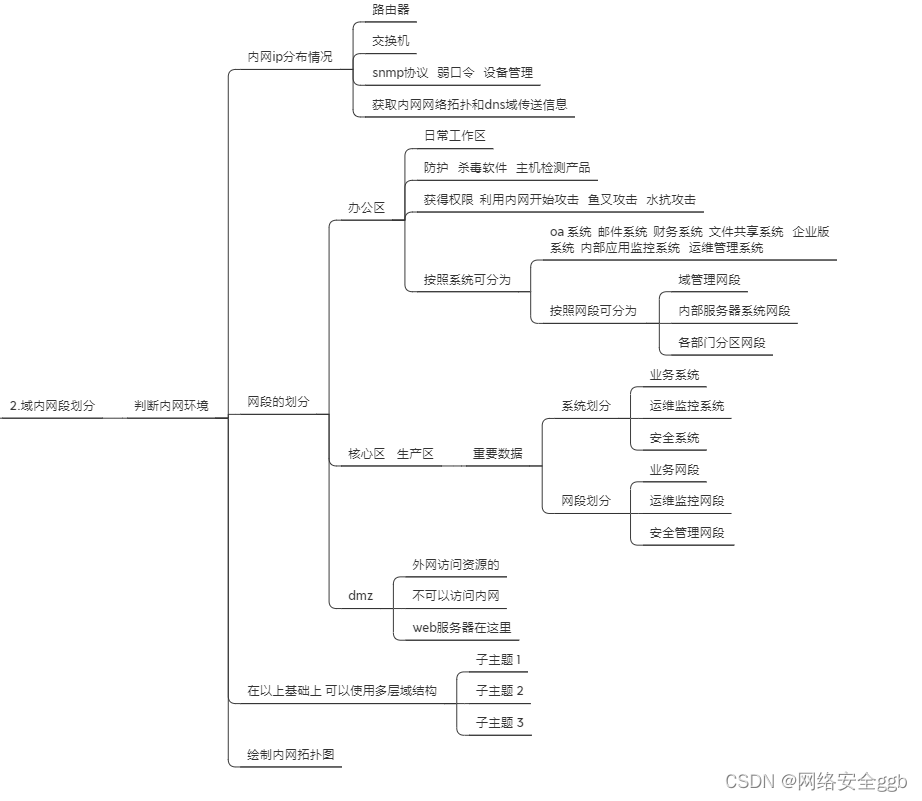

根据总线所处位置不同,分为三种类型:

- 片内总线:是芯片内部的总线。它是CPU芯片内部寄存器和寄存器之间、寄存器与ALU之间的公共连接线。

- 系统总线:是计算机系统内各功能部件(CPU、主存、I/O接口)之间相互连接的总线。按系统总线传输信息内容的不同,又分为3类:数据总线、地址总线和控制总线。

- 通信总线

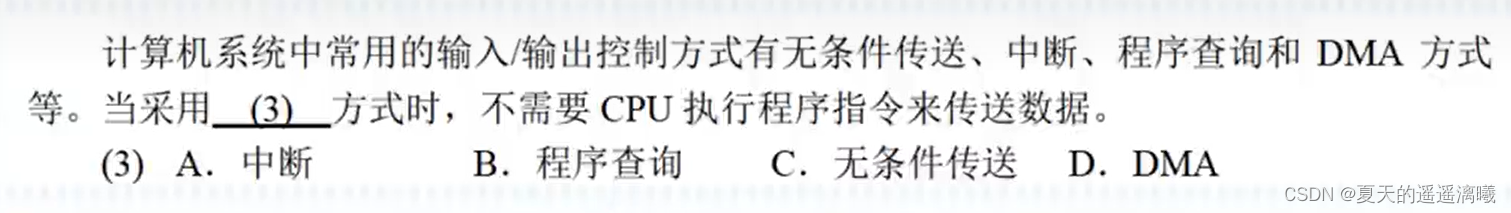

6.输入输出技术

CPU与外设之间的数据传送方式:

6.1 直接程序控制方式

直接程序控制是指外设数据的输入/输出过程是在CPU执行程序的控制下完成的。这种方法分为:无条件传送和程序查询方式两种情况。

- 无条件传送方式:(无条件地与CPU交换数据)在此情况下,外设总是准备好的,它可以无条件的随时接收CPU发来的输出数据,也能够无条件的随时向CPU提供需要输入的数据。

- 程序查询方式:(先通过CPU查询外设状态,准备好之后再与CPU交换数据)在这种方式下,利用查询方式进行输入/输出,就是通过CPU执行程序来查询外设的状态,判断外设是否准备好接收数据或准备好了向CPU输入的数据

6.2 中断方式

对于程序控制I/O的方法,其主要的缺点:CPU必须等待I/O系统完成数据的传输任务,整个系统的性能严重下降。

利用中断方式完成数据的输入/输出过程为:当I/O系统与外设交换数据时,CPU无需等待也不必去查询I/O的状态,而可以抽身出来处理其他任务。当I/O系统准备好了以后,则发出中断请求信号通知CPU,CPU接到中断请求信号后,保存正在执行程序的现场,转入I/O中断服务程序的执行,完成与I/O系统的数据交换,然后再返回被中断的程序继续执行。

与程序控制方式相比,中断方式因为CPU无需等待而提高了效率。

6.3 直接存储器存取方式(DMA)!!!

直接存储器存取(Direct Memory Access, DMA)方式是在存储器与I/O设备间直接传送数据,即在内存和I/O设备之间传送一个数据块的过程中,不需要CPU的任何干涉,是一种完全由DMA硬件完成I/O操作的方式。

D

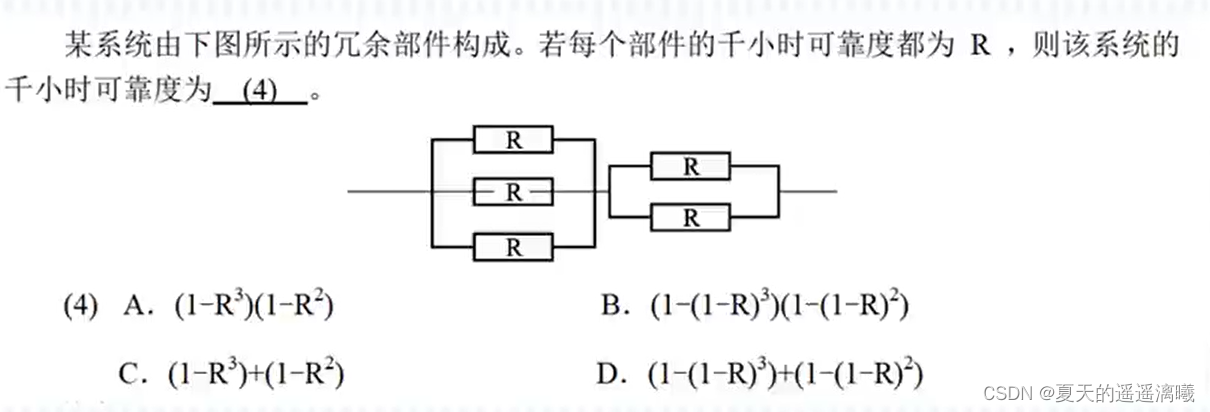

7.计算机系统的可靠性

计算机系统的可靠性是指从它开始运行(t=0)到某个时刻t这段时间内能正常运行的概率,

用R(t) 表示

- 串联部件的可靠度 = 各部件的可靠度的乘积

- 并联部件的可靠度 = 1 - 部件失效率的乘积 (失效率 = 1 - 可靠度)

首先是3个R的并联,接着是2个R的并联,最后是串联。

选B