参考(照抄+自己加点):

ZYNQ PS-PL数据交互方式总结(好文)_axi emc-CSDN博客

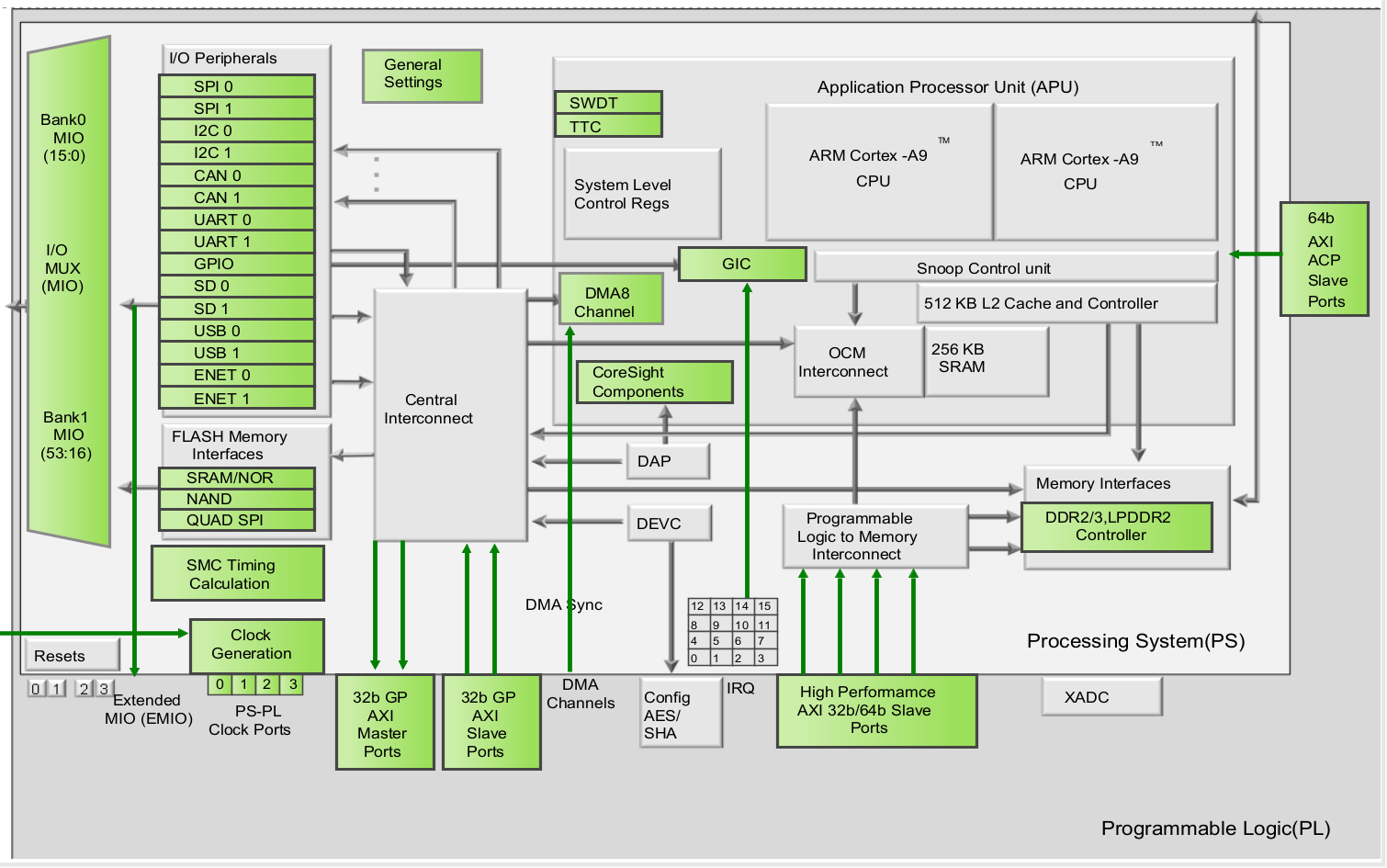

zynq_process是一个用于方便操作PS和PL通信的GUI。 MIO分配在bank0和bank1直接与PS部分相连,EMIO分配在bank2直接和PL部分相连。除了bank1是22-bit之外,其他的bank都是32-bit。所以MIO有53个引脚可供我们使用,而EMIO有64个引脚可供我们使用。

MIO分配在bank0和bank1直接与PS部分相连,EMIO分配在bank2直接和PL部分相连。除了bank1是22-bit之外,其他的bank都是32-bit。所以MIO有53个引脚可供我们使用,而EMIO有64个引脚可供我们使用。

使用EMIO的好处就,当MIO不够用时,PS可以通过驱动EMIO控制PL部分的引脚,接下来就来详细介绍下EMIO的使用。

EMIO的使用和MIO的使用其实是非常相似的。区别在于,EMIO的使用相当于,是一个PS + PL的结合使用的例子。所以,EMIO需要分配引脚,以及编译综合生成bit文件。

MIO与EMIO概念

MIO:多功能IO接口,属于Zynq的PS部分,在芯片外部有54个引脚。这些引脚可以用在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能。

EMIO:扩展MIO,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯片外面实现数据输入输出。

PS 和外部设备之间的连接主要是通过复用的输入/输出(Multiplexed Input/Output,MIO)来实现的。 PS的54个MIO引脚可以用于连接不同的外设接口,如图 1.3.13中的MIO14和MIO15,既可以配置成UART0 的引脚接口,也可以配置成 I2C0 或 CAN0 的引脚接口。最终所选择的配置需要与开发板的原理图相 对应。

zynq_process预设配置:

PS复位一个,GP0配置一个,输出时钟一个。

编辑好硬件设备以后~:

参考:

Vivado IP核Global 和 out of context per IP两种综合方式区别-CSDN博客

在用vivado 生成IP核时,有两种综合方式:Global和out of context per IP。Global模式可以理解为全局综合,当整个工程中的某个文件修改综合时,之前生成的IP核将被重新综合,而out of context per IP模式被称为OOC模式,在生成综合IP核时,已经将IP核综合为网表文件和IP调用文件,在后续整个工程实现时,不再对IP核的源文件进行综合实现,而是直接将网表与其他模块一起实现。个人理解有些像软件工程编译时的增量编译,因此IP采用OOC模式可以大大解决整个工程的综合时间,毕竟FPGA目前的综合时间还是太漫长了。

我的话:Global模式在自己写IP加入BD设计的时候用,因为对接的时候Global相比out of context per IP不会自行优化,不会自动删去接口。

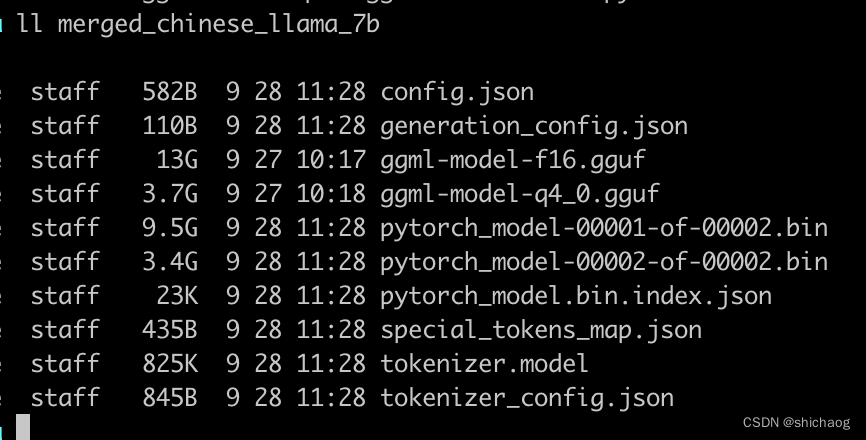

生成的文件:

Create a HDL wrapper-生成HDL顶层文件

Xilinx Bit文件格式详解-腾讯云开发者社区-腾讯云 (tencent.com)

FPGA中可执行文件:bit/bin/mcs/elf-腾讯云开发者社区-腾讯云 (tencent.com)

XSA文件和HDF文件:

hdf: Hardware Description File,Vivado 2019.1及更早版本导出的硬件描述文件,给xilinx sdk使用。(在 Export Hardware 的过程中,工具会将硬件以一个 ZIP 压缩文件的形式导出到该工作空间中。该文件包含了我们前面所搭建的硬件平台的配置信息,其后缀名.hdf 的含义为 ―Hardware Definition File‖,即硬件定义文件)

xsa: Xilinx Shell Archive,Vivado 2019.2及后续版本导出的硬件文件,.xsa=.bit+hdf.

vitis与SDK

Vitis平台使用从这六点变化开始 (e-elements.com)

Vitis的使用 - 简书 (jianshu.com)

![[React] Context上下文的使用](https://img-blog.csdnimg.cn/36e2bbade74240c9b425807ec1d78dc8.png)