名称:2FSK调制解调VHDL(代码在文末付费下载)

软件:Quartus

语言:VHDL

要求:使用VHDL实现2FSK的调制和解调,并进行仿真

代码下载:2FSK调制解调VHDL,Quartus_Verilog/VHDL资源下载

代码网:hdlcode.com

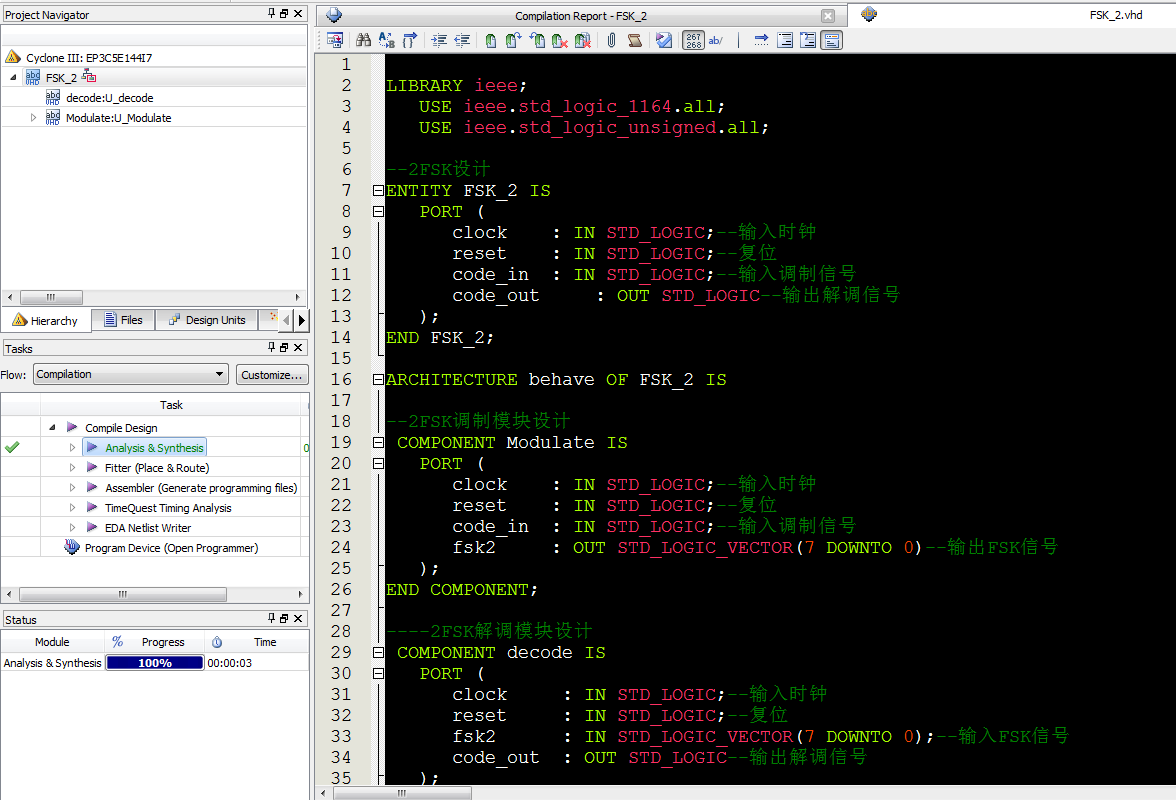

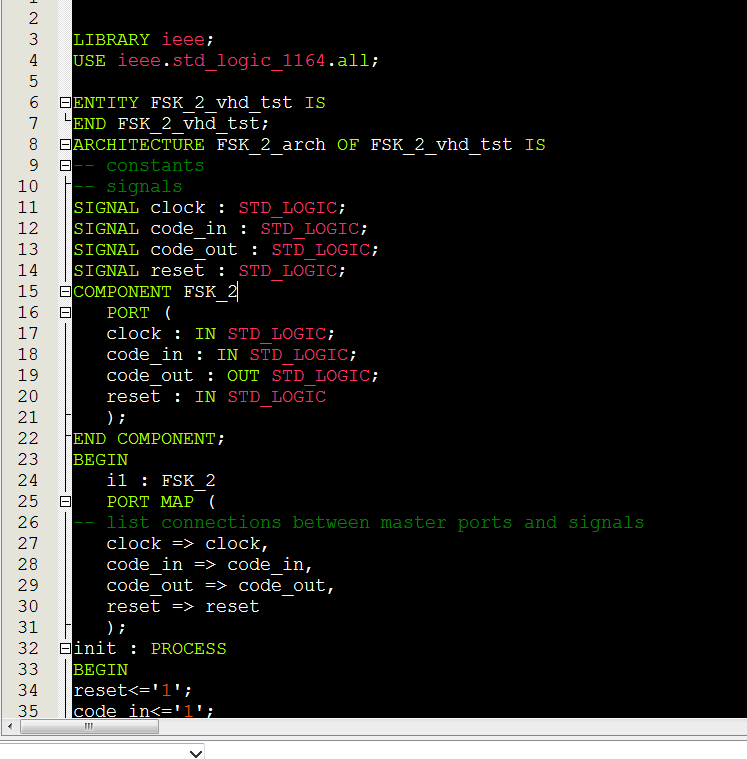

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --2FSK设计 ENTITY FSK_2 IS PORT ( clock : IN STD_LOGIC;--输入时钟 reset : IN STD_LOGIC;--复位 code_in : IN STD_LOGIC;--输入调制信号 code_out : OUT STD_LOGIC--输出解调信号 ); END FSK_2; ARCHITECTURE behave OF FSK_2 IS --2FSK调制模块设计 COMPONENT Modulate IS PORT ( clock : IN STD_LOGIC;--输入时钟 reset : IN STD_LOGIC;--复位 code_in : IN STD_LOGIC;--输入调制信号 fsk2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--输出FSK信号 ); END COMPONENT; ----2FSK解调模块设计 COMPONENT decode IS PORT ( clock : IN STD_LOGIC;--输入时钟 reset : IN STD_LOGIC;--复位 fsk2 : IN STD_LOGIC_VECTOR(7 DOWNTO 0);--输入FSK信号 code_out : OUT STD_LOGIC--输出解调信号 ); END COMPONENT; SIGNAL fsk2 : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000";--FSK信号 BEGIN --例化调制模块 U_Modulate : Modulate PORT MAP ( clock => clock, reset => reset, code_in => code_in,--输入调制信号 fsk2 => fsk2--输出FSK信号 ); --例化解调模块 U_decode : decode PORT MAP ( clock => clock, reset => reset, code_out => code_out,--输出解调信号 fsk2 => fsk2--输入FSK信号 ); END behave;

设计文档(文档点击可下载):

1.

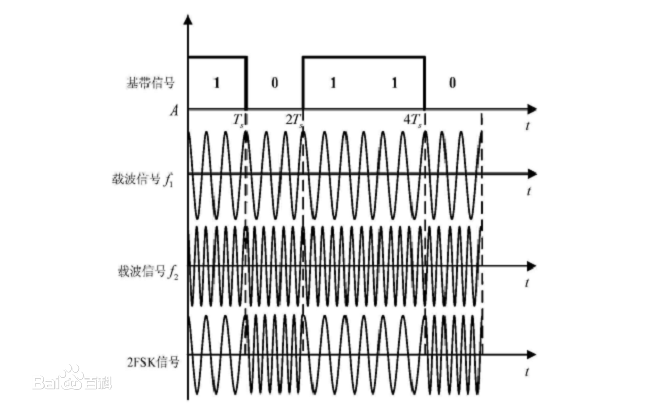

2FSK(Frequency Shift Keying)为二进制数字频率调制(二进制频移键控),用载波的频率来传送数字信息,即用所传送的数字信息控制载波的频率。2FSK信号便是符号“0”对应于载频 f1,而符号“1”对应于载频 f2(与 f1 不同的另一载频)的已调波形,而且 f1 与 f2 之间的改变是瞬间的。传“0”信号时,发送频率为 f1 的载波; 传“1”信号时,发送频率为 f2的载波。

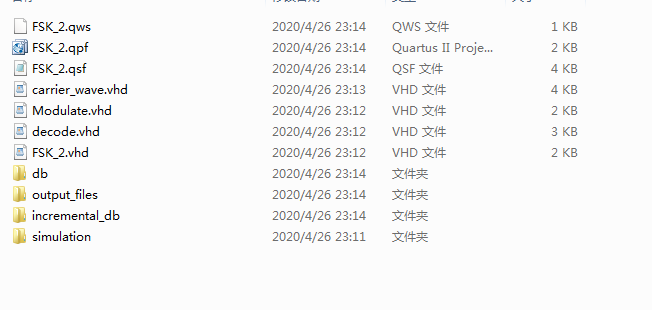

2. 工程文件

3. 程序文件

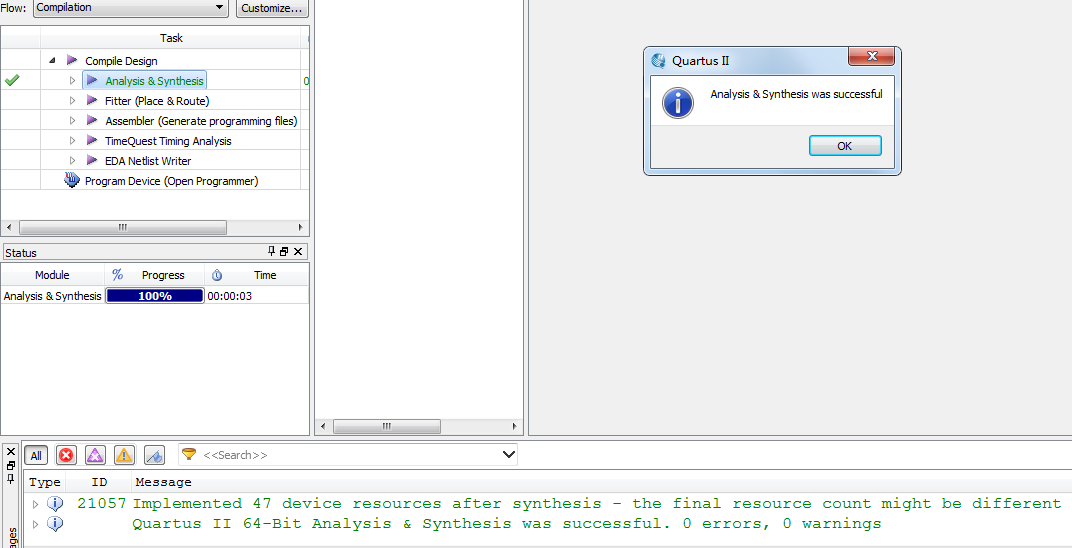

4. 程序编译

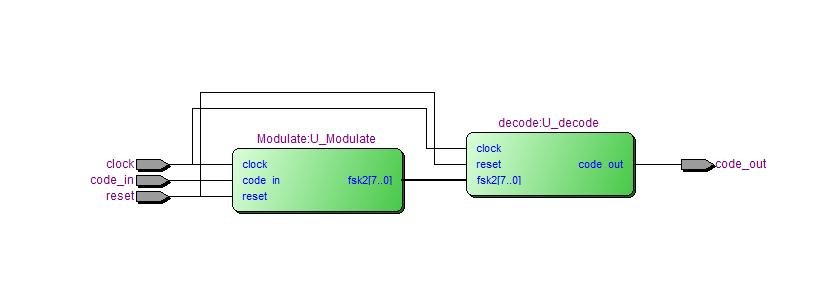

5. RTL图

6. testbench

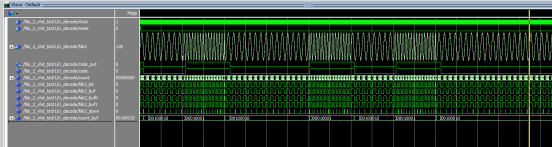

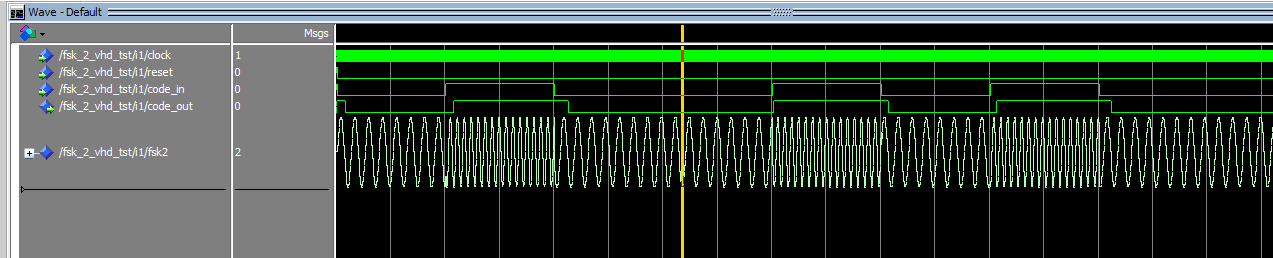

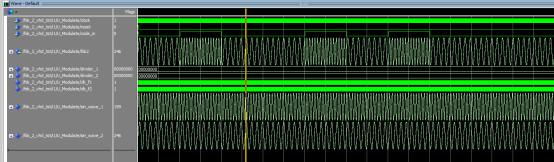

7. 仿真图

Code_in为输入调制信号,fsk2为2FSK信号。Code_out为解调信号,可以看到与调制信号波形一致

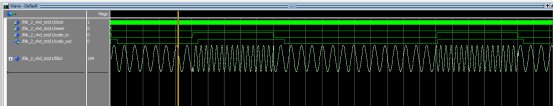

调制模块仿真

解调模块